本文主要是介绍Verilog HDL高级数字设计 从零学习(二),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Verilog HDL高级数字设计 从零学习(二)

- 4.1 Verilog原语和设计封装

- 4.2.1 Verilog中的四值逻辑

- 4.2.2 测试方法

- 4.3 传播延时

🔈声明:

🔑未经作者允许,禁止转载

🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈

刚看完了第四章的内容,在此记录一下。

整个第四章主要是介绍了一些RTL级的设计思想和设计流程,没有过多的技巧性的内容。

通常设计需要先完成HDL模型的设计,并综合成物理电路,然后进行功能,时序和故障覆盖的验证。

- 设计流程:

- 1) 编写文本形式的的电路或模型描述 (Verilog代码编写)

- 2) 编译这些描述,以验证它的语法正确性。

- 3) 对模型及其设计功能进行仿真验证。(RTL级功能验证)

电路的Verilog模型将每个模块描述封装成输入——输出关系的结构或行为描述形式。

结构描述形式可以是门级网表,也可能是主要功能模块描述如ALU。

行为描述形式可能是一个简单的布尔方程模型,寄存器传输模型,或者某种算法。

4.1 Verilog原语和设计封装

原语:Verilog包括常见组合逻辑门的26个预定义功能模型,是构成设计的最基本功能单元。(没有预定义时序原语)

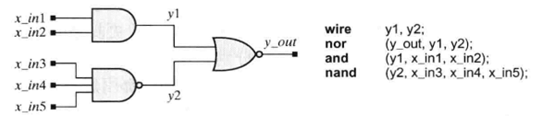

- 以一个基本的五输入的门电路来对原语的用法进行举例

自顶而下设计思想(Top-down):就是将一个大的工程或模块拆分成更为细小的模块,这样只要完成每个小模块的编写和测试,再进行拼接就能实现复杂的工程,是现在的主流思想。

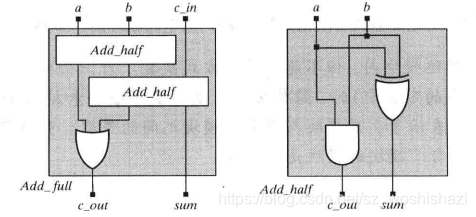

- 以一个16位行波进位加法器为例来ji(个人认为就是串行的加法,来完成一个多位数据加法)

- 这是一个16位的行波加法器,完成16位的加法。输入A,B,C_in,输出C_out。

- 把16位的行波加法器可以拆分为4个4位的行波加法器。

- 又可以将一个4位的行波加法器拆分成4个串行的全加器的组合。

- 每个全加器可由两个半加器构成,一个半加器的门电路如下。用Verilog可以直接用原语来完成。

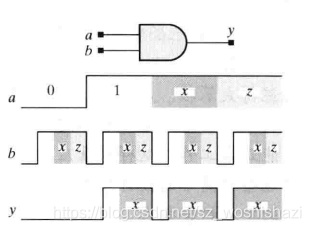

4.2.1 Verilog中的四值逻辑

0值和1值对应于信号的有效或无效状态。X表示不定状态,例如当一个线网被两个具有相反输出值的基本门驱动时,就会出现这种情况。

Z表示三态情形,表示连接线不与驱动相连接。

- 从下图可知当输入出现x或z时输出都为x。

4.2.2 测试方法

关键词initial定义了开始运行的简单行为,与这种行为有关的语句列在begin……end之间,称为过程语句。begin……end之内的程序赋值语句执行的时序,取决于它在语句列表中的顺序和执行该语句的延时时间。

在Verilog中,所有线网在仿真开始时都被赋值为z,并在之后被激励单元赋值,没有驱动的线网型继续保持Z。同样,reg型一开始为x。

4.3 传播延时

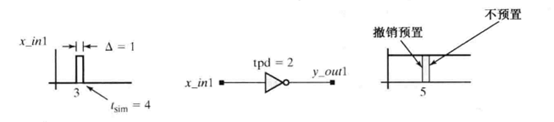

- 从输入信号通过逻辑门到输出信号,会有传播延时,而Verilog中的基本门原语被默认时零延时。

惯性延时:信号变化的物理行为是有惯性的,因为每个传导路径都具有一定的电容性和电阻性,电荷无法在一瞬间积累或消散。

传输延时: 信号流经电路导线所用的时间

例如:一个NAND的所有输入都长时间地保持为1,这时突然有一个输入端变为0,那么输出不会马上变成1,除非输入端保持0输入足够长时间。(这个可能就是hold-time的原因?)

- 在t=3时输入一个持续1个单位的脉冲。由于反向器传播延时为2,在t=4时脉冲就消失了,仿真器没有检测到后沿的事件,所以将事件直接撤销了。

这篇关于Verilog HDL高级数字设计 从零学习(二)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!