表决器专题

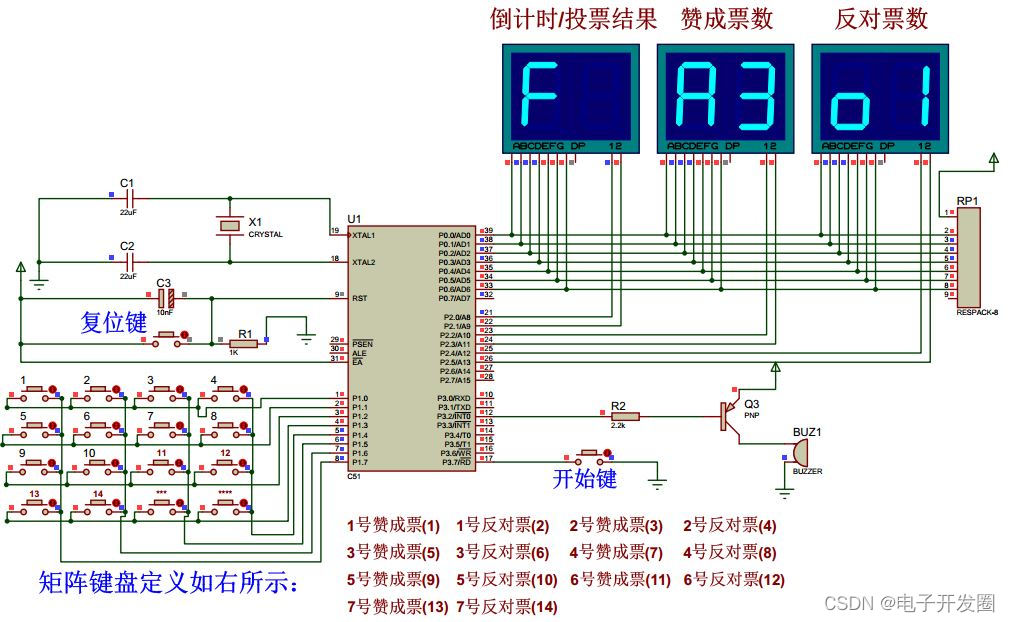

0496-基于单片机的表决器(七人)系统设计

功能描述 1、采用51单片机作为主控芯片; 2、采用矩阵按键,每人两个按键,分别代表同意和反对; 3、按下"开始键"后,进入10秒倒计时,超时投票无效; 4、采用数码管显示:倒计时、表决结果、表决票数; 5、表决结果:"P"表示通过、"F"表示不通过,倒计时结束显示; 6、表决票数:"A"显示同意票数,"o"显示不同意票数,投票过程实时显示; 7、表决开始和结束,采用蜂鸣器声音提示; 8、按下"

Multisim14.0仿真(四十二)基于74LS183的8位表决器设计

一、74LS183简介: 74LS183是一种4位高速全加器,用于数字电路中的加法运算。74LS183输入端包括两个4位二进制数和一个进位信号,输出端包括1个4位二进制数和一个进位信号。 74LS138具有快速响应、低功耗灯特点,能实现高校的数字匀速。 二、74LS183引脚定义: 三、74LS183功能表: 四、74LS183逻辑图: 五、

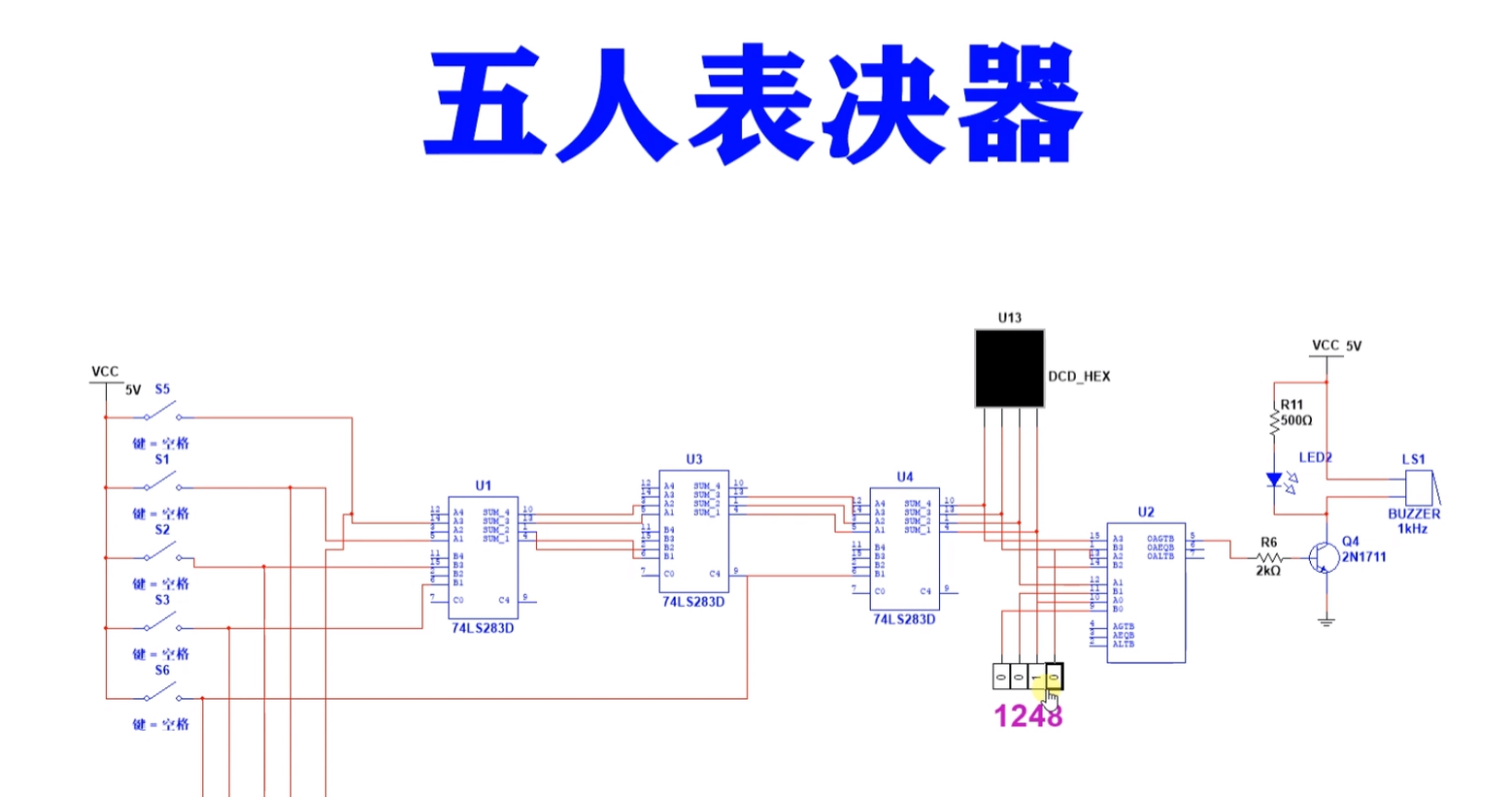

五人表决器基于Multisim仿真Multisim仿真

仿真图: 功能简介: 5个开关模拟5位投票人 通过电位控制可以设置时间通过票数 一旦投票人大于该数,LED和蜂鸣器即工作 芯片介绍 74LS283芯片的特点如下: 四位二进制全加器:74LS283是一个四位二进制全加器,可以执行四位二进制数的加法运算。并行输入输出:该器件具有四个并行输入(A0-A3, B0-B3)和一个四位并行输出(S0-S3),使其能够同时对多个位进行操作。进位和

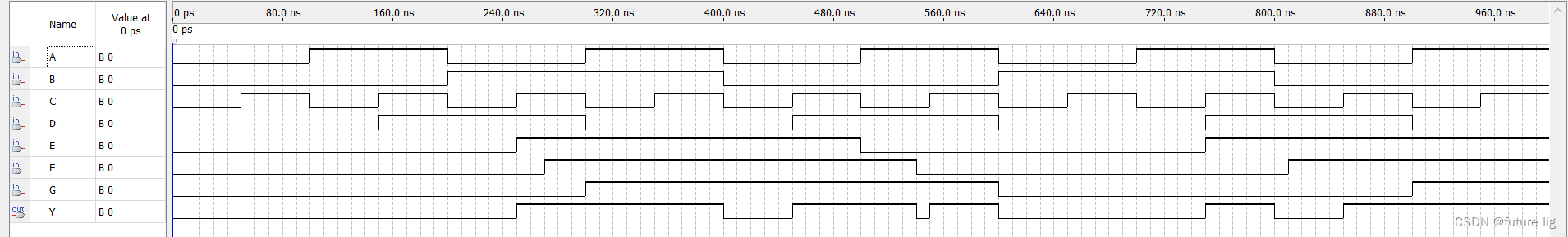

Verilog HDL表决器电路设计

一、电路基本原理 1.电路是多输入,单输出组合逻辑电路 2.输出根据输入比较关系,确定为0或1 3.输入为奇数 二、Verilog代码实现(下面以七人表决器设计为例子) 代码实现: module biaojueqi(A,B,C,D,E,F,G,Y);//注意工程名,根据自己工程名而定input A,B,C,D,E,F,G;output reg Y;always @(A or