本文主要是介绍Vivado Design Suite一级物件,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Vivado Design Suite一级物件

按设计过程导航内容

Xilinx®文档围绕一组标准设计流程进行组织,以帮助您

查找当前开发任务的相关内容。本文件涵盖

以下设计过程:

•硬件、IP和平台开发:为硬件创建PL IP块

平台,创建PL内核,子系统功能仿真,并评估

Vivado®计时、资源使用和电源关闭。还包括开发

用于系统集成的硬件平台。

网表和设备对象

Vivado Design Suite支持内存设计中的许多一流对象

数据库这些对象表示逻辑设计、设备的单元、网络和端口

目标Xilinx设备或平台板的资源,以及特定用户使用的对象

Vivado设计套件的功能,如IP集成商使用的块设计对象,或

Vivado硬件管理器使用的硬件对象。Vivado设计套件映射

将逻辑设计的网表对象映射到目标设备或板的设备对象上。

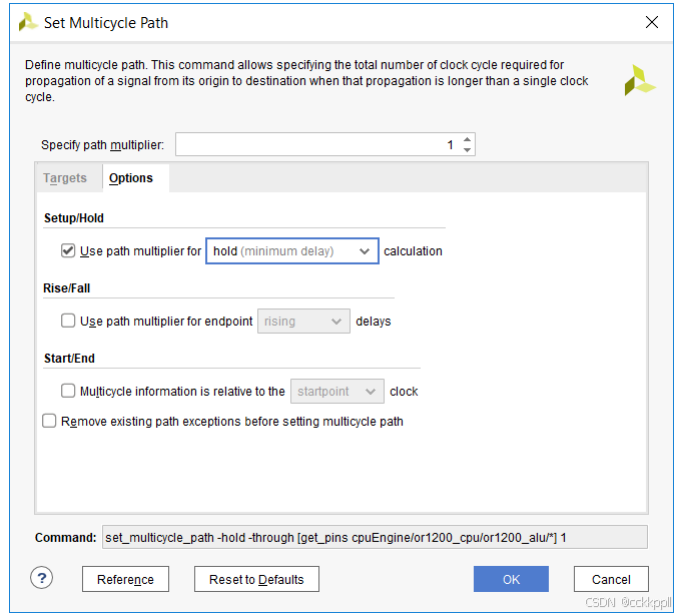

图1-1,第10页说明了一些Vivado工具第一类之间的关系

物体。此图具有代表性,并非旨在描绘所有Vivado工具的第一类

对象或它们的关系。

显示在图1-1顶部的网表对象是逻辑设计的一部分

编程到FPGA中。设备对象,如图的下半部分所示,是零件

实际物理设备的,并包括区域资源,如时钟区域、瓦片、站点或

CLB。设备对象还包括封装引脚和I/O组,如的左侧所示

图,以及路由资源,如节点、导线和管道,如中的右侧所示

图形

Vivado Design Suite中存在其他类别的一级对象,例如计时

对象,它们与网表设计相结合以创建计时报告和约束

放置和布线结果。与网表和设备关联的定时对象

对象,提供了对所实现的设计的完整时序分析。计时对象

包括时钟、定时路径和延迟对象。

对象之间的关系由连接两个对象的箭头显示:

•双向箭头表示可以从以下任一位置查询关系

方向例如,您可以查询连接到特定网络的单元格(get_cells

-of_objects[get_nets]),或查询连接到特定单元格的网络

(get_nets-of_objects[get_cells])。

•单端箭头反映的关系只能在的方向上查询

箭头。例如,在图1-1中,您可以看到您可以查询位于

在特定的时钟区域(get_bels-of_objects[get_clock_regions])中,但是

您无法获得与特定贝尔相关联的时钟区域。

一类对象的描述、它们与其他对象的关系以及特性

在这些对象上定义的。

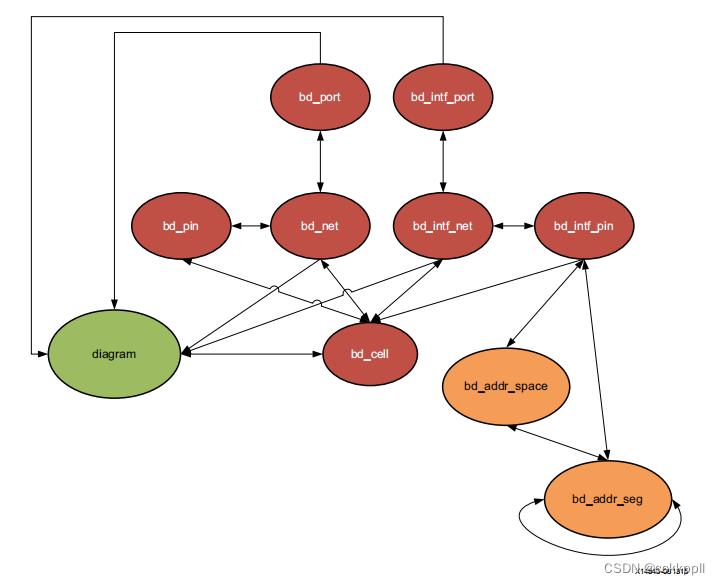

块设计对象

块设计是由互连的IP核心组成的复杂子系统设计,可以

或者用作独立的设计或者被集成到其他设计中。块设计,或

图表,可以使用Vivado Design Suite的IP集成程序创建。它们可以是

交互式创建,在Vivado Design Suite IDE中的IP集成商的画布上,或

以交互方式使用Tcl命令。

块设计图对象在结构上与网表对象非常相似

如前所述。组成的不同设计对象之间的关系

方块设计或图表如图1-2所示。

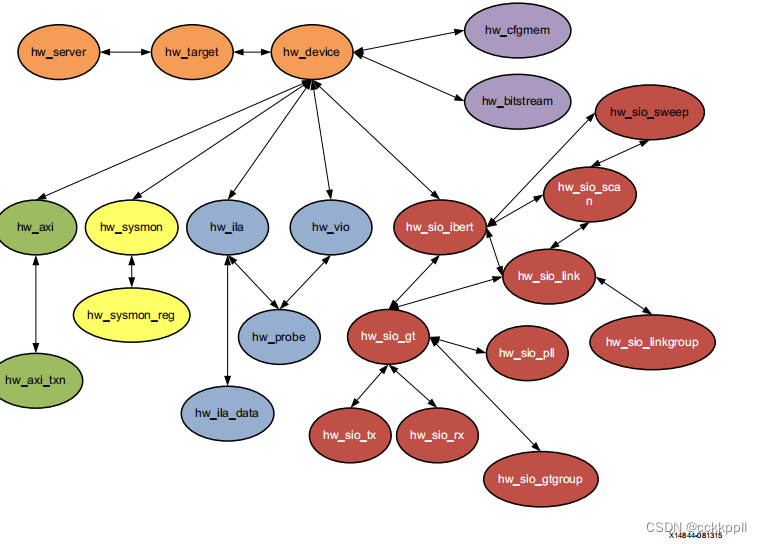

硬件管理器对象

硬件管理器是Vivado Design Suite的一项功能,可用于连接到

设备编程器或调试板,并锻炼编程的硬件设备。这个

硬件管理器允许您在设备上练习调试逻辑,访问要设置或

检索当前值。Vivado硬件管理器的许多调试核心和对象

如图1-3所示。

这篇关于Vivado Design Suite一级物件的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!