边沿专题

epoll下电平触发LT和边沿触发ET的区别

LT 电平触发 高电平触发 EPOLLIN 事件 数据可读 内核中的socket接收缓冲区 为空 低电平 不会触发 内核中的socket接收缓冲区 不为空 高电平 会触发 EPOLLOUT事件 数据可写 内核中的socket发送缓冲区不满 高电平 内核中的socket发送缓冲区 满 低电平 ET 边沿触发 转换的时候触发

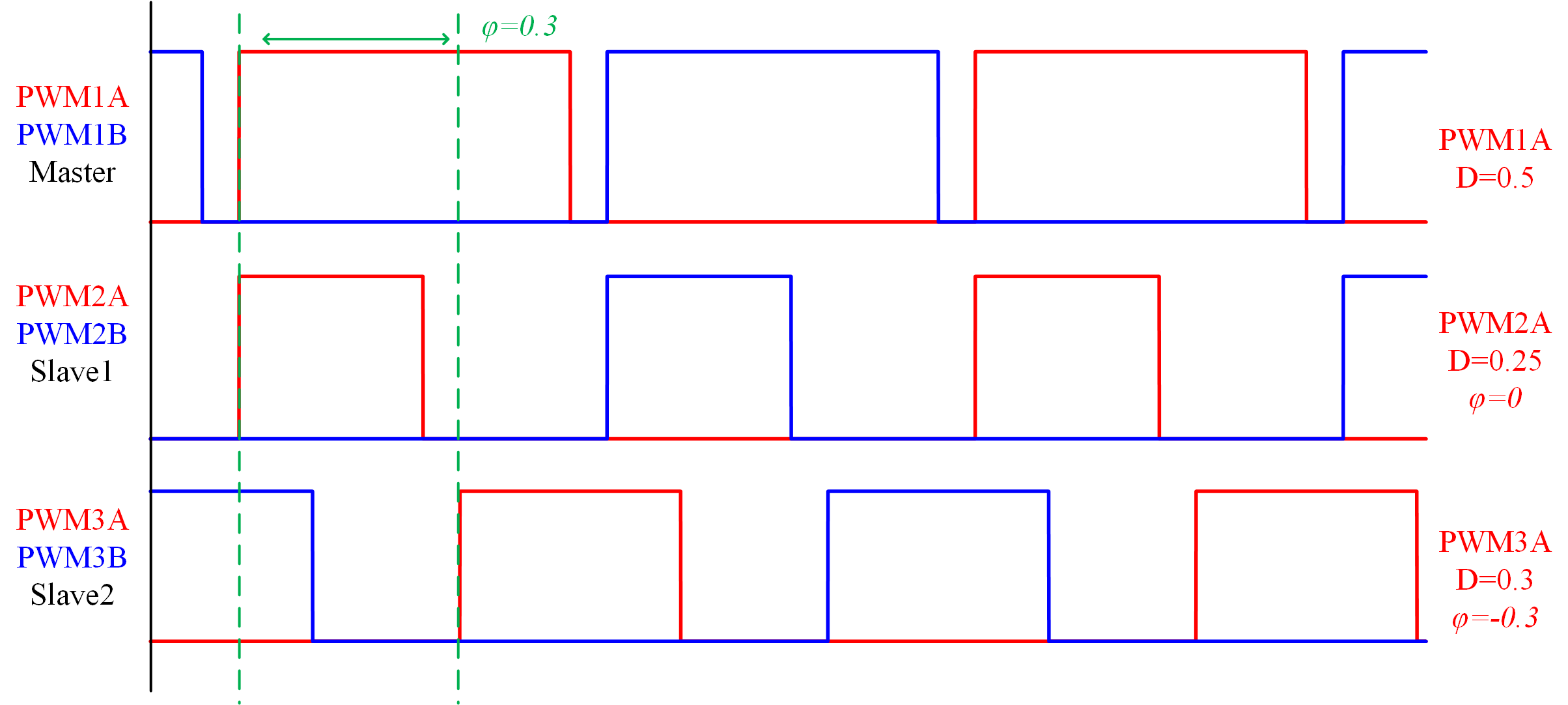

28335 ePWM模块 中心移相与边沿移相代码

中心移相 最常见的中心移相示意图如下: 可以看到其中的PWM1作为主相,其余PWM2和PWM3都作为其的辅相。中心移相,顾名思义,就是移动相位参考高电平的中心,当占空比D=0.5时,其移相与我们认为的上升沿移相一致,也就是最常见的移相。 为方便理解,先给相关设置的结构体设置: typedef struct {volatile struct EPWM_REGS* ePWMx;Uint32

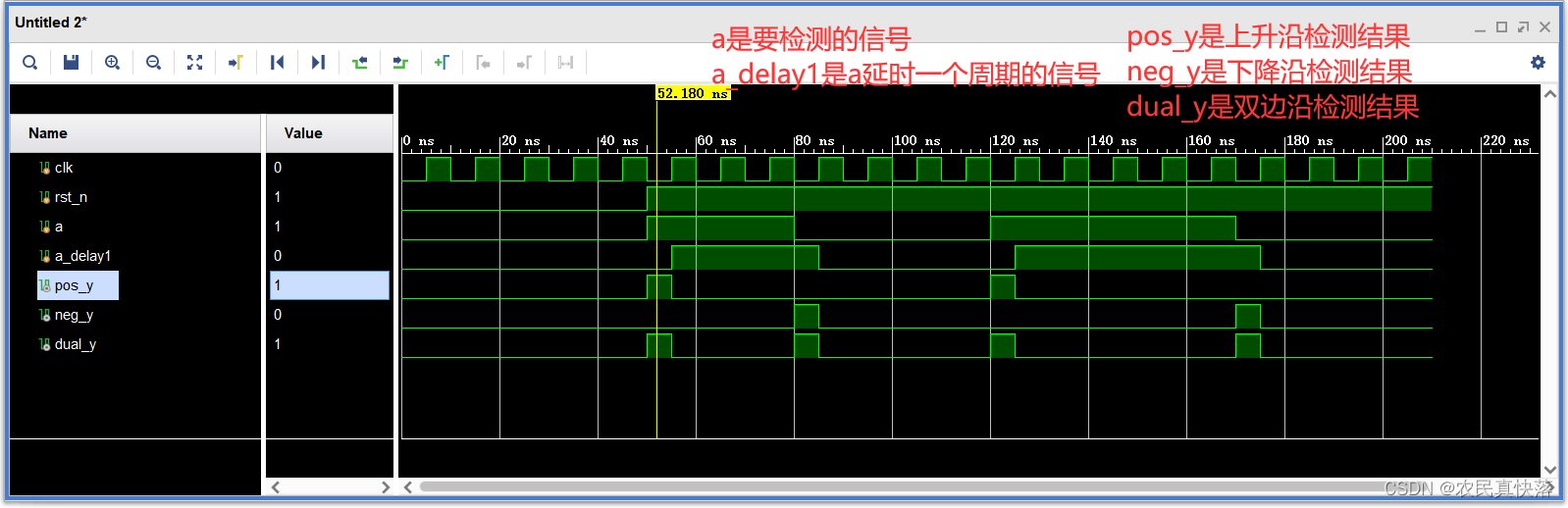

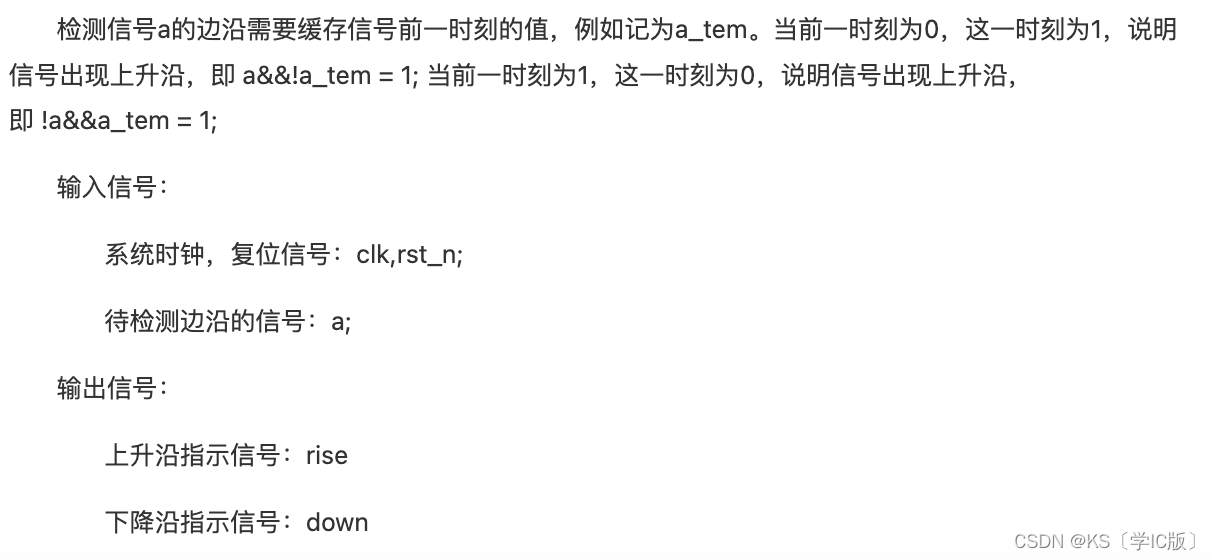

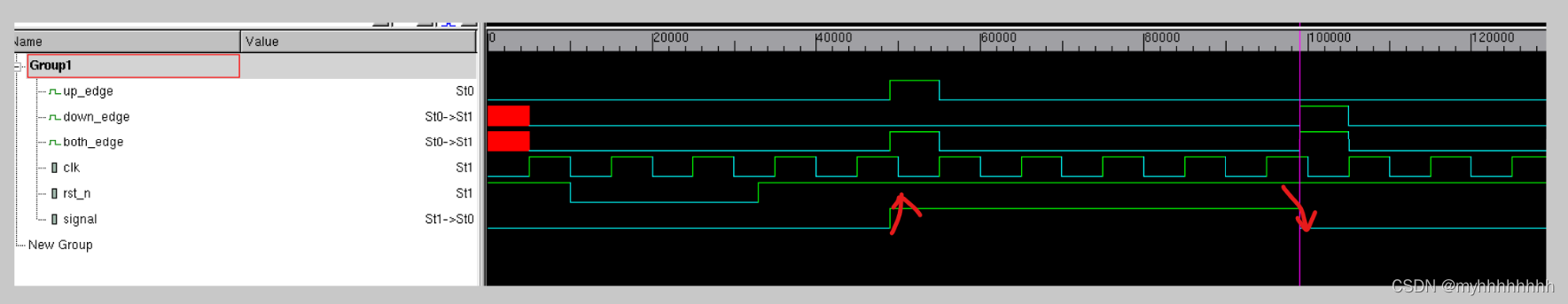

【IC设计】边沿检测电路(上升沿、下降沿、双沿,附带源代码和仿真波形)

文章目录 边沿检测电路的概念上升沿检测电路下降沿检测电路双边沿检测电路代码和仿真RTL代码Testbench代码仿真波形 参考资料 边沿检测电路的概念 边沿检测指的是检测一个信号的上升沿或者下降沿,如果发现了信号的上升沿或下降沿,则给出一个信号指示出来。 边沿检测电路根据检测边沿的类型一般分为上升沿检测电路、下降沿检测电路和双沿检测电路。 上升沿检测电路 如图所示,我们的

08 - D 边沿触发器

---- 整理自B站UP主 踌躇月光 的视频 1. D 边沿触发器电路 1.1 改造 RS 触发器 加入清零端和置位端。 Clear=1 时,Q=0,Q’=1 Pre=1时,Q’=0,Q=1 1.2 D 触发器中加入清零和预置 EN=1,D=0 时,R=1,S=0,Q=D=0,Q’=1 EN=1,D=1 时,R=0,S=1,Q=D=1,Q’=0 EN=0 时,R=S=0,Q

我的OpenCV学习笔记(17):利用形态学学滤波检测边沿和角点

首先如何理解对灰度图像进行形态学操作? 一种比较形象的方法是将灰度图像看做是“等高线”:亮的区域代表山峰,而暗的区域代表山谷,图像的边沿就对应于峭壁。如果腐蚀一幅图像,会导致山谷被扩展,而峭壁减少了。相反的,如果膨胀一幅图像,峭壁则会增加。但是这两种情况下,中间的部分(大片的谷底和高原)基本保持不变。 在上述理解的基础上,如果我们对图像的腐蚀和膨胀的结果做差,就能提取图像的边界:因为边界区域,

Verilog经典题(一)——边沿检测、格雷码与二进制码的转换

文章目录 边沿检测思路代码波形&总结 格雷码与二进制码的转换思路代码波形&总结 边沿检测 实现信号边沿检测功能,输出一个周期宽度的脉冲信号 思路 边沿的两侧信号是相反的。 上升沿 = ~res[0] && res[1] 下降沿 = res[0] && res[1] 边沿 = 上升沿 | 下降沿 = res[0] ^ res[1] 输入信号 clk,rst,din输出 o1,

数字电路 第四章—第四节(边沿触发器(上))

一、边沿D触发器 1、电路组成及逻辑符号 下图所示是用两个同步D触发器级联起来构成的边沿D触发器。 2、工作原理 3、异步输入端的作用 (1)下图所示是带有异步输入端的边沿D触发器的逻辑电路图和逻辑符号(右上是曾用符号,右下是国标符号)。 (2)同步输入端与异步输入端: (3)异步输入端的工作原理: (4)异步输入端是预置触发器初始状态,或者

FPGA中边沿提取的verilog代…

原文地址:FPGA中边沿提取的verilog代码 作者:SUN_403 always@(negedge clk, negedge rst) begin if (rst == 1'B0) din_1 <= 1'B1; else if(clk == 1'B0) begin i_posedge <= (~din_1) & en;

modelsim时许仿真中对边沿状态的读取

三天前写了一个1101序列检测电路,但是仿真结果一直不对。当我从源文件上绞尽脑汁也不知道哪里错了,后来发现是modelsim在时钟上升沿时对状态的读取方式和我们数电老师讲的不一样造成的。 错误: 红色的是按照数电刚开始老师讲的,上升沿到时读取状态为上升沿前一时刻的状态,故读取1101,但输出并没有变为1 其实当上升沿到时,如果需要读取的数据正好也是在上升沿或下降沿,则读法不一样。 上升

电平触发方式和边沿触发的区别

电平触发方式是按照电平的高或者低来触发,所以用的时候,必须在发生触发事件后立即将电平拉到非触发电平上,如果不这样做的话,会导致程序一直在触发事件程序入口处,而不会执行其他地方的程序。所以一般比较少用。 边沿触发方式是按照(上或下)边沿触发事件,由于触发的条件是边沿(上或下),所以即使在触发事件后,保存原来的电平都没有关系,不会一直在触发的,一般都用这种方式。 //将P3.2连接至GN

「Verilog学习笔记」边沿检测

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 `timescale 1ns/1nsmodule edge_detect(input clk,input rst_n,input a,output reg rise,output reg down);reg a_tem ; always @ (posedge clk or neg

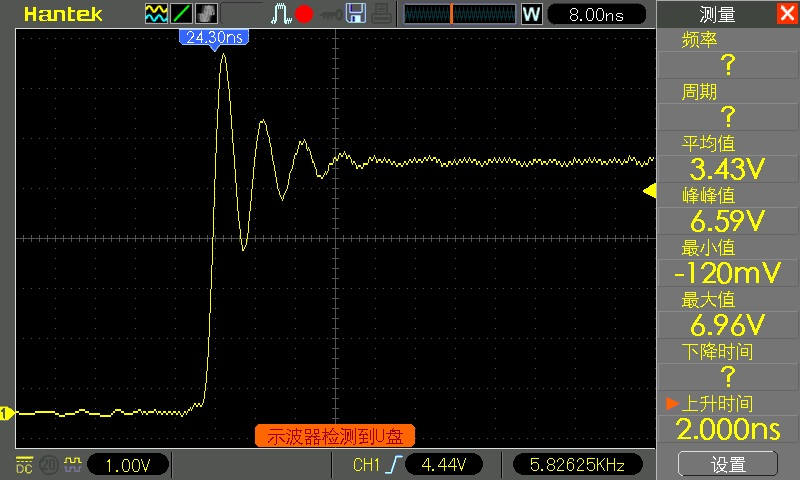

快速边沿脉冲发生器实验

快速边沿脉冲发生器是一种能够产生高频率、快速上升或下降边沿的电路或设备。它通常用于测试和测量领域,特别是在数字电路和通信系统中。 快速边沿脉冲发生器的工作原理通常基于电容放电或者开关切换的原理。其中,电容放电方式是通过充电电容器并在需要的时候通过放电来产生脉冲。而开关切换方式则是通过开关的切换来控制电路的导通和断开,从而产生脉冲。 快速边沿脉冲发生器的特点包括: 1. 高频率:能够产生高频率的

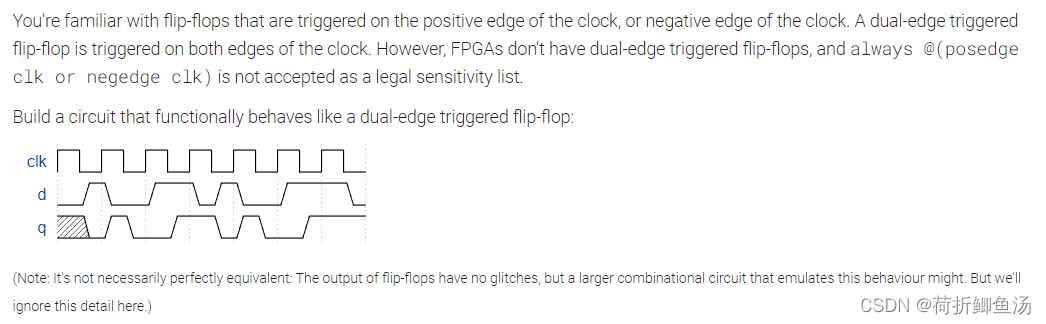

Verilog单边沿检测和双边沿检测的方法(HDLBits例题)

1.单边沿检测 边沿检测是用来检测某一信号是否发送了从0至1或者从1至0的变化,有同步和异步之分。 同步边沿检测:是使用一个基准时钟,即在同一个时钟下来检测一个信号的上升沿或者下降沿。 异步边沿检测:是利用D触发器来实现边沿检测。 HDLBits例题: 单边沿检测例题 题目:对于8位向量中的每一位,检测输入信号在一个时钟周期内从0变化到下一个时钟周期的1(类似于正边缘检测)。输出位应该在0

STM32F103 设置双边沿触发输入捕获中断(TIM3 CH1)

在STM32的配置中,有这么一个设置: 但是这其实是设置下降沿捕获,对应设置的寄存器为CCER, 可以看到这双沿触发就是下降沿触发。因为bit[3:2]都是保留的。 因此在仔细查看了各路大佬的博客后,发现双边沿触发是可以设置的。 原贴http://www.openedv.com/thread-12644-1-1.htmlhttp://www.openedv.com/thread

7、epoll边沿触发与反应堆

epoll边沿触发 1、epoll事件模型: epoll监听的是文件描述符,也可以监控进程间通信的事件。 #include <stdio.h>#include <stdlib.h>#include <sys/epoll.h>#include <errno.h>#include <unistd.h>#define MAXLINE 10int main(int argc, char

【FPGA】跨时钟域问题(二)(单bit信号跨时钟域 1. 电平同步器 2. 边沿同步器 3. 脉冲检测器)

【FPGA】跨时钟域问题(二)(单bit信号跨时钟域 1. 电平同步器 2. 边沿同步器 3. 脉冲检测器) 作者:安静到无声 个人主页 作者简介:人工智能和硬件设计博士生、CSDN与阿里云开发者博客专家,多项比赛获奖者,发表SCI论文多篇。 Thanks♪(・ω・)ノ 如果觉得文章不错或能帮助到你学习,可以点赞👍收藏📁评论📒+关注哦! o( ̄▽ ̄)d ლ(°◕‵ƹ′◕ლ)希望在传播知识

【数字IC手撕代码】Verilog边沿检测电路(上升沿,下降沿,双边沿)|题目|原理|设计|仿真

芯片设计验证社区·芯片爱好者聚集地·硬件相关讨论社区·数字verifier星球四社区联合力荐!近500篇数字IC精品文章收录!【数字IC精品文章收录】学习路线·基础知识·总线·脚本语言·芯片求职·EDA工具·低功耗设计Verilog·STA·设计·验证·FPGA·架构·AMBA·书籍 Verilog边沿检测电路 一、前言二、边沿检测电路题目三、边沿检测电路原理四、RTL设计五、Testb