布线专题

RF射频信号布局布线要点

RF射频信号布局布线要点 一、射频产品布局要求: 1、布局采用一字型布局。在同一个屏蔽腔体内,布局时应该按RF主信号流一字布局由于空间限制,如果在同一个屏蔽腔内,RF主信号的元器件不能采用一字布局时,可以采用L形布局,不要用U字形布局。 2、相同单元的布局要尽量保证完全相同。有多个接收通道和发射通道,就要保证多个通道的布局和布线要完全相同。 3、布局时就要考虑RF主信号走向,和器件

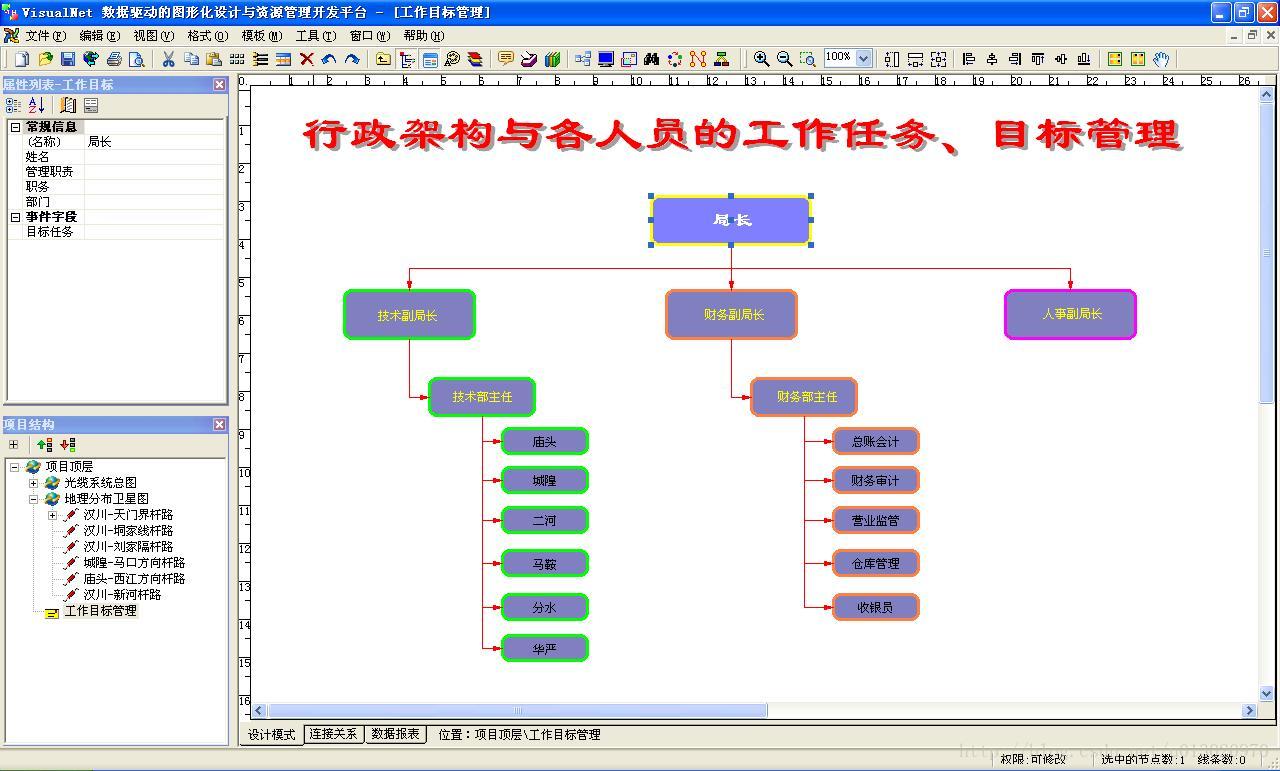

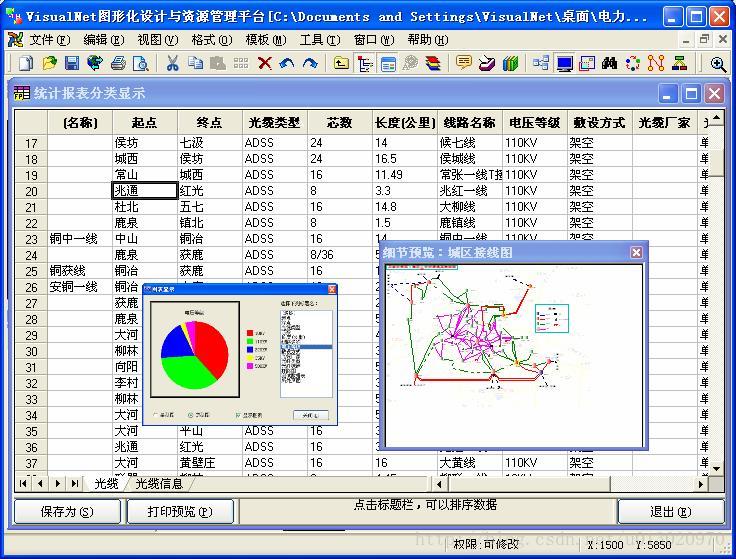

VisualNet综合布线管理系统

VisualNet采用C/S+B/S架构(见图1),为用户提供一个虚拟现实的网络资源综合性管理平台,系统所有设施设备编码具有唯一性,没有重复编码,真正实现精确管理。 VisualNet的特点概括为 ①采用易于理解的图形化方式,来集中管理设备对象、连接关系以及数据属性; ②采用由总到分、由粗到细的层次化的管理模式,便于管理复杂的大型网络; ③每个图形对象均可被查询、定位和管理,并与

VisualNet设备布线管理

一、背景情况 在对含有各种设备、线路、网络资源的项目进行设计、施工、维护和管理时,都会遇到一个共同特点,即它们存在着大量的设备节点和节点间复杂的连接关系,既难于理解又不便管理,它们带来一系列难以了解清楚的问题是。 然而,目前却很难找到一条有效的途径来管理这些日益复杂和离散的系统。缺少对这些基础设施的配置和资源使用状况的了解,导致日益严重的设备故障、低效的技术支持、资产的不明

VisualNet在网络综合布线设备管理中的优越性

一、实现的功能 1、提供一个图形化的设计管理平台 系统采用易于理解的图形方式,通过创建一个“虚拟现实”的环境来,来管理各种数据信息、设备对象以及相互之间复杂的连接关系。 系统提供了近10万的图库模板,采用“所见即所得”的拖放式设计方式,“即改即显”。譬如房屋、辖区地图、医务室、报警点、居委会、小区平面图等。 比GIS设计更方便、快捷,操作步骤更少、模板更多! 2、采用层次化的管

VisualNet综合布线项目实际应用其三

1、与网管软件集成 说明:与各种设备检测系统、监控系统进行集成,随时调阅查看它们的运行状态。并通过登录接口进行相应参数的配置管理。 2、与文档资料的集成 说明:开放式的接口,可把平时需要管理的文档进行电子化、标准化集中管理。如检测报告、图片、施工回单、设备技术文件、驱动程序等等。分门别类的根据权限进行调阅、查询。 3、与短信、传真系统的集成

VisualNet综合布线管理系统应用实例展示

如下图一所示的是我们地区的综合布线资源管理项目的一个截图。目前我们采用了由总到分,先粗后细的方式,实施完成了各个站的布局设计、光缆连接设计、杆路图设计、光缆熔接信息设计、机房机柜布置、设备布局、设备端口连接、配线跳线设计以及通信电源设备布局设计。在图纸设计完成后,我们对各个设备、线路对象进行了数据录入,同时还把我们平时所关心的设备管理技术文档、承载的业务报表、光缆检测数据文档都一起进行了集成整合。

PCB布线——【四五年的经验】

http://www.geek-workshop.com/thread-1448-1-3.html 一般PCB基本设计流程如下:前期准备->PCB结构设计->PCB布局->布线->布线优化和丝印->网络和DRC检查和结构检查->制版。 第一:前期准备。这包括准备元件库和原理图。“工欲善其事,必先利其器”,要做出一块好的板子,除了要设计好原理之外,还要画得好。在进行PCB设计之 前

(转)【PCB布局布线】之差分布线和阻抗匹配

【PCB布局布线】之差分布线和阻抗匹配(转) 一、PCB 差分布线操作 参看:Altium Designer -- 精心总结 PCB 差分布线已经讲的很清楚了,在此不做介绍。 二、差分布线优缺点 参看:实际运用中差分信号线的分析和 LAYOUT 参看:差分信号 -- 维基百科 (1) 差分信号 首先来看一下什么是差分信号吧。 1、差分信号 差分传输是一种信号传输的技术,

ad18学习笔记22:关于keep out layer禁止布线层

ad18里的新特性,在 keep out层无法直接放置线条,需要去菜单-放置-keepout进行画线,如果,在其他层画了一个图形,无法直接修改这个图形的属性,把他变为keepout的线条,但是可以通过特殊粘贴操作,把它转移过来。 比如,我在机械层画了一个异性的板框,我想在keepout层画一个一样的板框边沿,如果用线条和弧线一点点去画太浪费时间了,还不一定能完全重合,这个时候就可以把这个板框线条

NYOJ38, 布线问题

布线问题 时间限制: 1000 ms | 内存限制: 65535 KB 难度: 4 描述 南阳理工学院要进行用电线路改造,现在校长要求设计师设计出一种布线方式,该布线方式需要满足以下条件: 1、把所有的楼都供上电。 2、所用电线花费最少 输入 第一行是一个整数n表示有n组测试数据。(n<5) 每组测试数据的第一行是两个整数v,e. v表示学校里楼的总个数(v<

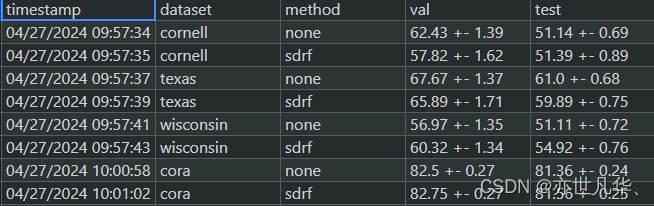

【传知代码】基于曲率的图重新布线(论文复现)

前言:在图形处理中,一个至关重要的问题是图形的重新布线,即在不改变图形基本结构的前提下,通过调整节点间的连接关系,使图形具有更好的性质,如更低的复杂度、更高的可视化效果或更强的鲁棒性。传统的图形重新布线方法往往依赖于直观的经验或简单的启发式算法,难以适应复杂多变的应用场景,近年来,基于曲率的图重新布线技术应运而生,为图形优化领域带来了新的曙光。与传统的方法相比,基于曲率的图重新布线技术更加注重图

探索800G数据中心的高速布线解决方案

随着技术的快速进步,数据中心正以前所未有的速度迅速发展。虽然100G和400G数据中心已经普及,但800G数据中心正逐渐流行并展现出增长趋势。由于对高速数据传输的需求呈指数级增长,因此需要高效、可靠的线缆连接解决方案。本文将介绍800G数据中心的DAC、AOC和光纤跳线的布线解决方案。 800G数据中心DAC和AOC解决方案 直连铜缆(DAC)包括无源铜缆、有源铜缆(ACC)和有源铜缆(AEC

Blender + Marvelous Designer(MD)服装,Quad Remesher四边面拓扑布线、UV投射

Blender + Marvelous Designer(MD)服装,Quad Remesher四边面拓扑布线、UV投射_哔哩哔哩_bilibili Blender+MD服装,Quad Remesher四边面拓扑和UV投射 - 哔哩哔哩 https://i0.hdslb.com/bfs/article/b3f270cb02bb6de5cc080d732dc8283850669770.png

1349:【例4-10】最优布线问题

【解题思路】 最小生成树模板题,求最小生成树所有边权加和。 该题输入的是邻接矩阵,因此使用邻接矩阵解决该问题。当然也可以保存为邻接表。 【参考代码】 //示例代码 Prim算法#include <iostream>#include <cstring>#include <cstdio>using namespace std;const int N=105; // 定义常量 N,表

基于Swift实现的最小生成树应用-室内布线

1 问题内容与目的要求 求解最优化问题的算法通常需要经过一系列的步骤,在每个步骤都面临多种选择。对于许多最优化问题,使用动态规划算法求最优解显得大材小用,可以使用更简单、更高效的算法。贪心算法就是这样的算法,它在每一步都做出当时看起来最佳的选择。也就是说能找到最优解的最优化问题。贪心算法并不能保证得到最优解,但对很多问题确实可以求得最优解。 贪心方法是一种强有力的算法设计方法,可以很好的解决很多

[激光原理与应用-95]:电控 - PCB布线常见降低信号干扰的手段

目录 一、降低信号干扰的PCB布线 二、常见规则与技巧 2.1. 布线规则 (1) 信号线和电源线分开布线 (2) 信号线和地线相邻布线 (3) 高频信号线短而直 (4) 电源线宽而短 (5)地线密集布线 2.2. 布线技巧 (1)使用层间连接 (2)使用电容和电感 (3)使用阻抗匹配 一、降低信号干扰的PCB布线 在PCB布线中,降低信号干扰是确保电路性能稳定性的

EDA(四)布局布线

EDA(四)布局布线 布局布线(Layout and Routing)是电子设计自动化(EDA)领域中的一个重要环节,特别是在集成电路(IC)设计和印刷电路板(PCB)设计中。它涉及到将电路设计中的逻辑门、晶体管、电容器、电阻器等电子元件在物理空间中进行精确的放置(布局),并通过导线(通常称为走线或布线)将它们连接起来,以实现电路的功能。 布局(Layout) 布局是指在芯片或电路板上为电子

Allegro 17.2 布线阻抗分析

Allegro 17.2布线阻抗分析 做多层电路板的时候,遇到需要做阻抗要求的时候,一般使用SI9000做阻抗设计。或者向PCB厂商拿叠层结构信息。无论哪一种,只是停留在设计层面,在设计PCB的走线线,是否完全做到阻抗一致,还

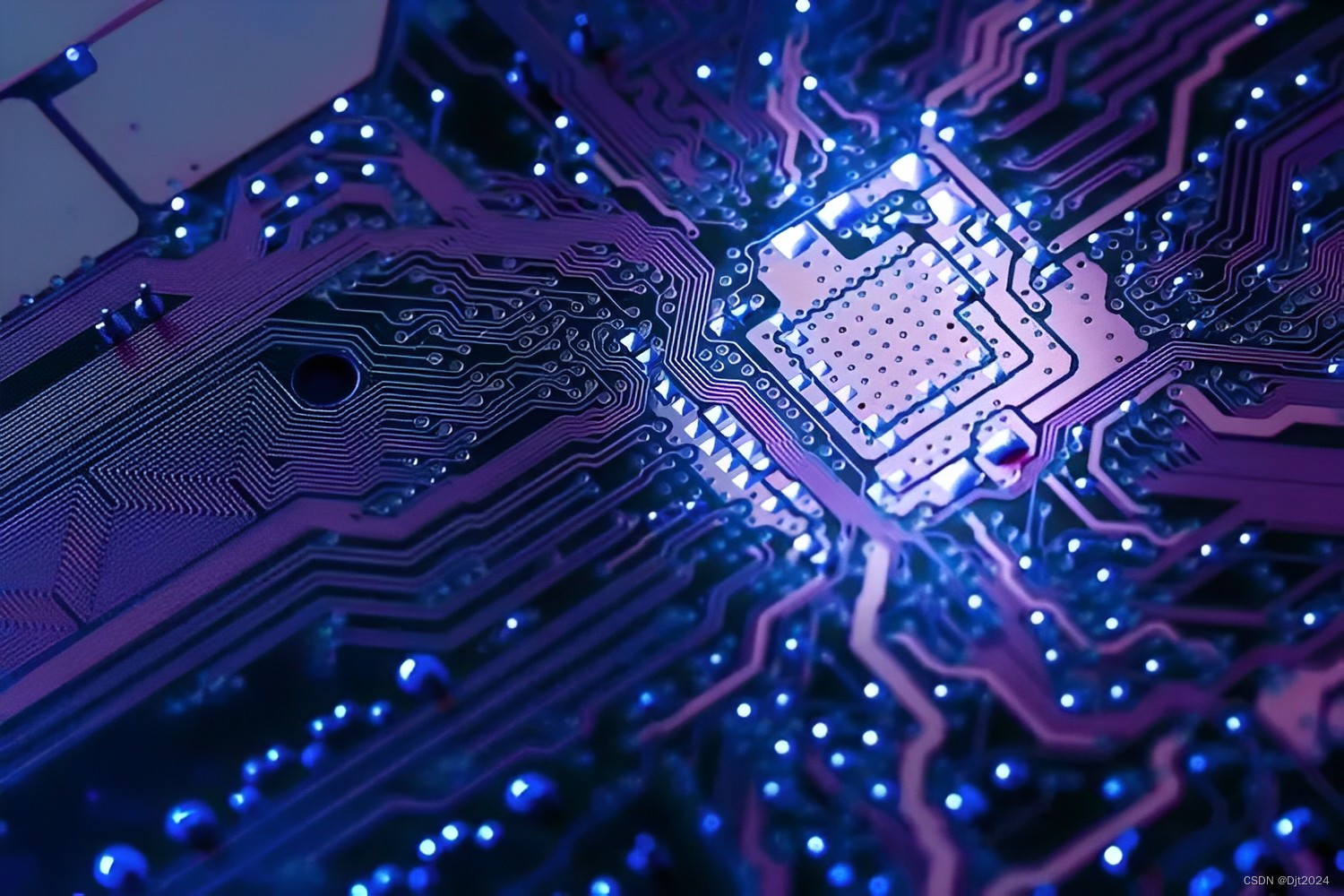

电机控制器电路板布局布线参考指导(七)电流检测模块布局布线

电机控制器电路板布局布线参考指导(七)电流检测模块布局布线 1.高侧电流检测2.低侧电流监测3.两相和三相电流检测4.关键元器件选型要求5.布局6.布线7.工具设置8.输入和输出滤波9.注意事项 很多电机驱动器产品系列包括内置了电流感测功能的器件,其中大多数均使用外部分流电阻作为测量源。通过将电流感测放大器与驱动器结合在一起,为电机接口提供了一体化的解决方案,并且能够以更低的成本实

GlobalRouting - FastRoute布线算法运行流程(二)

文章目录 1. 运行步骤 FT::run 1. 运行步骤 首先生成2D的布线,然后进行层分配以及生成3D的布线,最后计算结果并返回。具体流程如下: 读取查找表flut, POST9.dat, POWV9.dat使用查找表生成RSMT,将多pin线网拆分为2pin线网进行第一遍2D布线优化RSMT,建立各节点之间的MST,并进行第二遍2D布线,最后进行螺旋布线将2D布线结果转

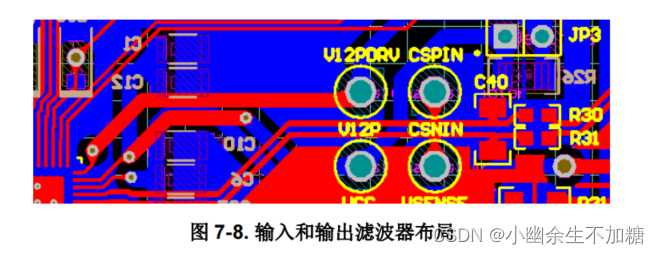

xilinx 7系列FPGA时钟布线资源

7系列FPGA拥有多种时钟路由资源,以支持各种时钟方案和需求,包括高扇出、短传播延迟以及极低的偏斜。为了最佳地利用时钟路由资源,需要了解如何将用户时钟从PCB传递到FPGA,确定哪种时钟路由资源最优,然后通过利用适当的I/O和时钟缓冲器来访问这些时钟路由资源。 一、时钟缓冲 7系列FPGA具有丰富的时钟资源。各种缓冲器类型、时钟输入引脚和时钟连接性可以满足许多不同的应用需求。选择适当的时钟资源

电机控制器电路板布局布线参考指导(五)

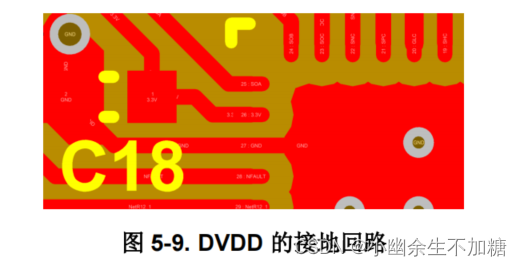

电机控制器电路板布局布线参考指导(五)大容量电容和旁路电容的放置 1.大容量电容的放置2.电荷泵电容器3.旁路电容/去耦电容的放置3.1 靠近电源3.2 靠近功率器件3.3 靠近开关电流源3.4 靠近电流感测放大器3.5 靠近稳压器 tips:资料主要来自网络,仅供学习交流 1.大容量电容的放置 在电机驱动系统设计中,大容量电容器可大幅度减轻低频电流瞬变的影响,并存储电荷以在

电机控制器电路板布局布线参考指导(四)

电机控制器电路板布局布线参考指导(四)一般布线指导 1.使栅极驱动布线尽可能宽并尽可能短2.高侧栅极的信号布线应和开关节点布线尽可能靠近3.不要使用直角布线4.泪滴技术5.在目标周围应以平行线对的方式布线6.将无源器件(例如源匹配电阻或交流耦合电容器)放置在信号路径内7.将电路的模拟和数字部分单独接地是最简单和最有效的噪声抑制方法之一 在进行电机驱动器 PCB 设计时,请遵循以下通

![[激光原理与应用-95]:电控 - PCB布线常见降低信号干扰的手段](https://img-blog.csdnimg.cn/img_convert/aebbf2ba95e30e9ffb89b7ef9e7e2cb3.jpeg)