本文主要是介绍xilinx 7系列FPGA时钟布线资源,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

7系列FPGA拥有多种时钟路由资源,以支持各种时钟方案和需求,包括高扇出、短传播延迟以及极低的偏斜。为了最佳地利用时钟路由资源,需要了解如何将用户时钟从PCB传递到FPGA,确定哪种时钟路由资源最优,然后通过利用适当的I/O和时钟缓冲器来访问这些时钟路由资源。

一、时钟缓冲

7系列FPGA具有丰富的时钟资源。各种缓冲器类型、时钟输入引脚和时钟连接性可以满足许多不同的应用需求。选择适当的时钟资源可以改善布线能力、性能以及FPGA的整体资源利用率。

1、BUFG

在以下情况下最适合使用:

• 设计或设计的部分在设备的较大区域内具有全局范围,且功能的本地化不可能实现。

• 硬件功能块,如块RAM、DSP或跨多个时钟区域的集成IP,需要级联,或需要连接到附近没有的CLB。

• 通过同步(无抖动)或异步切换时钟,应用程序能够切换到停止的时钟或选择具有不同频率的时钟(例如,用于降低功耗)。

• 可以使用时钟使能(CE)功能在非工作期间降低功耗。然而,在大多数情况下,由于时序(CE延迟)限制,不应使用CE功能来模拟时钟元件上的真正CE逻辑功能。

2、BUFR和BUFIO

BUFR和BUFIO组合的主要目的是支持源同步接口。

当接口被放置在一个单一区域内时,BUFIO对SelectIO的高速侧进行时钟驱动,而BUFR则对反序列化/序列化侧以较低速度进行时钟驱动,将其送入FPGA逻辑,提供时钟域转移功能。

3、BUFMR(BUFMRCE)

对于需要比单个时钟区域/bank中可用逻辑和(或)I/O更多的接口,BUFMR(BUFMRCE)用于将时钟域转移功能扩展到上方和下方的时钟区域。

4、BUFR

某些需要与时源同步I/O用例无关的分割时钟的应用类型,可以使用BUFR作为简单的时钟分频器,当无法使用MMCM/PLL或它不适用于频率分频功能时。在这种情况下,必须特别注意时序和偏斜,因为这不是BUFR的主要用途。

5、BUFH(BUFHCE)

水平时钟缓冲器BUFH(BUFHCE)严格来说是一种区域性资源,不能跨越上方或下方的时钟区域。与BUFR不同,BUFH没有时钟分频的能力。

• BUFH类似于全局时钟资源,但仅在跨越两个水平区域的区域基础上。

• BUFH具有作为MMCM/PLL反馈的能力,并且可以补偿时钟插入延迟。

• 当接口或逻辑云可以定位到一个时钟区域或两个水平相邻的时钟区域时,BUFH是首选的时钟资源。

• BUFH还具有一个时钟使能引脚(BUFHCE),可用于在逻辑或接口及其相关逻辑不活动时降低动态功耗。

• 时钟使能功能可以在每个时钟周期的基础上提供门控时钟。

• 与全局时钟树类似,BUFH也可以连接到CLB中的非时钟资源(使能/复位),但具有更好的偏斜特性。

• BUFH也可以用于时钟区域内时钟元件的同步启动。

二、带时钟功能的输入

外部用户时钟通过称为带时钟功能(CC)输入的差分时钟引脚对引入FPGA。带时钟功能的输入提供专用的高速访问到内部全局和区域时钟资源。带时钟功能的输入使用专用路由,并且必须用于时钟输入,以保证各种时钟特性的时序。具有本地互连的通用I/O不应用于时钟信号。

每个I/O bank位于单个时钟区域内,并包含50个I/O引脚。在每个I/O列的每个I/O bank中的50个I/O引脚中,有四个带时钟功能的输入引脚对(总共八个引脚)。每个带时钟功能的输入:

• 可以连接到PCB上的差分或单端时钟

• 可以配置为任何I/O标准,包括差分I/O标准

• 具有P侧(主)和N侧(从)

带时钟功能的输入在每个I/O bank中组织为2个MRCC和2个SRCC对。

1、SRCC

可以访问单个时钟区域以及全局时钟树,以及同一列中上方和下方的其他CMT。

可以驱动:

• 同一时钟区域内的区域时钟线(BUFR、BUFH、BUFIO)

• 同一时钟区域和相邻时钟区域中的CMT。

• 设备同一顶部/底部半部分的全局时钟线(BUFG)。

2、MRCC

可以访问多个时钟区域和全局时钟树。MRCC的功能与SRCC相同,并且还可以驱动多时钟区域缓冲器(BUFMR),以访问最多三个时钟区域。

如果带时钟功能的输入不用作时钟,则可以用作常规I/O。用作常规I/O时,带时钟功能的输入引脚可以配置为任何单端或差分I/O标准。

带时钟功能的输入可以连接到同一时钟区域中的CMT,以及上方和下方时钟区域中的CMT,但有一些限制。

3、单个时钟驱动单个CMT

当一个时钟输入驱动单个CMT时,带时钟功能的输入和CMT(MMCM/PLL)必须位于同一时钟区域。

4、单个时钟驱动多个CMT

单个时钟输入可以驱动同一列中的其他CMT。在这种情况下,MMCM/PLL必须放置在与带时钟功能的输入相同的时钟区域中。将额外的CMT放置在相邻区域是更优的选择,但同一列中距离超过一个CMT的CMT也可以被驱动。要使这种配置能够自动放置而无需CLOCK_DEDICATED_ROUTE约束,CMT中使用的资源必须相同。如果需要混合使用MMCMs/PLLs,则它们应首先放置在同一CMT中。

如果必须从不在同一时钟区域的带时钟功能的输入驱动CMT,并且与带时钟功能的输入相同的时钟区域中没有MMCM/PLL,则必须设置属性CLOCK_DEDICATED_ROUTE = BACKBONE。在这种情况下,MMCM或PLL不会将输出正确对齐到输入时钟。

用于驱动同一列中CMT的专用资源有限。一些Xilinx IP使用这些资源,因此它们无法用于其他设计用途,从而导致设计无法布线。如果到其他时钟区域的专用路由不可用,将CLOCK_DEDICATED_ROUTE设置为FALSE允许使用本地互联逻辑,尽管这会导致更长且无法补偿的延迟。

三、全局时钟资源

是专门为FPGA中各种资源的所有时钟输入而设计的一个互联网络。这些网络被设计成具有低偏斜、低占空比失真、低功耗以及改进的抖动容忍度。它们还支持非常高频率的信号。

理解全局时钟的信号路径有助于深入了解各种全局时钟资源。全局时钟资源和网络由以下路径和组件组成:

1、 时钟树和网络(Clock Tree and Nets) - GCLK

时钟树是一个层次化的结构,它确保时钟信号能够以最小的延迟和偏斜到达FPGA中的所有逻辑单元。

7系列FPGA的时钟树被设计为具有低偏斜和低功耗的操作。任何未使用的分支都会被断开。时钟树也可以用来驱动逻辑资源,如复位或时钟使能。这主要用于高扇出/负载网络。

全局时钟线的引脚访问并不局限于逻辑资源的时钟引脚。全局时钟线可以驱动CLB中的其他引脚(除了CLK引脚),例如控制引脚SR和CE。需要非常快速的信号连接和大负载/扇出的应用可以从这种架构中受益。

2、时钟区域

7系列设备通过使用时钟区域来改进时钟分布。每个时钟区域最多可以有12个全局时钟域。这12个全局时钟可以由单片设备或SLR中可用的32个全局时钟缓冲器的任何组合来驱动。时钟区域的尺寸固定为50个CLB高(50个IOB),并跨越芯片的左侧或右侧。在7系列设备中,时钟主干将设备分为左侧或右侧。主干并不位于芯片的中央。通过固定时钟区域的尺寸,较大的7系列设备可以有更多的时钟区域。7系列FPGA提供从1到24个时钟区域。

3、全局时钟缓冲器

在7系列设备中,最多有32个全局时钟缓冲器。一个CCIO输入可以直接连接到设备同一半部分中的任何全局时钟缓冲器。每个差分时钟引脚对可以连接到PCB上的差分或单端时钟。当用作差分时钟输入时,直接连接来自差分输入引脚对的P侧。当用作单端时钟输入时,必须使用引脚对的P侧,因为仅在此引脚上存在直接连接。

单端时钟输入必须分配给带时钟功能输入引脚对的P侧(主侧)。

如果单端时钟连接到差分时钟引脚对的P侧,N侧不能用作另一个单端时钟引脚——它只能用作用户I/O。

设备上半部分的CMT(时钟管理瓷砖)只能驱动设备上半部分的BUFG(全局时钟缓冲器),而设备下半部分的CMT只能驱动下半部分的BUFG。类似地,只有设备同一半部分的BUFG才能用作同一半部分设备中CMT的反馈。千兆收发器(GTs)只能直接连接到MMCMs/PLLs,当CMT列扩展到也包含完整列的GTs和I/O的区域时。

全局时钟缓冲器允许各种时钟/信号源访问全局时钟树和网络。全局时钟缓冲器的可能输入源包括:

• 时钟功能输入

• CMT,包括混合模式时钟管理器(每个CMT一个MMCM和一个PLL),驱动设备同一半部分的BUFG(全局时钟缓冲器)

• BUFG

• 通用互联

• BUFR

• 千兆收发器

7系列FPGA的时钟功能输入可以通过时钟主干列中存在的垂直时钟网络间接驱动全局时钟缓冲器。32个BUFG被组织成两组,每组16个BUFG,分别位于设备的顶部和底部。任何直接连接到BUFG的资源(例如GTX收发器)都有顶部/底部的限制。例如,顶部的每个MMCM只能驱动位于该顶部区域的16个BUFG。同样,底部的MMCM驱动底部的16个BUFG。

所有全局时钟缓冲器都可以驱动7系列设备中的所有时钟区域。但是,单个时钟区域中只能驱动12个不同的时钟。时钟区域(50个CLB)是时钟树的一个分支,由25行CLB向上和25行CLB向下组成。时钟区域跨越设备的一半。

时钟缓冲器被设计为同步或异步的无故障2:1多路复用器,具有两个时钟输入。存在一条专用路径(路由资源)用于BUFG级联,以允许选择两个以上的时钟输入。7系列FPGA的控制引脚提供了广泛的功能和强大的输入切换。

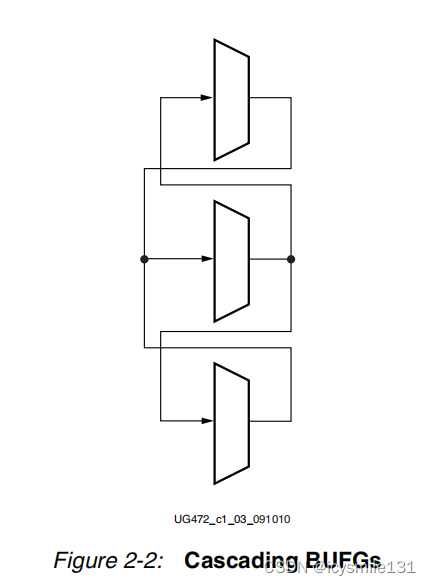

在7系列FPGA的时钟架构中,BUFGCTRL多路复用器及其所有派生器件可以在设备的上半部和下半部每组16个时钟缓冲器内与相邻的时钟缓冲器进行级联,从而在上半部有效地形成一个由16个BUFGMUX(BUFGCTRL多路复用器)组成的环,在下半部形成另一个由16个BUFGMUX组成的环。图2-2展示了BUFG级联的简化示意图。

这篇关于xilinx 7系列FPGA时钟布线资源的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!