层次化专题

推荐一款功能全面的层次化笔记应用,支持自由拖拽、缩放、旋转,可视化非常牛逼(附源码)

背景 不知道各位大佬日常生活中笔记软件用的多不,小编在工作中常常用笔记来记录每天的收获和安排。笔记软件的好坏直接影响了工作的心情和效率。今天给大家介绍的这款笔记软件,以其强大的笔记功能为基础,创造性地融入了画布式的自由编辑特性。在这里,你不仅可以像在传统笔记本上一样记录文字、绘制图表,更能够像操作实体白板一样,自由地拖拽、缩放、旋转各种元素,实现思维的可视化呈现。让我们一起来看看吧。 简介

【C++继承解密】:构建层次化设计的艺术

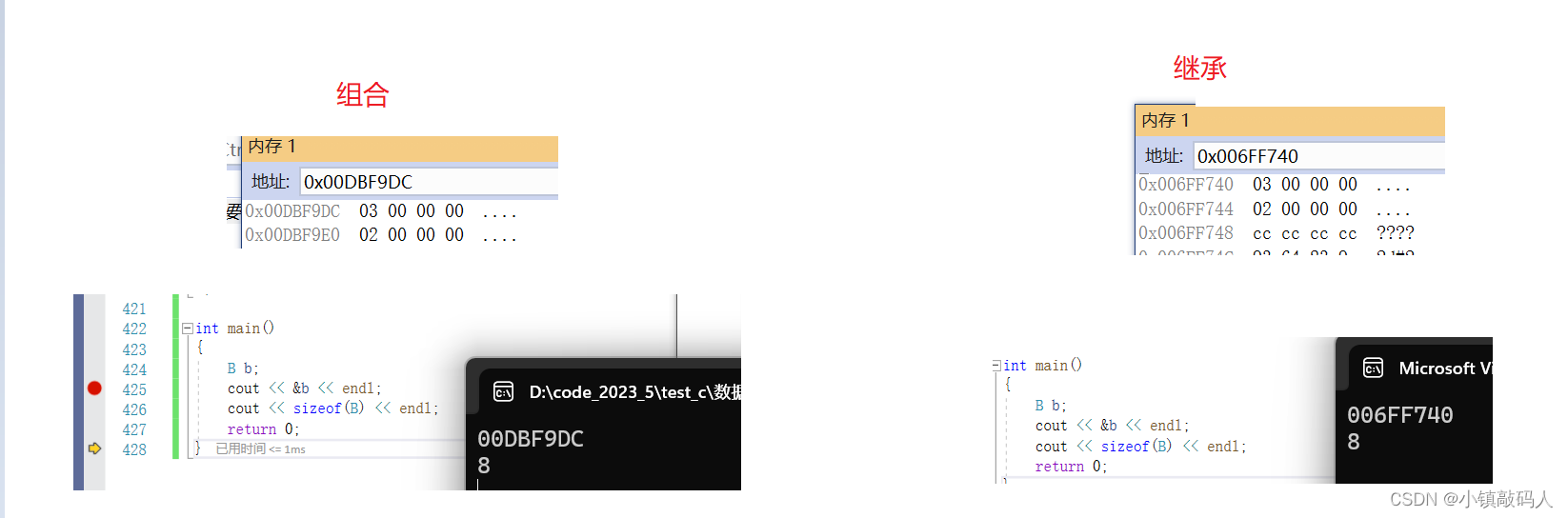

📃博客主页: 小镇敲码人 💚代码仓库,欢迎访问 🚀 欢迎关注:👍点赞 👂🏽留言 😍收藏 🌏 任尔江湖满血骨,我自踏雪寻梅香。 万千浮云遮碧月,独傲天下百坚强。 男儿应有龙腾志,盖世一意转洪荒。 莫使此生无痕度,终归人间一捧黄。🍎🍎🍎 ❤️ 什么?你问我答案,少年你看,下一个十年又来了 💞 💞 💞 【C++继承解密】:构建层次化设计的艺术 ♊️ 继承

深入解析MySQL的层次化设计

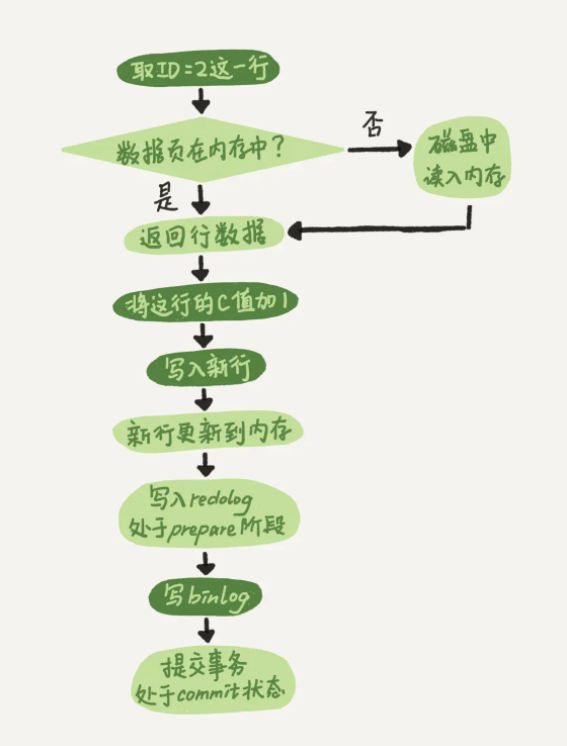

一、基础架构 1.连接器 1.会先连接到这个数据库上,这时候接待你的就是连接器。连接器负责跟客户端建立连接、获取权限、维持和管理连接 2.用户密码连接成功之后,会从权限表中拿出你的权限,后续操作权限都依赖于此时拿出的权限,这就意味着当链接完成之后即使有人修改了你的用户权限,也不会影响你先有的链接 3.长连接是指连接成功后,如果客户端持续有请求,则一直使用同一个连接。短连接则是指每

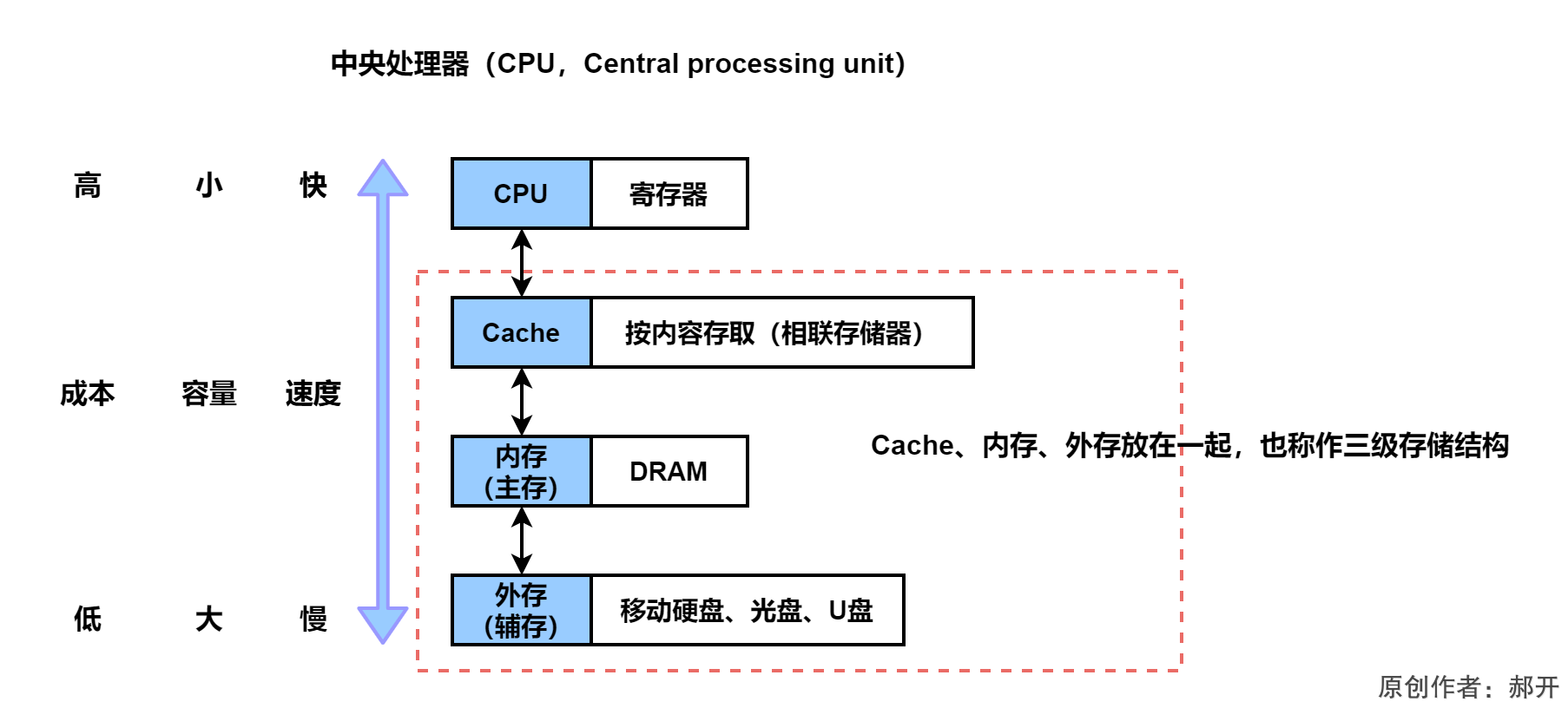

软设之层次化存储体系

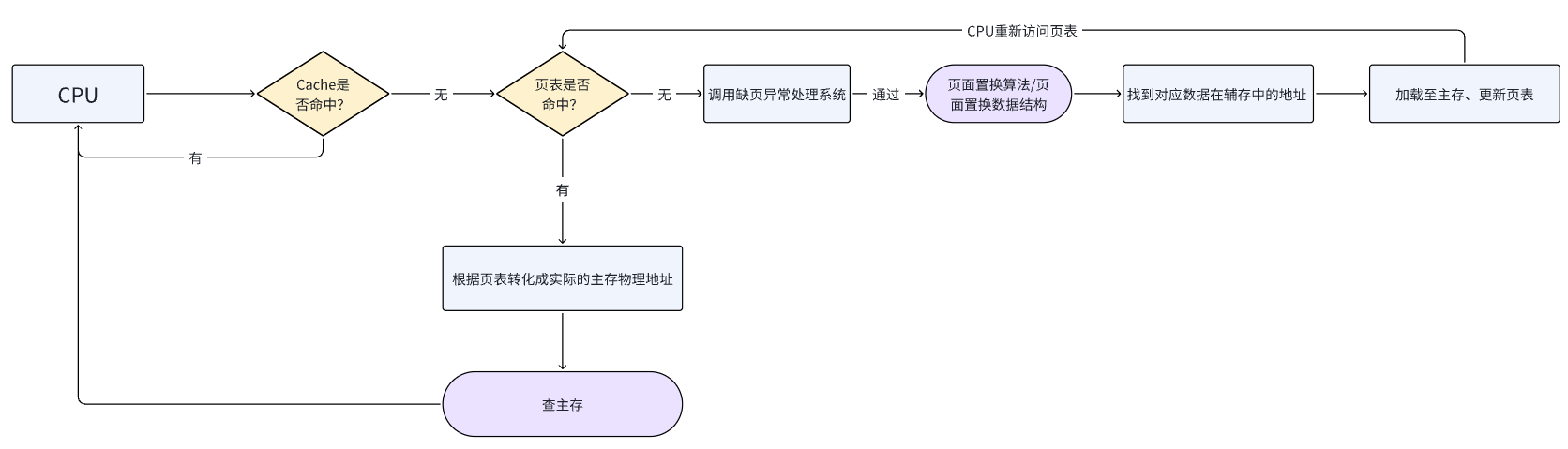

存储结构按照速度排名,由快到慢,分别是cpu,cache,内存,外存。成本也是在相应升高。 层次化存储理论依据是局部性原理,分别是时间局部性,空间局部性。 时间局部性:刚被访问的内容,立即又被访问 空间局部性:刚被访问的内容,邻近空间很快被访问。 存储器分类 按照存储位置分为内存和外存 存取方式 按内容读取,相联存储器 按地址读取 随机存储器,比如说内存 顺

空间的艺术——展平式设计与层次化设计

所有芯片的设计跟普通的产品一样,需有一个标准规范化的流程(flow)。然后工程师们按照流程,运行和调试参数来得到一个合格的结果。 随着EDA软件的不断发展,新的技术不断涌现,flow的选择性也呈现出多元化的趋势。所以了解新知识,新技术对于我们来说,是相当有必要的。 从设计的大方向上讲,flow分为传统的展平式设计(flat flow)和层次化设计(hierarchical flow)。展

postgresql树形结构层次化叠加查询

postgresql树形结构层次化叠加查询 实验环境 操作系统:windows 10 家庭中文版数据库系统: PostgreSQL 9.6.2 场景说明 业务场景碰到这样一种情况,在一张树形结构的表格中(区域结构表),需要从子节点到根节点依次叠加。 例如: Created with Raphaël 2.1.2 树形结构示例 中国=a

pandas的层次化索引

一、层次化索引 层次化索引(hierarchical indexing)是pandas的一个重要的功能,它可以在一个轴上有多个(两个以上)的索引,这就表示着,它能够以低维度形式来表示高维度的数据。 二、Series的层次化索引 # Series的层次化索引,索引是一个二维数组,相当于两个索引决定一个值# 有点类似于DataFrame的行索引和列索引s = Series(np.ar

Cadence层次化设计-用与非门和反相器构成振荡器

Cadence层次化设计-用与非门和反相器构成振荡器 与非门电路原理图创建与非门symbol与非门版图用之前的反相器和上面的与非门做振荡器仿真画振荡器版图后仿真结果 与非门电路原理图 第二个pmos的输入用的是label来连接输入B。按L即可创建label 注意M0的衬底电位 创建与非门symbol 与非门版图 我出错的点:没根据管子宽长来设置active的宽度;没画

使用层次化设计方法设计简易电子钟(VHDL描述)

文章目录 前言一、如何设计简易电子钟?二、具体实现1.设计分频器2.设计小时计数器(24进制)3.分钟和秒计数器的设计4. 动态数码关显示控制模块4.顶层设计 关于如何生成器件和器件使用及其他1.生成器件:2.器件的使用3.其他 前言 简易的电子钟可用于24时计数。建议电子钟是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1

SystemVerilog语法中,在Class中引用层次化信号

在class中可以像在verilog中一样,直接在class中引用层次化信号。示例如下: 1.DUT模块,文件名为top.v。 module top(input clk ,input rst_n ,//总线信号 input wr_n ,input rd_n ,input cs0_n ,input cs7_n ); 2.cpu类,

1.2.1存储结构:层次化存储结构、外存(辅存)、内存(主存)、CPU内部的寄存器、Cache(相联存储器)

1.2.1存储结构:层次化存储结构、外存(辅存)、内存(主存)、CPU内部的寄存器、Cache(相联存储器) 存储系统--层次化存储结构外存(辅存)内存(主存)CPU内部的寄存器Cache(相联存储器) 这么多的存储结构,作为一个程序员来看的话,可以操作那些内容呢? 存储系统–层次化存储结构 整个层次化存储系统划分,每一个存储系统里面会有多种存储器,这些存储器可以分层,各个层

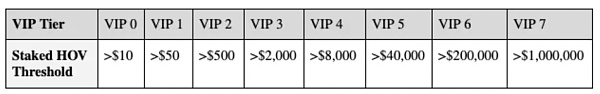

解读非托管流动性协议Hover: 差异化、层次化的全新借贷体系

“Hover 是 DeFi 借贷赛道的另辟蹊径者,除了在自身机制(借贷模型、治理体系)上进行创新获得内生动力外,背靠日渐繁荣的 Kava、Cosmos 生态进一步获得外生动力,发展潜力俱佳” 与 DEX 类似,借贷也是 DeFi 世界中最重要的基础板块之一,它也承担着链上流动性、价值传动的重任。链上借贷赛道最早可追溯到 2017年的ETHLend(AAVE的前身),它是以太坊上第一个去中心化