分频器专题

INVS 对时钟二分频器(reg-clkgen)的理解和处理

在时钟树的设计中,有很多方式处理分频时钟,常见的无外乎两种模式: 时钟二分频器(reg-clkgen)门控时钟 二者在功能上略有不同,比较的大差异是前者可以简单的实现50%占空比,后者却对功耗友好同时降低了实现难度。这里结合INVS在CTS的手法,一起了解一下INVS对二者的处理差异。闲言少叙,ICer GO! 就后端工具而言,CTS是其三大引擎之一,在当下设计的高工艺、高性能的背景下,

预分频器×重装载值)/LSI频率 为什么等于总时间

1. 第一种算法理解:分频系数 64 ,外部低速时钟40khz, 则一次计数周期1.6ms ,计数625个数,则有625个周期 ,1.6ms*625 等于1s 如果分频系数是64,外部低速时钟(LSI)频率是40kHz,那么每个计数周期的时间是1.6ms,因为: 1 / (40kHz / 64) = 1 / (40000 / 64) = 1 / 625 Hz = 1.6 ms

Verilog手撕代码(6)分频器

目录 分频概念偶数分频二分频任意偶数占空比问题 奇分频非常规占空比的奇分频 分频时钟的使用小数分频 分频概念 分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。 再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。 如图为四分频波形图,clk_o

FPGA【Verilog分频器】

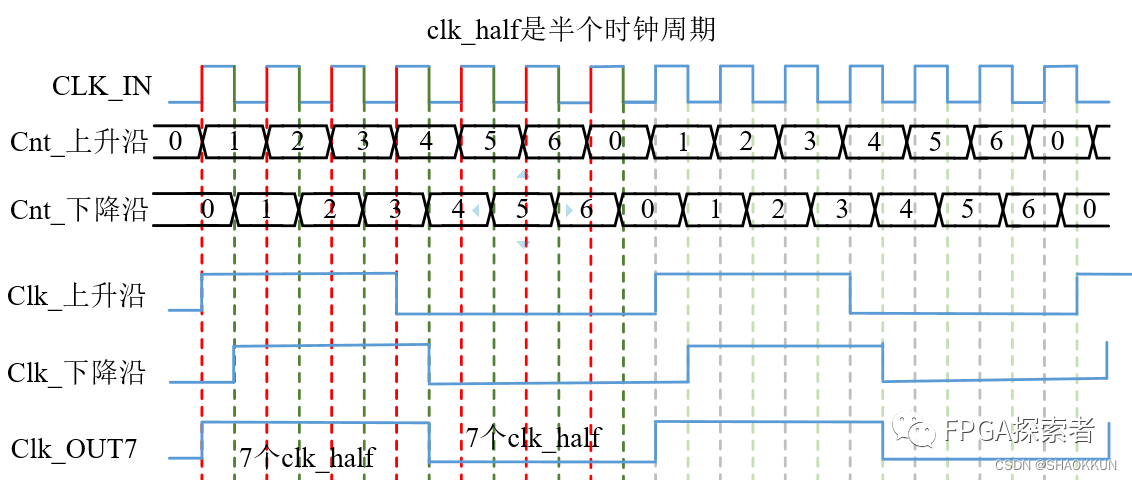

在数字系统的设计中经常会碰到需要使用多个时钟的情况。时钟信号的产生通常具有两种方法,一种是使用PLL(Phase Locked Loop,锁相环),可生成倍频、分频信号;另一种则是使用硬件描述语言构建一个分频电路。 分频器的设计通常分为以下三类:奇数分频器、偶数分频器及小数分频器。 1.偶数分频 只是注意时钟翻转的条件是(N/2)还是(N/

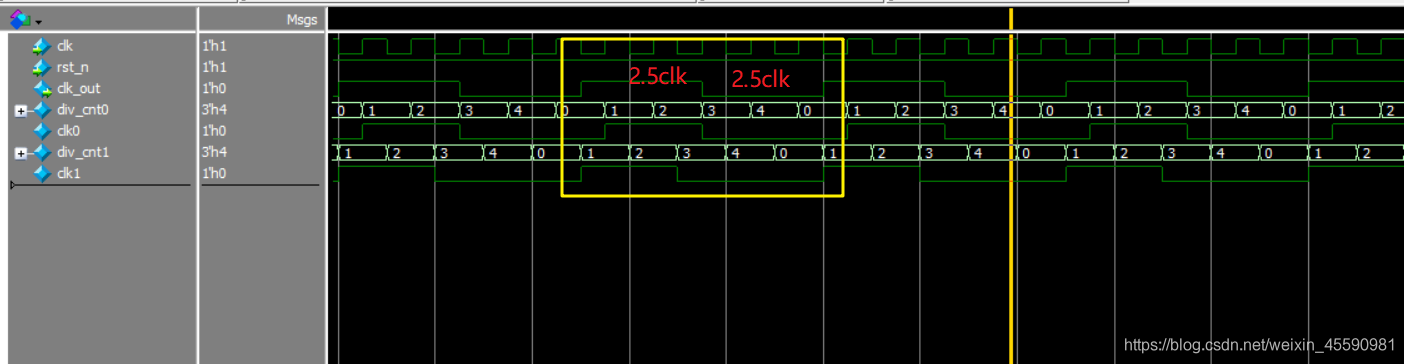

FPGA奇数和偶数分频器和半整…

原文地址:FPGA奇数和偶数分频器和半整数及任意小数分频器设计(Verilog程序) 作者:SUN_403 Author: ---Engineer Lhrace 1、半整数分频占空比不为50% //说明:设计的史上最好用的半整数分频占空比不为50%,包含设计思路 module div_5(clk,clk_div,cnt1,cnt2,temp1,temp2);//N+0.5 input

Verilog实现分频器时,计数注意事项

本来我是想设计一个四分频,但是结果却是六分频? 后来仔细分析了一下波形后,发现这是时序电路 代码: module fenpinqi(clk, clr, q0, state);input clk, clr;output reg q0;output reg [1:0] state;always@(posedge clk)begin if(clr) begin q0 <= 0; state <=2

【【萌新的FPGA学习之分频器的介绍】】

萌新的FPGA学习之分频器的介绍 分频器的介绍 分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。但是奇数分频会比偶数分频复杂一些。 实现分频一般有两种方法,一种方法是直接使用 PLL 进行分频,比如在 FPGA

【【萌新的FPGA学习之分频器的介绍】】

萌新的FPGA学习之分频器的介绍 分频器的介绍 分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。但是奇数分频会比偶数分频复杂一些。 实现分频一般有两种方法,一种方法是直接使用 PLL 进行分频,比如在 FPGA

分频器 偶分频 奇分频 任意分频

今天学习了一下分频器及其Verilog实现 1.偶分频 实现一个NUM_DIV分频的分频器,下面代码中 NUM_DIV= 6,占空比50% 设计代码 module divider_even(clk,rst_n,clk_div);input clk;input rst_n;output clk_div;reg clk_div;parameter NUM_DIV = 6;reg [3:

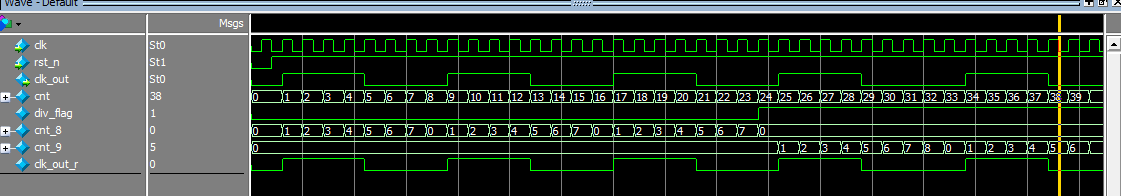

verilog基础设计4-偶数倍及奇数倍分频器的实现

抽空写一下奇数倍以及偶数倍分频的verilog代码,复习一下 目录 1、偶数倍分频的实现,占空比50% 2、偶数分频tb文件 3、偶数倍分频仿真结果 4、奇数倍分频的实现,占空比50% 5、奇数倍分频tb文件 6、奇数分频仿真结果 1、偶数倍分频的实现,占空比50% 以四分频为例 //占空比50%module div_even_f(input wire clk,in

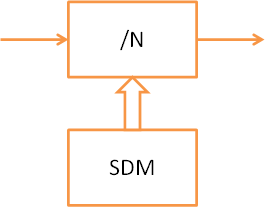

SDM对分频器输出信号相位噪声的影响

SDM是PLL里很重要的一个噪声源,下面分析一下SDM对NDIV输出时钟相噪的影响。 首先,SDM输出信号的噪声是量化噪声的 sdm_order sdm\_order次差分(具体推导暂且不提),而量化噪声是在 [−fclk,+fclk] [-fclk , +fclk]范围内均匀分布,噪声功率为 Δ 2 /12 \Delta^2/12,差分的传函是 1−z −1 1-z^{-1},则