本文主要是介绍预置分频器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

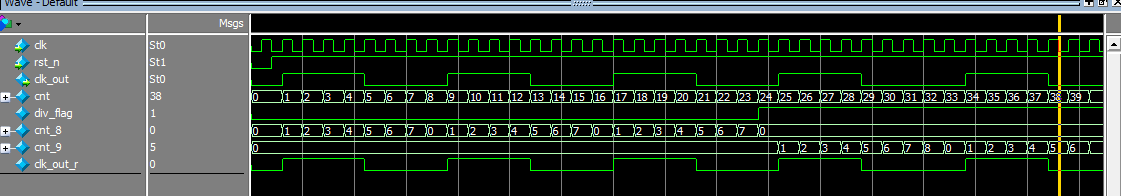

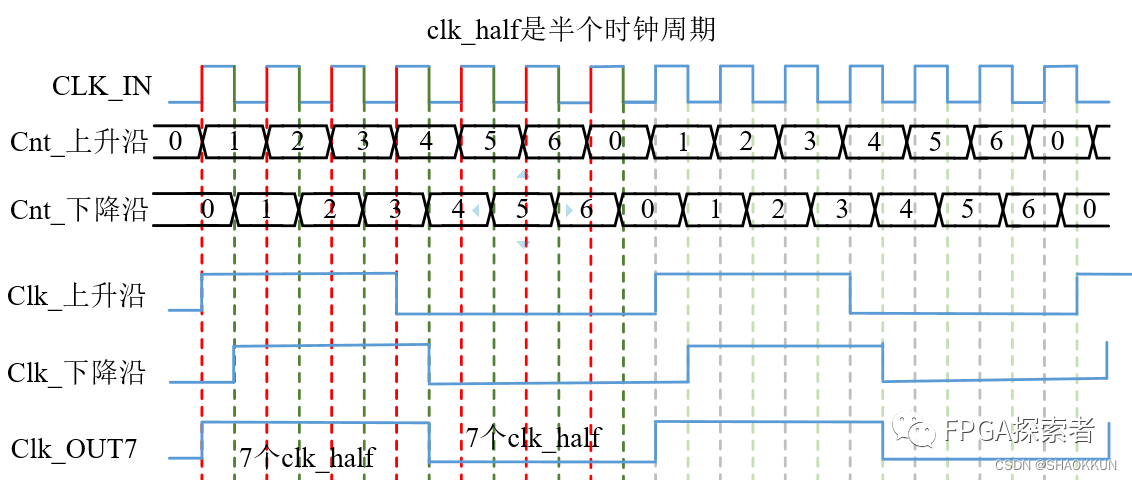

在PLL设计中,会遇到预置分频器的设置,一般有8/9,16/17,32/33等形式,其具体含义为对输入的VCO频率的预分频,如果选择8/9,即对VCO的分频为8或者9在整个计数周期内交替分频,P/(P+1)的含义是,如高电平时分频为P,则在低电平时分频为P+1,预分频主要是对频率较高时使用,分频数越大,越适合高频率。仅供参考!

这篇关于预置分频器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!