亚稳态专题

野火FPGA跟练(四)——串口RS232、亚稳态

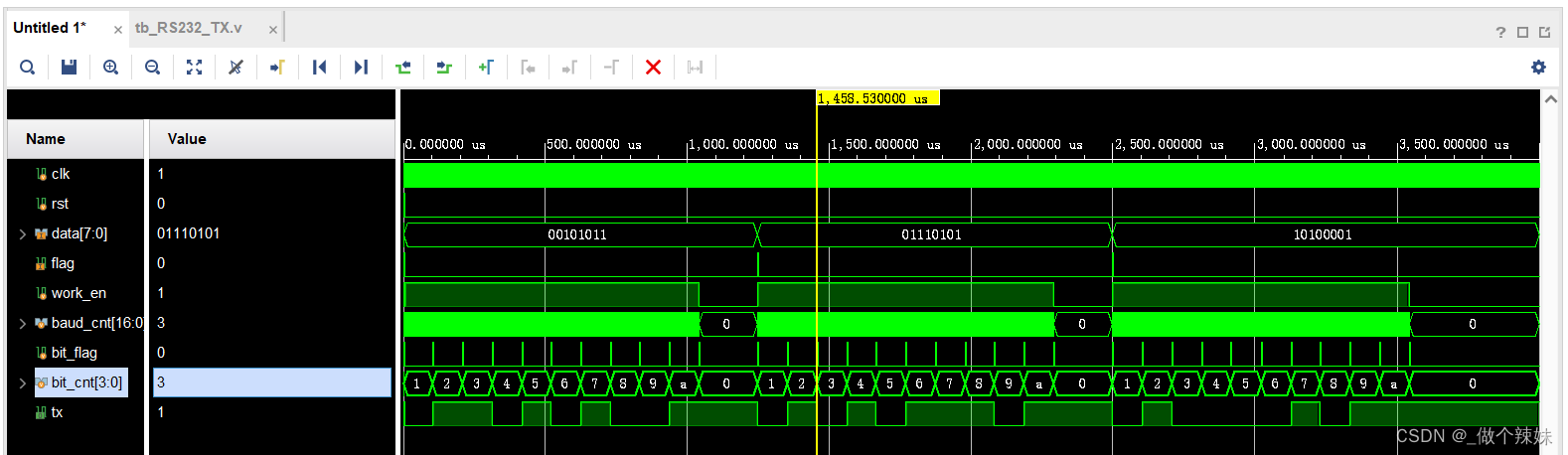

目录 简介接口与引脚通信协议亚稳态RS232接收模块模块框图时序波形RTL 代码易错点Testbench 代码仿真 RS232发送模块模块框图时序波形RTL 代码Testbench 代码仿真 简介 UART:Universal Asynchronous Receiver/Transmitter,异步串行通信接口。发送数据时并行转串行,接收数据时串行转并行。RS232:UAR

亚稳态和毛刺 - Metastability and Hazard(CN)(二)

我们在芯片设计与调试中,一定曾经遇到过一些诡异的问题。比如芯片的某一部分莫名其妙的复位却并没有故障记录、比如有的问题上下电和复位表现不一。甚至在有的FPGA项目后期,每一次重布局布线都是对人品的考验,祈祷在下一个版本中,Voldemort不会出现。根本原因是多方面的,但是不难发现亚稳态和毛刺的影子。 幸运的是,这些问题难以定位但容易在设计中避免,只需我们在设计中稍加关注即可避免。任何一个成熟

如何解决亚稳态(三)

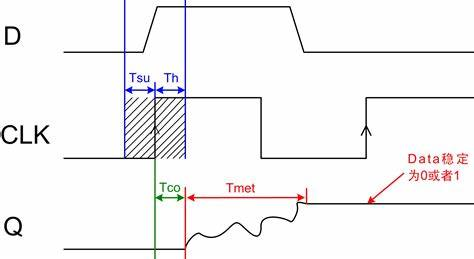

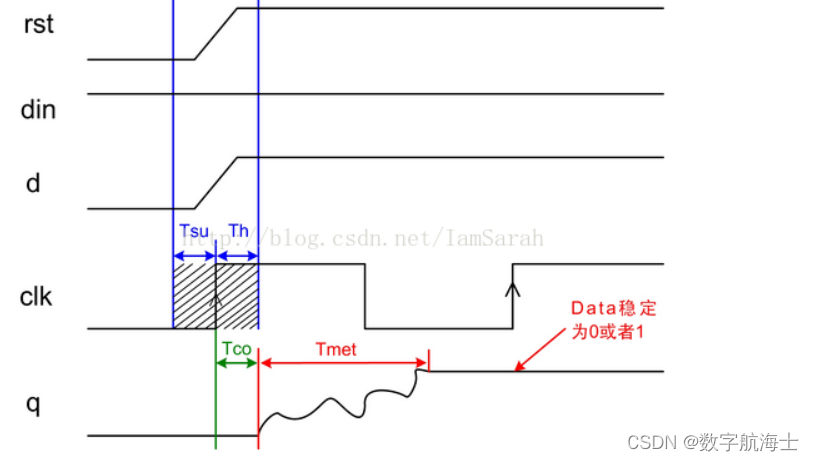

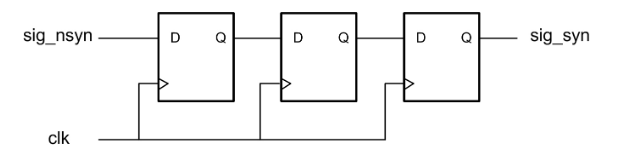

如何解决亚稳态: 亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。 解决方法: 1 降低系统时钟; 2 用反应更快的触发器; 3 引入同步机制,防止

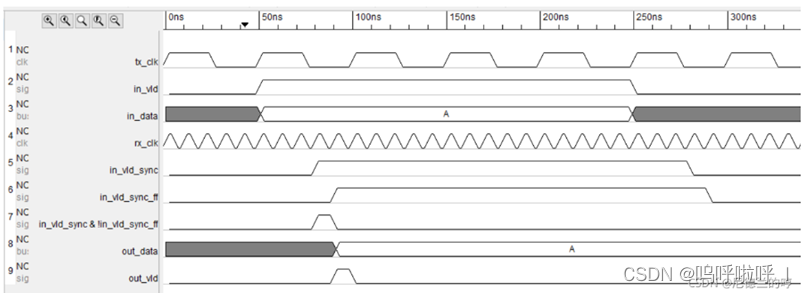

异步时钟域的亚稳态问题和同步器(四)

Metastability in the asynchronous clocks and Synchronizer 摘 要:相较纯粹的单一时钟的同步电路设计,设计人员更多遇到的是多时钟域的异步电路设计。因此,异步电路设计在数字电路设计中的重要性不言而喻。本文主要就异步设计中涉及到的亚稳态问题,作简要介绍,并提出常用的解决办法——即同步器的使用。 关键词:异步电路设计、亚稳态、同步器。 Abstra

关于数字电路中的亚稳态(一)

1)亚稳态定义 亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去 亚稳态这个点并不是真正的稳定,因为随机的躁声会驱使工作与亚稳态点的电路转移到一个稳定的

新芯计划(0)同步设计——亚稳态

系列文章目录 文章目录 系列文章目录前言一、亚稳态是什么二、亚稳态概率 前言 马上成为新ICer,利用空闲时间展开对自己的首轮培训,取名为”新芯计划“哈哈哈 这个系列主要给自己做个基础知识的巩固,本节的内容围绕亚稳态展开,如若有内容有误,欢迎和感谢各位指正 参考文章:MTBF 是如何指导跨时钟域设计的 一、亚稳态是什么 亚稳态发生于 : 输入数据不满足时钟的建

数字IC/FPGA——亚稳态及跨时钟域

什么是亚稳态亚稳态会造成什么平均故障间隔时间如何解决亚稳态同步时钟和异步时钟单bit电平信号如何跨时钟域单bit脉冲信号如何跨时钟域多bit信号如何跨时钟域 目录 一、亚稳态1.基本概念2.危害3.平均故障时间4.解决亚稳态的方法 二、跨时钟域1.同步电路和异步电路(1)同步电路(2)异步电路 2.单bit跨时钟域(1)电平信号(2)脉冲信号 3.多bit跨时钟域(1)格雷码(2)DMUX

FPGA亚稳态学习总结

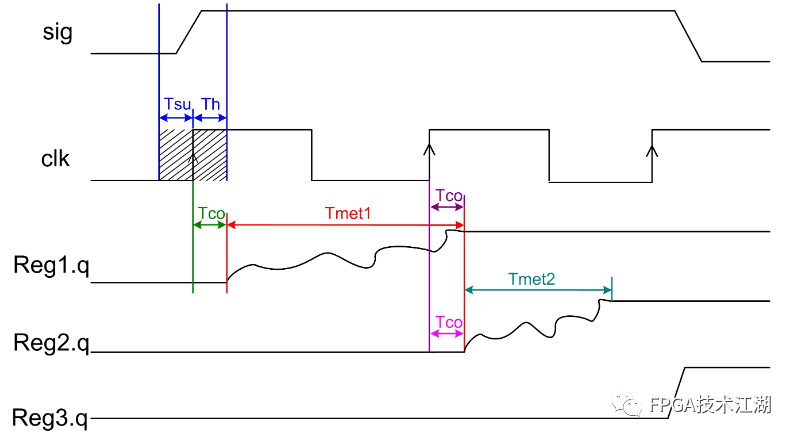

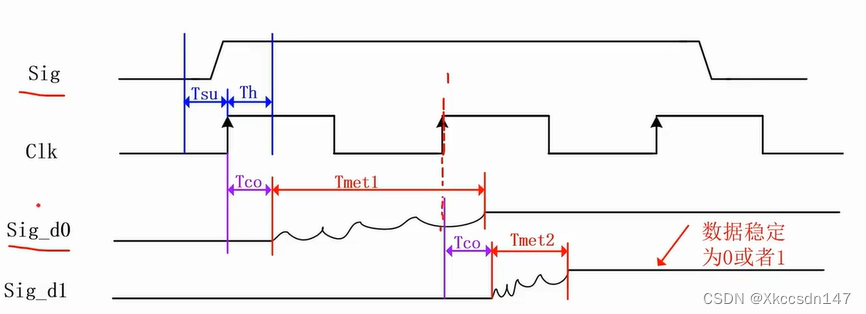

首先是组合逻辑电路考虑的是竞争冒险,冒险会产生毛刺。重点研究如何去毛刺 时序逻辑电路考虑的是时序不满足会产生的亚稳态问题:如何考量时序满不满足呢?根据不同的场景又有不同的说法。 时序分析的两组基本概念 建立时间与保持时间 1.在同步系统和异步系统(跨时钟域传输)中有两个时间概念:建立时间、保持时间。 触发器在时钟上升沿来临时对数据进行采样,产生对应的输出。但是实际器件无法瞬时完成数据采

今日说“法”:让FPGA设计中的亚稳态“无处可逃”

今日说“法”:让FPGA设计中的亚稳态“无处可逃” 欢迎大侠来到FPGA技术江湖新栏目今日说“法”,当然,在这里我们肯定不是去研究讨论法律法规知识,那我们讨论什么呢,在这里我们讨论的是产品研发以及技术学习时一些小细节小方法等,欢迎大家一起学习交流,有好的灵感以及文章随笔,欢迎投稿,投稿请标明笔名以及相关文章,投稿接收邮箱:1033788863@qq.com。今天带来让FPGA设计中的亚稳态“无处

数字电路的亚稳态问题

数字电路的亚稳态问题 亚稳态的原因:何时会发生亚稳态:亚稳态危害:异步复位的亚稳态同步复位的亚稳态亚稳态发生概率亚稳态振荡时间Tmet常用的消除亚稳态的三种办法 🔈声明: 🔑未经作者允许,禁止转载 🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧👈 亚稳态问题是数字电路中很重要的问题,因为现实世界是一个异步的世界,所以亚稳态

16 亚稳态原理和解决方案

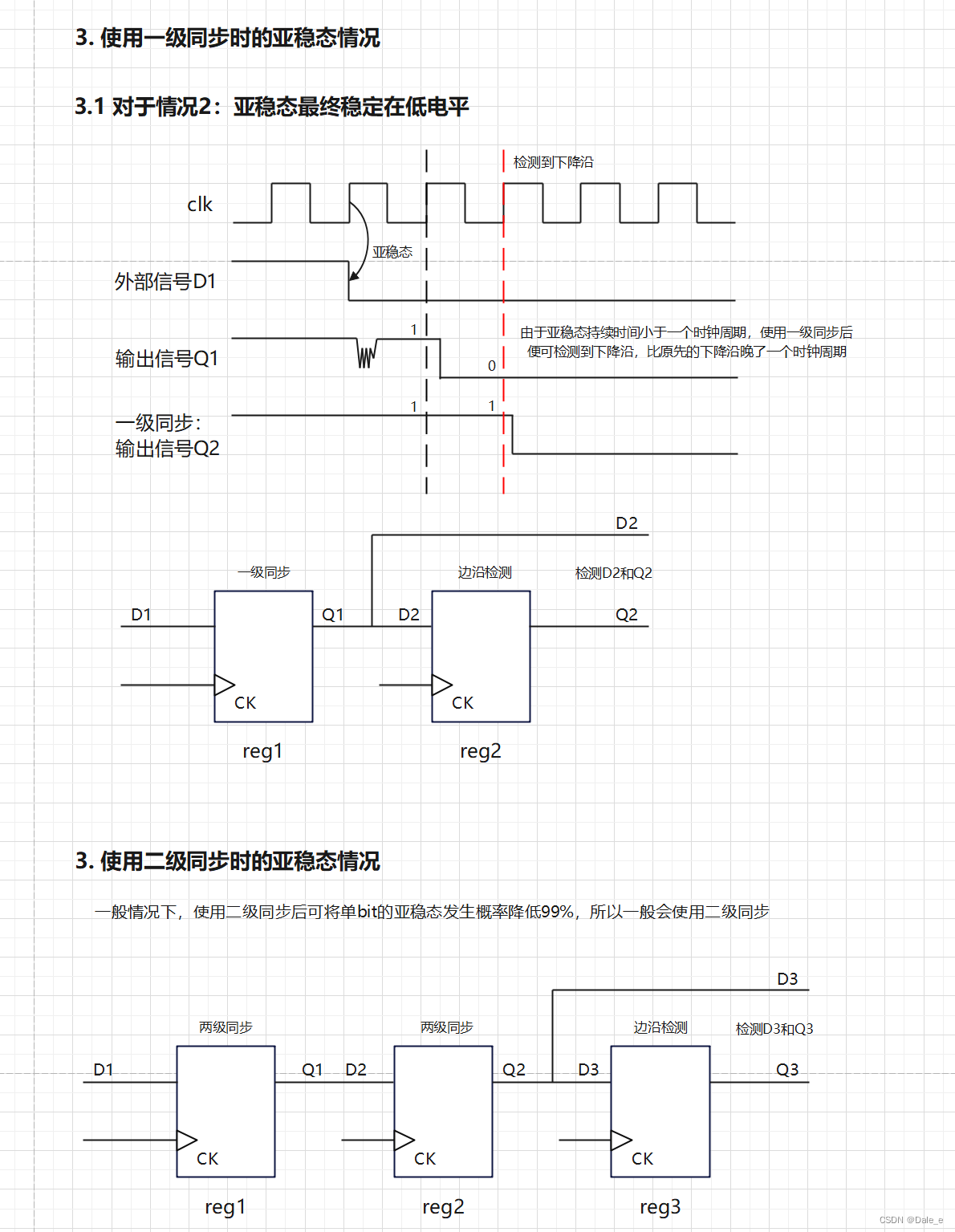

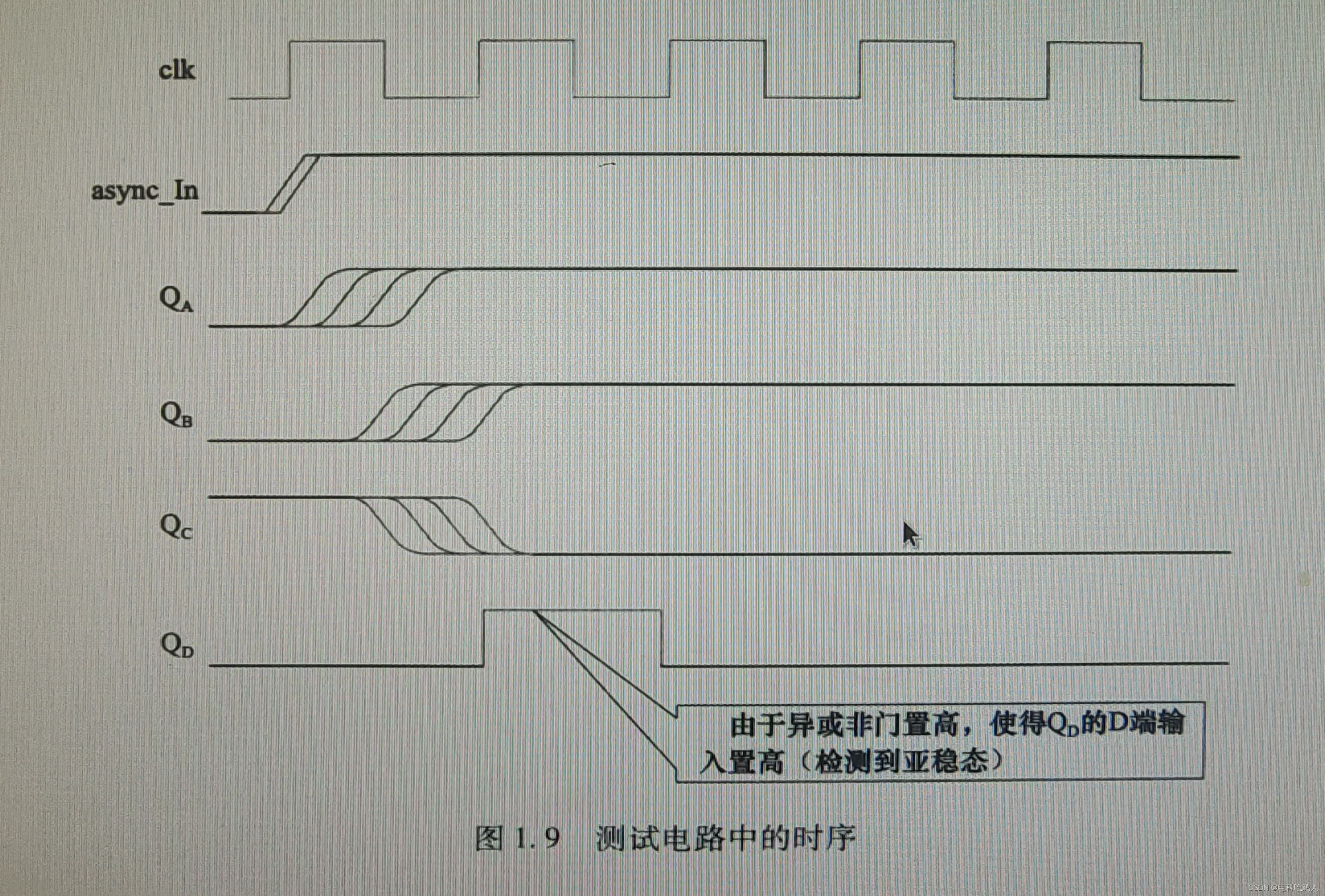

1. 亚稳态原理 亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。在同步系统中,输入总是与时钟同步,因此寄存器的setup time和hold time是满足的,一般情况下是不会发生亚稳态情况的。在异步信号采集中,由于异步信号可以在任意时间点到达目的寄存器,所以无法保证满足目的寄存器Tsu和Th的要求,从而出现亚稳态 2. 异步信号用于边沿检测时出现亚稳态的波形分析 以外部

异步时钟亚稳态 的解决方案——多bit信号

目录 1. 时钟偏斜 导致的采样中间值问题2. Gray码循环单bit翻转 编码方式 3. 同步使能 validavalid 最小持续时间 和 最小时间间隔 3. 异步FIFO FPGA 设计之 跨时钟域(三 - 多比特小结) FPGA 设计之 跨时钟域(四 - 格雷码) FPGA 设计之 跨时钟域(六 - 握手) 同步valid&ready握手 与 异步valid&ac

异步时钟亚稳态 的解决方案——单bit信号

目录 1. 亚稳态问题——电平同步1.1. 采样电压过低1.2. “3个沿”rd_en_d2 拉高的时刻 1.3. 产生脉冲——边沿检测 2. 漏采样——展宽2.1. 异或展宽两个连续脉冲 的最小间隔 2.2. 异或握手展宽两个连续脉冲 的最小间隔异或展宽 与 异或握手展宽 异步电路导致亚稳态的根本原因是跨时钟域导致建立、保持时间不满足,导致采样之后的信号在较长时间处于逻辑

数字电路时序学习:(一)亚稳态

书籍《硬件架构的艺术:数字电路的设计方法与技术》 (一) 亚稳态 1.1 概念 由于违反触发器的建立时间和 保持时间 而产生的 在时钟的上升沿的窗口内,数据发生变化,输出未知或称为亚稳的 亚稳态窗口 亚稳态窗口 - 窗口越大,进入亚稳态的概率越高 1.2 危害 输出产生毛刺 暂时保持不稳定状态而且需要较长时间才回到稳定状态 一般需要1~2个时间周期才能返回稳态

异步时钟亚稳态 的解决方案——多bit信号

目录 1. 时钟偏斜 导致的采样中间值问题2. Gray码循环单bit翻转 编码方式 3. 同步使能 validavalid 最小持续时间 和 最小时间间隔 3. 异步FIFO FPGA 设计之 跨时钟域(三 - 多比特小结) FPGA 设计之 跨时钟域(四 - 格雷码) FPGA 设计之 跨时钟域(六 - 握手) 同步valid&ready握手 与 异步valid&ac

与FPGA中亚稳态的‘量子纠缠’

亚稳态 说实话,这玩意我也是琢磨许久,不搞懂心里难受!!!这也让我觉得匪夷所思的地方!!! 这玩意不搞懂,我是睡不着觉的!!!! 为啥会出现亚稳态?组合逻辑有吗?组合逻辑是靠电平触发,每次会有确定的电平值0或1,但组合逻辑会有个竞争冒险现象,这个现象与亚稳态一样是个小祸害,阻碍整个系统变得优秀!!!(我这说的委婉,可能会导致系统奔溃) 那么在时序逻辑中呢?这涉及到很重要的数字器件,那