本文主要是介绍关于数字电路中的亚稳态(一),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1)亚稳态定义

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去

亚稳态这个点并不是真正的稳定,因为随机的躁声会驱使工作与亚稳态点的电路转移到一个稳定的工作点去。

正如山顶的球一样,双稳态电路在不确定进入某一种状态之前,可能会在亚稳态停留一段不可预测的时间。

2)锁存器的亚稳态

(1)R_S锁存器,加在S输入端的脉冲会使锁存器的状态0变到1状态。

对S输入端有一个最小脉冲宽度的限制。若所加脉冲的宽度与这个宽度限制更宽的话,锁存器的状态立即变为一状态。若小于这个限制脉宽就可能进入亚稳态。一旦进入亚稳态之后,他的行为就取决与“山的形状”了。用高增益,快速工艺制作的锁存器和触发器会比用低性能工艺制造的更快地脱离亚稳态!

(2)如果R_S都为1,则输出都被强制为0。一旦取消某一输入,则两个输入有重回复到通常的互补状态。但是,两个输入同时消失,则锁存器将进入一个不可预测的状态,而事实上这个状态可能是震荡状态或者是亚稳态!如果加在S或R端的“1”脉冲太短,也可能引起亚稳定性!

(3)尽管D锁存器消除了R-S锁存器的S=R=1的问题(清零置1同时有效),但是亚稳态的问题依然存在。如果在建立保持时间窗内信号发生变化的话,锁存器的输出就是不可预测的,并且可能进入亚稳态。

(4)触发器的亚稳态

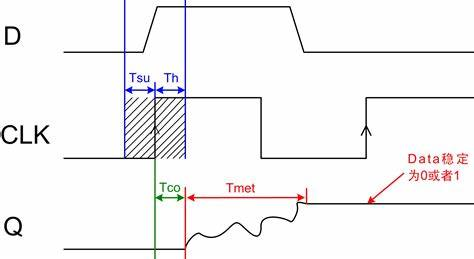

像D锁存器那样,边沿触发器D触发器也存在着一个建立和保持时间窗,在这段时间内D端的输入一定不能变化。在这一窗口时间也是在CLK信号的触发沿附近,若未能满足建立和保持时间的要求,触发器的输出通常会进入一个稳定状态。尽管这个状态不可预知,但他不是0就是1。但是,有时输出也可能会震荡或者进入亚稳态,或进入一个界于0和1之间的亚稳态,如果触发器进入亚稳态,则它只是在经过一个随机的延时后,才会自己回到一个稳定状态。

在触发器的建立时间和保持时间要求没有得到满足时,触发器就会进入一个界于状态1与状态0之间的第三种状态,即亚稳态状态。

最糟糕的是,理论上讲,门电路个触发器接受到这个亚稳态的输入信号之后,有些部件会把这个信号当成0,而另一些则把它当1,于是会产生不一样的输出,或者,还有一些门电路和触发器本身也可能产生亚稳态的输出信号(毕竟,这些器件现在都工作在其工作区的线性部分)。幸运的是,尽管触发器的输出保持亚稳态的可能性永远也不会为0,但这种可能性随着时间呈指数的下降趋势!

使触发器脱离亚稳态有两种方法:

1):利用满足最小脉宽宽度,建立时间等规定的输入信号,迫使触发器进入一个有效的逻辑状态。

2)等待足够长的时间,以便触发器自己脱离亚稳态状态。

亚稳定性分辨时间

如果满足了D触发器的建立和保持时间要求,那么在时钟沿到来后的Tpd时间(传播延迟)内触发器就会稳定在一个新的输出值上。如果没有满足D触发器的建立保持时间要求,触发器的输出就会进入亚稳态,并保持随机长的时间。在特定的系统设计中,我们用一个参数Tr(称为亚稳定分辨时间),来表示在不引起同步器故障的情况下,输出会停留在亚稳态的最大时间。

有效的亚稳态分辨时间:

Tr=Tclk(时钟周期)-Tcomb(组合逻辑的传播延迟)-Tsetup

Tpd时间(传播延迟):输入信号变化到产生输出信号变化所需的时间。

最可靠同步器设计

最可靠的同步器就是具有最大亚稳定性分辨时间的同步器。但是,在数字系统的设计中,我们不仅很少因为系统的可靠性而奢侈地降低时钟频率,而且为了让系统具有更好的性能还常常要求提高时钟频率。因此,通常需要能够在很短的时钟内可靠工作的同步器。

Tr=Tclk-Tcomb-Tsetup

速度越快的触发器建立时间就越短。Tcomb(组合逻辑的传播延迟)最小值为0;

用两级D触发器构成同步器,时钟异步信号输入DFF1,这个信号可能会违反触发器的建立时间和保持时间的规定。一旦发生这种情况。输出信号就会进入亚稳态,而且这个状态停留一个任意长的时间。然而,我们已经假设在时钟沿之后,亚稳定性保持的最长时间为Tr(称为亚稳定分辨时间)。只要时钟周期比Tr与DFF2的建立时间之和要大,那么从下一个时钟触发沿开始,DFF2的输出信号就是异步信号(DFF的输入信号)的同步拷贝,而且不会进入亚稳态。于是就可以把DFF2的输出信号(时钟异步信号)分发到系统的其余部分!

通过两极触发器其实就是给亚稳态足够的脱离时间,以便信号稳定后再采样!

原文地址:http://www.xmu123.com/2503/viewspace-34377.html

这篇关于关于数字电路中的亚稳态(一)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!