zedboard专题

在ZedBoard开发板上部署Node.js(v6.2.0)服务

在ZedBoard开发板上部署Node.js服务 本次部署环境为ZedBoard开发板Armv7l(32位)linux Ubantu 12.04 源文件下载 官网已编译文件下载 Node.js v6.2.0 armv7l 源文件部署 解压缩 $xz -d ***.tar.xz$tar -xvf ***.tar 修改文件夹名 mv *** node 添加环境变量 expo

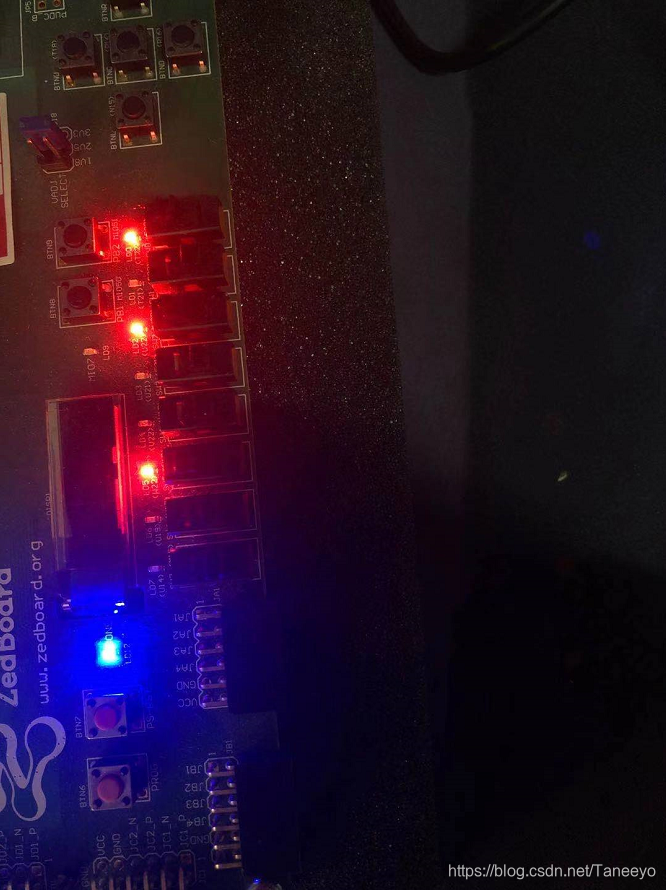

zedboard如何从PL端控制DDR读写(六)

上一节说到了DDR寻址的问题,如下图: 从官方文档上我们看到了DDR的地址是从0008_0000开始的,那么我们开始修改Xilinx给我们提供的IP核代码。其实很简单,上一节已经分析了地址停留在0000_1000的原因,现在我们只需要把write_burst_counter的位宽变大就可以了。 从上表看到地址范围由全0到全1,计算一下就知道需要的宽度为27,即 C_NO_B

zedboard如何从PL端控制DDR读写(四)

PS-PL之间的AXI 接口分为三种: • 通用 AXI(General Purpose AXI) — 一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。 • 加速器一致性端口(Accelerator Coherency Port) — 在 PL 和 APU 内的 SCU之间的单个异步连接,总线宽度

zedboard如何从PL端控制DDR读写(三)——AXI-FULL总线调试

本文主要是总结一下使用AXI-FULL调试的过程。 首先想到的是用RAM IP核来测试,方法是通过AXI接口向RAM写入一组数据并读出,看起来很简单,然而试了好久都没能出结果。如下图所示,其实AXI RAM就是在本地RAM接口的基础上套了一个AXI的壳 在使用modelsim仿真的时候总是会抛出一个警告,具体的警告类型忘了,下次有机会再尝试。试了好多次都这样,

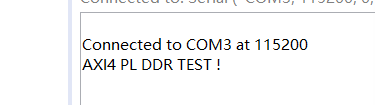

Zedboard 如何从PL端控制DDR3(二)--AXI4总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的。 AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3

【ZYNQ 详细案例二】VGA显示的详细实现与原理分析 彩条实验 基于ZEDBOARD

【ZYNQ 详细案例二】VGA显示的详细实现与原理分析 彩条实验 基于ZEDBOARD 首先我们来看看Zedboard用户手册和数据手册上对于其VGA端口的定义 可知由以上的信息我们得到。VGA显示信号由以下部分组成: 1、RGB444的数据值 2、VGA-HS: VGA行同步信号 3、VGA-VS: VGA场同步信号(列同步) 行同步有效说明一行扫描完了,到达下一行开始扫描‘场同步信号

【ZYNQ 详细案例一】GPIO读写的详细实现 基于ZEDBOARD

【ZYNQ 详细案例一】GPIO的认识与实现 基于ZEDBOARD GPIO是一种外设,可用于连接。。 首先先点击【Block Design】 然后添加处理器IP,也就是我们的ps部分。 双击打开之后,点击【Run Block Automation】,因为在创建工程时,我们已经选择了板子的型号。所以点这个自动配置,就会按照我们选择的板子型号进行一个默认的初始化。 默认点击【OK】即可。

【Zedboard HDMI bug解决】Please specify VLNV when creating IP cell axi_hdmi_dma

出这个bug就是有IP核没有加进去。 那么你的ADV7511应该用的是新版的。 老版本需要编译的IP: hdl-hdl_20xx /library/axi_clkgen hdl-hdl_20xx /library/axi_hdmi_tx hdl-hdl_20xx /library/axi_i2s_adi hdl-hdl_20xx /library/axi_spdif_tx hdl-hdl_20x

【Zynq bug】在SDK Terminal串口打印少了第一个字符 基于Zedboard

在printf之前,加上一个Xil_DCacheDisable();函数即可。 相关头文件 #include "stdio.h"#include "xil_cache.h" 结果就不会吃字节了: 原理是缓存上的问题,哪天有空补写一下。

【zedboard串口bug最终解决办法】zynq开发 在SDK 终端Teminal找不到COM3、COM5等接口 无法连接uart串口 ZYNQ驱动问题 解决办法

在SDK编写好代码 插上两根连接线,一个是JTAG DEBUG一个是uart串口线。 关于板子上跳帽的配置,如上图我的配置就行。 打开SDK的终端,发现没有 教程或者实例中的 COM5 or COM3 等待接口。 这个时候,打开设备管理器 打开端口 我这个COM4 是装VM虚拟机的时候的一个模拟虚拟串口。所以不是Zynq的。这个时候 我们再看看通用总线控制器。 这个就是Zy

【VIVADO SDK报错最终解决办法】write 0x00100000 error,AP transaction error, DAP status f000002 基于zedboard

要看最终解决办法的往下拉 下面是从bug入手到解决的过程: 先说一下我这边的环境: win10 vivado2018.3 Zedboard (zynq) 在SDK写好了代码: 点击 Run 出现如下的报错。 点击Details 没有太多信息。网上说的很多可能的原因版本: 0.DDR的配置错误 1.硬件上,检查跳帽有没有切换正确(× 无效) 2.PL资源有没有改动、hdf文件是否匹配(

【Zedboard】FPGA边缘提取 图像处理 基于ZYNQ完成 灰度图像 在VGA显示与 边缘提取 二值化 Verilog代码实现

【Zedboard】FPGA边缘提取 图像处理 基于ZYNQ完成 灰度图像 在VGA显示与 边缘提取 二值化 Verilog代码实现 在项目开始到目前为止已经完成了在Zedboard的PL部分即FPGA上的对本视觉系统的所有工作。项目整体Block Design 图如下所示: 实物图: 灰度图显示 边缘提取对比RGB彩色图 (一)、配置摄像头传感器并完成完成图像实时采集: (a)先

6、zedboard之纯PL流水灯实验

基本思想:想着最近在复习一下FPGA开发,准备接个大项目 熟悉工具vivado2021_1,许可2017-2021 芯片厂商 一、首先选择芯片类型 二、约束文件 led_demo.xdc set_property PACKAGE_PIN K17 [get_ports clk]set_property PACKAGE_PIN E17 [get_ports rst_n]set_prope

3、zedboard Linux内核编译

目标是生成zedboard的启动文件首先需要工具和输入文件: Tools Required Xilinx SDK Input Files Required FSBL u-boot uImage uRamDisk.image.gz devicetree.dtb Output Files Produced boot.bin 生成u-boot文件(u-boot) 生成Linux内核镜像文件(zIm

16 、zedboard之纯PL按键实验

实验基本目的:实验手册PL的流水灯,基本流程参考手册; 逻辑代码解析: `timescale 1ns / 1ps//// Company: // Engineer: // // Create Date: 03/11/2020 07:37:12 PM// Design Name: // Module Name: PL// Project Name: // Target Devi

14、zedboard 7020 编译Opencv3.4+Opencv_contrib3.4+DeepSort(软核)

基本问题描述:因为希望使用opencv 附加库的DNN 模块,搞一下深度学习的内容,因为上一篇博客已经自己制作了一个debain系统在zynq7020上,因此在该系统上编译opencv3.4 上,编译过程如下: 1、安装附加库 sudo apt-get install build-essential cmake git pkg-configsudo apt-get install libjp

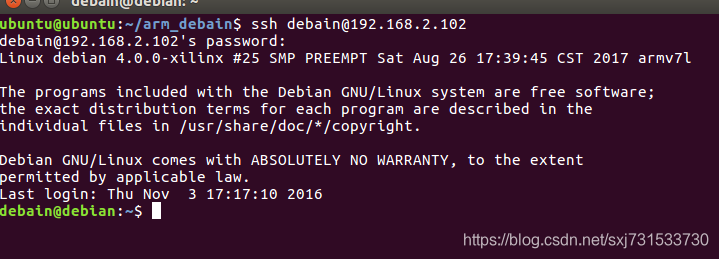

13、zedboard 7020 移植debain 9 系统

基本问题描述:手中有一个zedboard 7020 的开发板,SD一个,官方提供了三个硬件驱动文件BOOT.bin devicetree.dtb uImage 同时提供文件系统inaro-o-ubuntu-desktop-tar-20111219-0.tar.gz &linaro-precise-ubuntu-desktop-20120626-247.tar.gz 不得不提 这文件系统太

zedboard学习资料收集

https://blog.csdn.net/u010134517/article/details/21023593 转自:http://blog.csdn.net/tianhen791/article/details/12657071 以下提供的资料,若未提供链接,直接百度搜索引号里的关键字即可 zedboard-book-source: http://zedboard-book-s

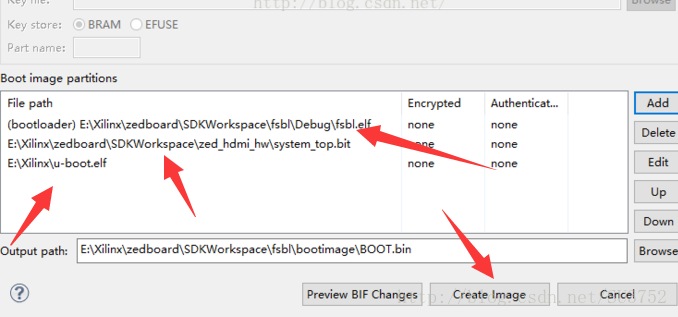

制作ZedBoard-linaro-desktop-ubuntu全过程之编译BOOT.bin

制作ZedBoard-linaro-desktop-ubuntu全过程之编译BOOT.bin 作者:Alston若水 1、准备阶段 (1)目标板子:ZedBoard REV D (2)Ubuntu环境:ubuntukylin-17.04-enhanced-amd64(我安装在了虚拟机下面) (3)xilinx vivado 2015.4 (4)外文参考资料: https://wiki.

制作ZedBoard-linaro-desktop-ubuntu全过程之构建硬件运行环境

制作ZedBoard-linaro-desktop-ubuntu全过程之构建硬件运行环境 作者:Alston若水 1、准备阶段 (1)目标板子:ZedBoard REV D (2)xilinx vivado 2015.4 (3)官网源码https://wiki.analog.com/resources/fpga/xilinx/kc705/adv7511 HDL源码 Ps端测试源码

制作ZedBoard-linaro-desktop-ubuntu全过程之编译Linux内核

制作ZedBoard-linaro-desktop-ubuntu全过程之编译Linux内核 作者:Alston若水 1、准备阶段 (1)目标板子:ZedBoard REV D (2)Ubuntu环境:ubuntukylin-17.04-enhanced-amd64(我安装在了虚拟机下面) (3)下在Linux内核源码:https://g

制作ZedBoard-linaro-desktop-ubuntu全过程之编译u-boot

制作ZedBoard-linaro-desktop-ubuntu全过程之编译u-boot 作者:Alston若水 1、准备阶段 (1)目标板子:ZedBoard REV D (2)Ubuntu环境:ubuntukylin-17.04-enhanced-amd64(我安装在了虚拟机下面) (3)u-boot源文件,https

zedboard REV .D上移植Linaro所出现问题以及一些观点

首先,放上成功启动后串口打印信息,方便有需要者自己看一下是卡在哪一步。 U-Boot 2016.07 (Oct 22 2017 - 21:30:47 +0800) Model: Zynq Zed Development Board Board: Xilinx Zynq DRAM: ECC disabled 512 MiB MMC: sdhci@e0100000: 0 SF:

zedboard axiDMA linux驱动

写在前面的话: 本篇是AXI DMA在linux下使用的例子。 包括PL端设计,基于vivado 2015.4,petalinux 2016.1,基于linux 4.4内核。 我在git hub 上托管了代码,https://github.com/shichaog/zynq-dma,如果想加入github上这个项目,给我邮箱发信息shichaog@126.com,方便为你配权限。 1.P

zedboard(zynq)怎么学,学习资料和推荐书籍

https://blog.csdn.net/tianhen791/article/details/12657071 zedboard(zynq)怎么学,学习资料和推荐书籍 2013年10月12日 21:32:34 tianhen791 阅读数:22507 以下提供的资料,若未提供链接,直接百度搜索引号里的关键字即可 (1)“Zedboard 评测(一)"——Demo演示 :这篇资料可

【ZedBoard学习实例1】 VGA显示彩条

ZedBoard学习实例1 VGA显示彩条 ZedBoard学习实例1 VGA显示彩条参考文章改进 ZedBoard学习实例1 VGA显示彩条 参考文章 彩条控制verilog代码 主体参考了该文章的代码,文中还介绍了相关的电路图,还有ZedBoard的手册内容。19201080分辨率显示器的参数 针对不同尺寸的显示器,适用的分辨率也不同。VGA接口也是支持19201080分