本文主要是介绍【ZYNQ 详细案例二】VGA显示的详细实现与原理分析 彩条实验 基于ZEDBOARD,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

【ZYNQ 详细案例二】VGA显示的详细实现与原理分析 彩条实验 基于ZEDBOARD

首先我们来看看Zedboard用户手册和数据手册上对于其VGA端口的定义

可知由以上的信息我们得到。VGA显示信号由以下部分组成:

1、RGB444的数据值

2、VGA-HS: VGA行同步信号

3、VGA-VS: VGA场同步信号(列同步)

行同步有效说明一行扫描完了,到达下一行开始扫描‘场同步信号有效说明整个屏幕完成,又回到第一行开始扫描。以此重复达到持续绘制VGA显示屏幕这一功能。

但是,在显示器上的电子枪在扫描过程中需要进行复位调整,这时如果我们在复位时开始执行有效的行或者场扫描的话,那么会出现错误。这也是为什么VGA时序图中有FRONT_PORCH和BACK_PORCH空隙原因。

digilent关于VGA的资料

对于我们输入不同的行和场的同步信号,显示器会自动匹配我们的信号 产生图像。但我们的输入应该满足如下的配置。

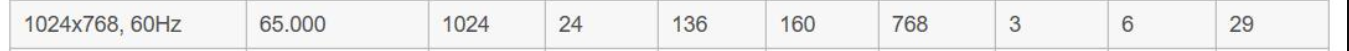

了现在我们以如下标准编写程序

由上面的参数,我们可以写一个参数定义对吧:

//行方向:

`define H_ACTIVE 1024

`define H_FRONT_PORCH 24

`define H_SYNCH_PULSE 136

`define H_BACK_PORCH 160

`define H_TOTAL ( `H_SYNCH_PULSE + `H_BACK_PORCH + `H_ACTIVE + `H_FRONT_PORCH )

//TOTAL=1344 //场方向

`define V_ACTIVE 768

`define V_FRONT_PORCH 3

`define V_SYNCH_PULSE 6

`define V_BACK_PORCH 29

`define V_TOTAL (`V_SYNCH_PULSE + `V_BACK_PORCH + `V_ACTIVE +`V_FRONT_PORCH )

//TOTAL = 806

为了编程方便,我们转换一下时序图,也是相当于建立一个坐标系,但是如果我们按照时序图上的那样,从 sync低电平时开始的话,那么到达有效信号还得先去除 sync和BP(back porch)的时间对吧。那如果我们改变一下顺序呢,我们从 有效信号开始时,记作 数轴原点 0。那么我们可以得到下面这种形式的定义:

现在我们就可以按照时序编写代码了:

首先扫描x方向和y方向:

//=========== 行计数器 ================

always@(posedge pixel_clk)beginif(rst)x_cnt <= 0;else if( x_cnt == (`H_TOTAL-1) )x_cnt <= 0;else x_cnt <= x_cnt + 1;

end

//========== 场计数器 ==================

always@(posedge pixel_clk)beginif(rst)y_cnt <= 0;else if(x_cnt == (`H_TOTAL-1))beginif(y_cnt == (`V_TOTAL - 1) )y_cnt <= 0;else y_cnt <= y_cnt + 1;end

end

现在 x_cnt 和 y_cnt 相当于就是我们的坐标变量了。我们可以在坐标不同的阶段对一些信号做处理。比如,我们要告诉VGA显示器我们什么时候数据是有效的:即 x_cnt 处于 0 ~ H_active 时对吧:

//======== 判断输出有效信号 ==========

reg h_en;

always@(posedge pixel_clk)begin if(x_cnt == (`H_TOTAL-1) )h_en <= 1;else if(x_cnt == (`H_ACTIVE-1))h_en <= 0;endreg v_en;

always@(posedge pixel_clk)beginif(x_cnt == (`H_TOTAL-1)) beginif(y_cnt == (`V_TOTAL-1) )v_en <= 1;else if(y_cnt == (`H_ACTIVE-1))v_en <= 0;end

endalways@(posedge pixel_clk) beginde <= v_en & h_en;end

请注意:对于场时序,他是一行扫描才加一,也就是当x_cnt扫完一行时,我们才会处理它。

接下来我们还有最后一项工作,就是把h_sync 和 v_sync 信号输出,对于这两个信号,我们只要在 x_cnt 处于 active+ front_porch 到 active+ front_porch+sync_pause 这个时间内给低电平(因为是低电平有效),其他时间都拉高不久可以了嘛。因此我们编写代码:

//================ 设置SYN的时间段为低电平================

always@(posedge pixel_clk)beginif(x_cnt == (`H_ACTIVE+`H_FRONT_PORCH-1))h_sync <=0;else if(x_cnt == (`H_ACTIVE+`H_FRONT_PORCH+`H_SYNCH_PULSE-1) )h_sync <=1;endalways@(posedge pixel_clk)beginif(rst)v_sync <=1;else beginif(x_cnt == `H_TOTAL-1) beginif(y_cnt == (`V_ACTIVE+`V_FRONT_PORCH-1))v_sync <=0;else if(y_cnt == (`V_ACTIVE+`V_FRONT_PORCH+`V_SYNCH_PULSE-1) )v_sync <=1; elsev_sync<=v_sync;endelsev_sync <=v_sync;end

end

这样一来,我们所有的工作都结束了。通过这个模块,我们能够有效让显示屏识别在哪里数据有效、在哪里是hs,在哪里是vs。所以现在显示屏能够正常工作啦。如果我们再给它RGB的信号,他就可以正常输出颜色了。

对了,现在先给出 【vga_driver.v 】模块的完整代码。

`timescale 1ns / 1ps//VGA Format 1024*768@60HZ

`define H_ACTIVE 1024

`define H_FRONT_PORCH 24

`define H_SYNCH_PULSE 136

`define H_BACK_PORCH 160

`define H_TOTAL ( `H_SYNCH_PULSE + `H_BACK_PORCH + `H_ACTIVE + `H_FRONT_PORCH )

//1344 // pixels`define V_ACTIVE 768

`define V_FRONT_PORCH 3

`define V_SYNCH_PULSE 6

`define V_BACK_PORCH 29

`define V_TOTAL (`V_SYNCH_PULSE + `V_BACK_PORCH + `V_ACTIVE +`V_FRONT_PORCH )

//806 // linesmodule vga_driver(input pixel_clk ,input rst ,output reg de ,output reg h_sync ,output reg v_sync ,output reg [10:0] y_cnt ,output reg [10:0] x_cnt

);//=========== 行计数器 ================

always@(posedge pixel_clk)beginif(rst)x_cnt <= 0;else if( x_cnt == (`H_TOTAL-1) )x_cnt <= 0;else x_cnt <= x_cnt + 1;

end

//========== 场计数器 ==================

always@(posedge pixel_clk)beginif(rst)y_cnt <= 0;else if(x_cnt == (`H_TOTAL-1))beginif(y_cnt == (`V_TOTAL - 1) )y_cnt <= 0;else y_cnt <= y_cnt + 1;end

end//======== 判断输出有效信号 ==========

reg h_en;

always@(posedge pixel_clk)begin if(x_cnt == (`H_TOTAL-1) )h_en <= 1;else if(x_cnt == (`H_ACTIVE-1))h_en <= 0;endreg v_en;

always@(posedge pixel_clk)beginif(x_cnt == (`H_TOTAL-1)) beginif(y_cnt == (`V_TOTAL-1) )v_en <= 1;else if(y_cnt == (`H_ACTIVE-1))v_en <= 0;end

endalways@(posedge pixel_clk) beginde <= v_en & h_en;end

//================ 设置SYN的时间段为低电平================

always@(posedge pixel_clk)beginif(x_cnt == (`H_ACTIVE+`H_FRONT_PORCH-1))h_sync <=0;else if(x_cnt == (`H_ACTIVE+`H_FRONT_PORCH+`H_SYNCH_PULSE-1) )h_sync <=1;endalways@(posedge pixel_clk)beginif(rst)v_sync <=1;else beginif(x_cnt == `H_TOTAL-1) beginif(y_cnt == (`V_ACTIVE+`V_FRONT_PORCH-1))v_sync <=0;else if(y_cnt == (`V_ACTIVE+`V_FRONT_PORCH+`V_SYNCH_PULSE-1) )v_sync <=1; elsev_sync<=v_sync;endelsev_sync <=v_sync;end

endendmodule现在我们编写一个tb仿真模块测试一下我们的时序。

module test3;

reg clk,rst;

wire de;

wire hs,vs;wire [10:0] x_cnt;

wire [10:0] y_cnt;vga_driver u0( . pixel_clk ( clk ) ,.rst ( rst ) ,.de ( de ) ,.h_sync ( hs ) ,.v_sync ( vs ) ,.y_cnt ( y_cnt ) ,.x_cnt ( x_cnt ) );always #30 clk=~clk;initial begin

clk = 0;

rst = 1;

#100 rst = 0;

endendmodule仿真得到时序图

我们放大看 hs什么时候低电平 什么时候重新拉高,如果是理想情况,一个是x_cnt到达h_active+h_front_porch-1 的时候也就是(1024+24)-1=1048-1=1047 的时候拉低,再过h_sync_pause=136 也就是(1048+136)-1=1184-1=1183的时候拉高(为什么要减一 是因为我们从0开始计数的呀):

对于场时序也是这样分析来验证。

一定要先仿真通过再下比特流!!

我们现在写一个顶层模块,同时把GRB颜色输出,但是,在此之前,我们应该给出一个65MHZ的时钟才行,注意,这里的65是根据我们之前讨论的 在不同分辨率下的VGA时序参数那里得到的。此处我们可以用vivado自带的时钟IP核来完成时钟频率的转换。(IP核 如果是第一次接触,可以理解为一个函数,你只用关心输入输出,不用在意它是如何实现的)

点击【IP Catalog】

选择【clock wizard】时钟向导

我们只用把输出改成65MHZ即可

接下来我们就可以写顶层模块了。

module TOP(output [3:0] R,G,B,output h_sync,v_sync,input clk,rst);wire clk65M ;wire de ;clk_wiz_0 u_clock(.clk_in1_0(clk),.clk_out1_0(clk65M),.locked_0(),.reset_0(1'b0));wire [10:0]x_cnt ;wire [9:0]y_cnt ;vga_driver u0( . pixel_clk ( clk65M ) ,.rst ( rst ) ,.de ( de ) ,.h_sync ( h_sync ) ,.v_sync ( v_sync ) ,.y_cnt ( y_cnt ) ,.x_cnt ( x_cnt ) );reg[3:0] Rr , Gr , Br ;always@ (posedge clk)case ( x_cnt ) //对于x_cnt在不同的位置,我们赋予不同的颜色,就会形成彩条128*4 : { Rr , Gr , Br } <={ 4'b0000 , 4'b0000 , 4'b0000 } ;128*1 : { Rr , Gr , Br } <={ 4'b0000 , 4'b0000 , 4'b1111 } ;128*2 : { Rr , Gr , Br } <={ 4'b0000 , 4'b1111 , 4'b0000 } ;128*3 : { Rr , Gr , Br } <={ 4'b0000 , 4'b1111 , 4'b1111 } ;128*0 : { Rr , Gr , Br } <={ 4'b1111 , 4'b0000 , 4'b0000 } ;128*5 : { Rr , Gr , Br } <={ 4'b1111 , 4'b0000 , 4'b1111 } ;128*6 : { Rr , Gr , Br } <={ 4'b1111 , 4'b1111 , 4'b0000 } ;128*7 : { Rr , Gr , Br } <={ 4'b1111 , 4'b1111 , 4'b1111 } ;endcaseassign B = ( de == 0 ) ? 0 : Br ;assign G = ( de == 0 ) ? 0 : Gr ;assign R = ( de == 0 ) ? 0 : Rr ;endmodule

最后,代码实现很简单,主要是要掌握如何处理时序以及如何调用IP核例化实现功能。代码可以参考,新手可以多写写。最后的效果:

最后,更改不同的 vga_driver的分辨率参数,将会得到不同的分辨率下的图像。大家可以尝试一下,但如果屏幕报错黑屏,多半是时序或者时钟的问题。解决办法:

1、检查你的时钟是否是对应的分辨率下的有效值。

2、显示屏是否支持这种分辨率。

3、检查 行场时序是否有错

3、检查de信号(即数据有效信号)是否出错

4、管脚约束是否匹配你的板子,电压是否是3.3v

。。。

这篇关于【ZYNQ 详细案例二】VGA显示的详细实现与原理分析 彩条实验 基于ZEDBOARD的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!