systolic专题

脉动型(Systolic)FIR滤波器的实现

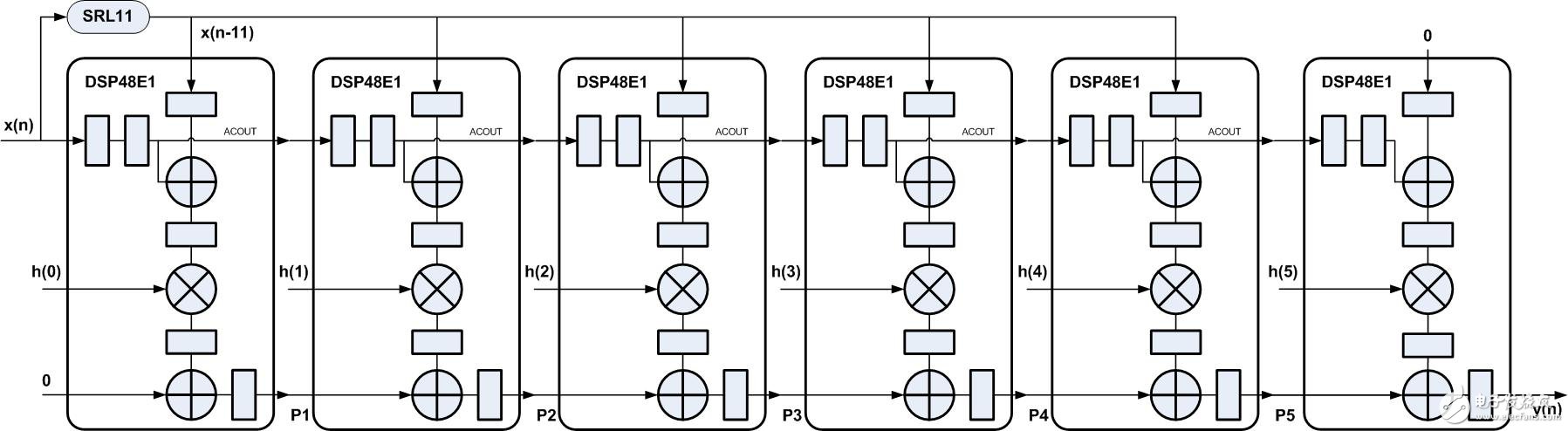

脉动型(Systolic)FIR滤波器设计 #e# 脉动型FIR滤波器是对直接型的升级,在每个操作后都加入流水线级,每个动作都打一拍,就跟心脏跳动一样,因此称为脉动型,这种结构非常适用于高速数据流的处理。如图1所示为脉动型FIR滤波器结构。 图1 与直接型结构不同的是,输入数据到下一个处理单元都需要打2拍,这是为了使乘法后的累加数据同步,下面推导验证:

AI算力基础 _Systolic Array的实现

阅读总结 Google的TPU是AI_ASIC芯片的鼻祖,从论文的作者数量之庞大,及论文少有的出现了致谢,就可以看出一定是历经了一番磨砺才创造出来。该论文发表在 2017 年,让我们回到那个年代,一同看看是什么样的背景诞生了如此伟大的艺术品~ 0. 背景 作者:H.T.Kung 1982. 年份:1982. 标题:《Why Systolic Architecture?》 关键词: co

通用脉动阵列systolic array及矩阵乘法Matrix Multiplication

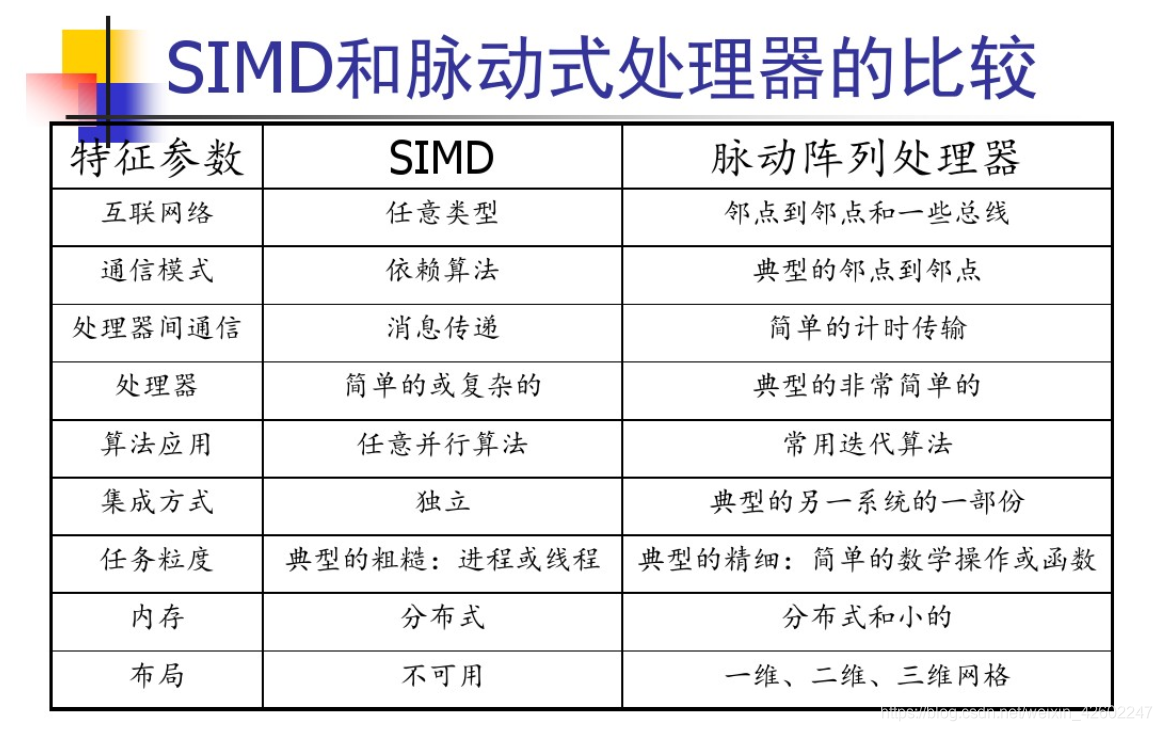

目录 脉动阵列的特点Matrix Multiplication矩阵乘法通用SA(systolic array)发展趋势SIMD和SA处理器的比较Reference 脉动阵列的特点 优点: 结构简单,规整,控制方便 计算并行度高,吞吐量高 缺点: 具有一定的专用性 Matrix Multiplication矩阵乘法 下图原文有个小错误,A[J,K]应该是A[I,K] 为

AI算力基础_Why-systolic-architecture

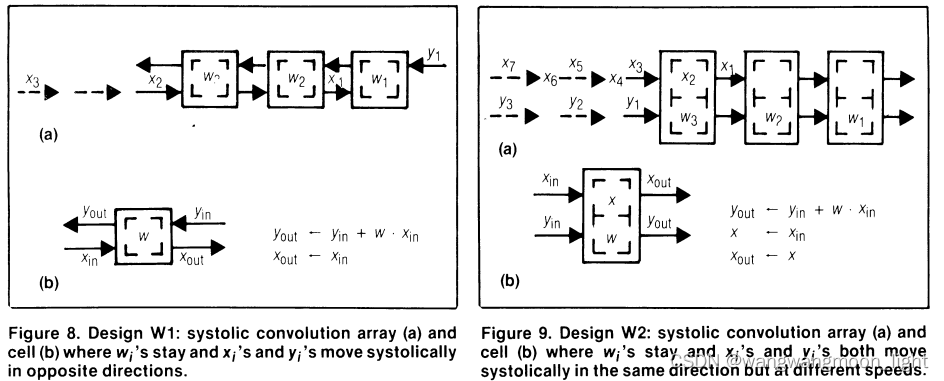

阅读总结 作者:H.T.Kung 1982. 年份:1982. 标题:《Why Systolic Architecture?》 关键词: cost-effectiveness:成本高效益 concurrency:并发性 decompose:分解 massive parallelism:大规模并行 Why Systolic Architecuture? H.T.Kung 1982 Systol

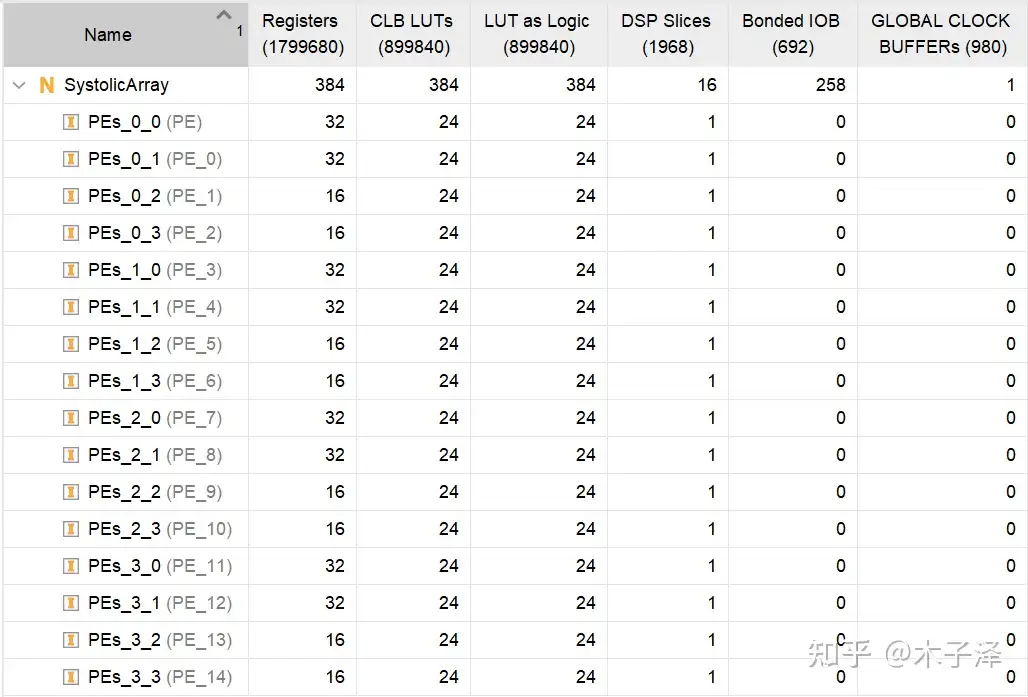

使用Chisel搭建Systolic Array

最近听到非常多人吹Chisel,为了方便快速做算法实现,就去尝试学了下,发现确实很香,有种相见恨晚的感觉。 今天是使用Chisel搭建个脉动阵列(Systolic Array, SA)[1],脉动阵列是神经网络中最基础也是最常用的组件之一。它主要是实现高效的矩阵乘法,而神经网络中到处都是矩阵乘法,从全连接层到卷积层(GEMM),都可以用矩阵乘法表示。UCB的Chipyard中专门集成了个脉动阵列

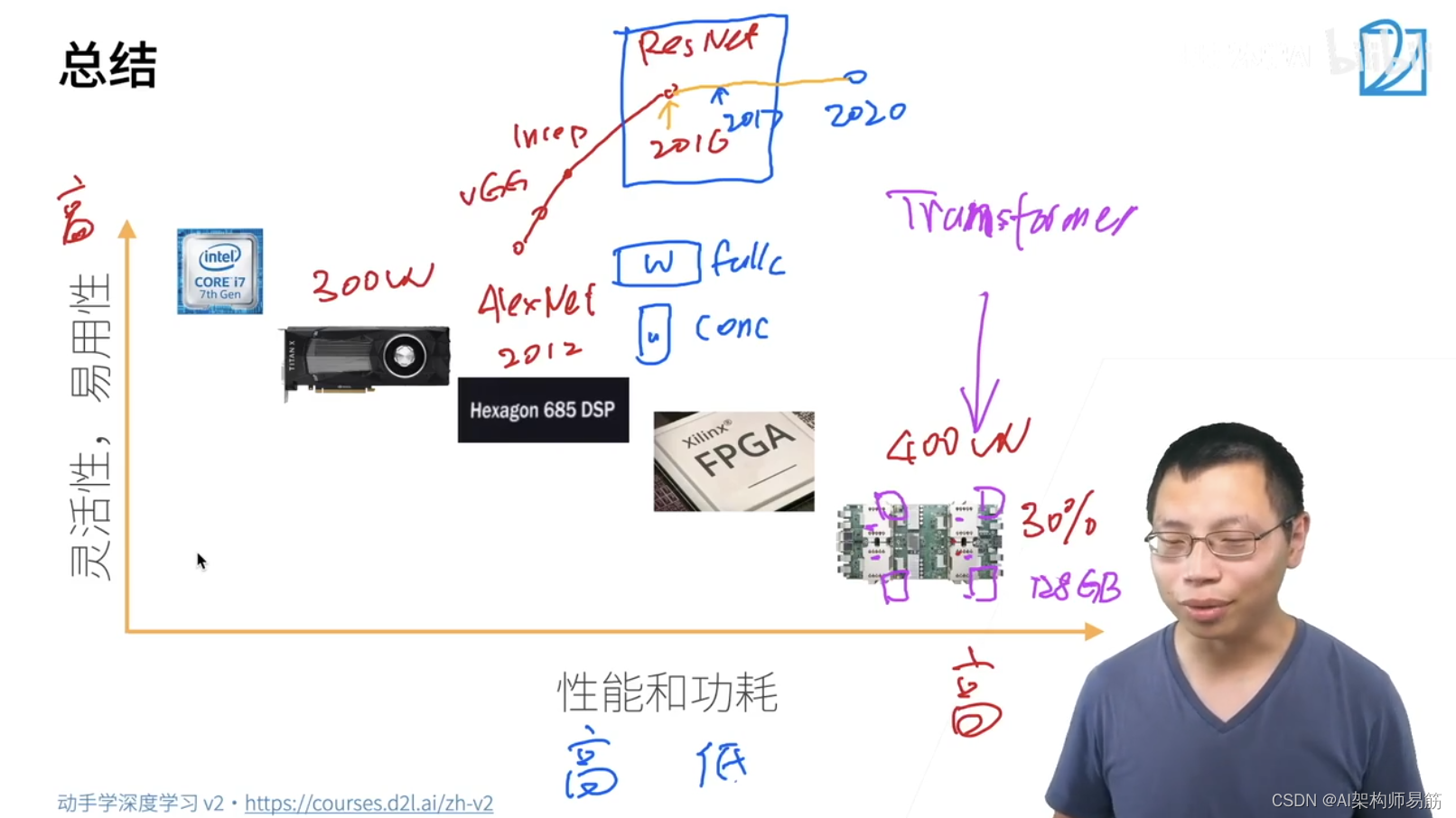

深度学习硬件:TPU, DSP, FPGA, AI ASIC, Systolic Array 动手学深度学习v2

1. TPU和其他 1.1 手机芯片 1.2 DSP digital signal processor 数字信号处理 1.3 可编程阵列 FPGA - field-programmable gate array 1.4 AI ASIC - Application-specific integrated circuits Systolic Array

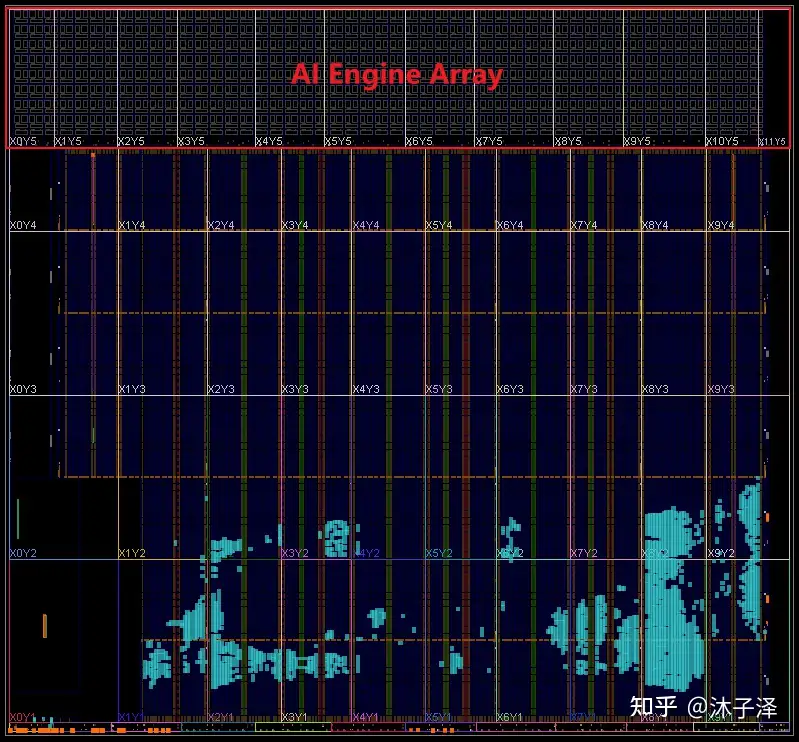

Versal系列0-AI Engine与Systolic Array

最近在开发VCK190时,发现Xilinx Versal系列的AI engine(AIE),其实和Systolic Array(SA)有着很相似的地方。Xilinx工程师在研发AIE时,应该是有所借鉴SA的。 Systolic Array最早是H. T. Kung于1982年在论文《Why systolic architectures?》中提出,但是由于过于过于专用性,在通用处理器当道的年代并没