ddr专题

DDR的Controller、Channel、Chip、Rank、Bank、Row、Column、Sided、Dimm

目录 概览 1.概览 先从半导体生产开始,生产出来还没切割的叫晶圆(wafer)。切割出来还没封装的叫裸die(bare die)。封装好的叫颗粒(component)。做成内存条后叫模组(module)。下文我们也会按这样的称呼去区分。 2.Controller(内存控制器) 一开始内存控制器在主板上有独立的芯片;在英特尔微处理器

linux如何查看内存条是ddr几代

在 Linux 系统中,可以通过以下几种方法查看内存条的类型和代数(如 DDR3、DDR4 等): 1. 使用 dmidecode 命令 dmidecode 是一个工具,它可以从系统的 DMI 表(也称为 SMBIOS 表)中提取硬件信息,包括内存的信息。 查看内存信息 sudo dmidecode --type memory 这个命令会输出关于系统内存的详细信息。你可以在输出中找到类

内存之RAM、SRAM、DRAM、ROM、FLASH、SDRAM、DDR*(一篇文章就懂)

内存之RAM、SRAM、DRAM、ROM、FLASH、SDRAM、DDR* 内存 内存(Memory)指的是内存存储器,又称为主存,是CPU用来直接寻址和存储的空间,它相当于一座桥梁,用以负责诸如硬盘、主板、显卡等硬件上的数据与处理器之间数据交换处理,我们可以把内存看作数据缓存区,一个高速的缓存区。内存之所以称为内存,是相对于硬盘这些外存而言,我们要用的软件数据都安装存放在外存上,但是当我

地平线—征程2(Journey 2-J2)芯片详解(16)—DDR系统

写在前面 本系列文章主要讲解地平线征程2(Journey 2-J2)芯片的相关知识,希望能帮助更多的同学认识和了解征程2(Journey 2-J2)芯片。 若有相关问题,欢迎评论沟通,共同进步。(*^▽^*) 错过其他章节的同学可以电梯直达目录↓↓↓ 地平线—征程2(Journey 2-J2)芯片详解——目录-CSDN博客 5. DDR子系统 DDR内存子系统包括DDR控制器、

【转】DDR基础之Write_leveling简介

DDR基础之Write_leveling简介 2016年11月24日 09:31:37 雄关迈步 阅读数:2676 1)为了更好的提高信号完整性,DDR3存储模块采用了fly-by的拓扑结构。该拓扑应用于地址、控制、时钟线。Fly-by拓扑能有效减少stub的长度,但是较长的走线带来了CK-CK#与DQS-DQS#间的时延(由于CK-CK#的飞行时间,其到达每个DDR3颗粒的时间不同,而DQS

【转载】DDR扫盲——关于Prefetch与Burst的深入讨论

DDR扫盲——关于Prefetch与Burst的深入讨论 1赞 发表于 2017/8/15 13:17:55 阅读(12692) 评论(1) 学习DDR有一段时间了,期间看了好多的资料(部分公司的培训资料、几十篇的博文,Micron的Datasheet,JESD79规范等)。但是有一个问题,想了好久(很多资料都没有说明白),至今才算搞明白,所以写一篇文章和大家分享一下。 如题,接下来要讨论

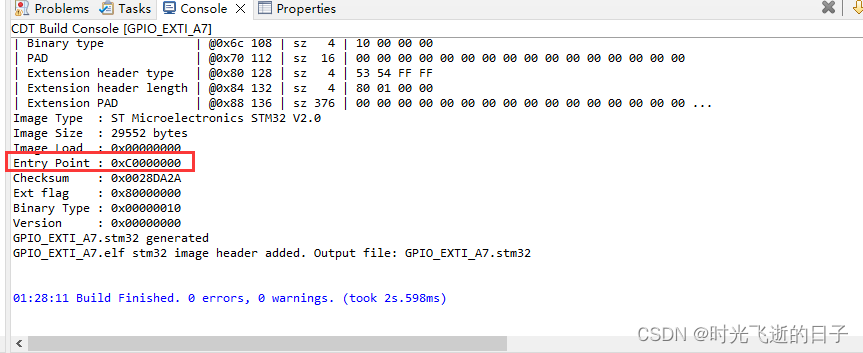

stm32MP135裸机编程:修改官方GPIO例程在DDR中点亮第一颗LED灯

0 参考资料 轻松使用STM32MP13x - 如MCU般在cortex A核上裸跑应用程序.pdf正点原子stm32mp135开发板&原理图STM32Cube_FW_MP13_V1.1.0STM32CubeIDE v1.15 1 需要修改那些地方 1.1 修改LED引脚 本例使用开发板的PI3引脚链接的LED作为我们点亮的第一颗LED灯,开启我们的基于stm32MP135的裸机编

博客摘录「 AXI三种接口及DMA DDR XDMA介绍(应用于vivado中的ip调用)」2024年6月10日

关键要点: 1.AXI Stream经过协议转换可使用AXI_FULL(PS与PL间的接口,如GP、HP和ACP)。 2.传输数据类里就涉及一个握手协议,即在主从双方数据通信前,有一个握手的过程。基本内容:数据的传输源会产生“VALID”信号,来指明何时数据有效或控制信息有效。而在目标源一方,会产生“READY”信号,来指明已经准备好接受数据或控制信息。当“VALID”信号和“READY”信号

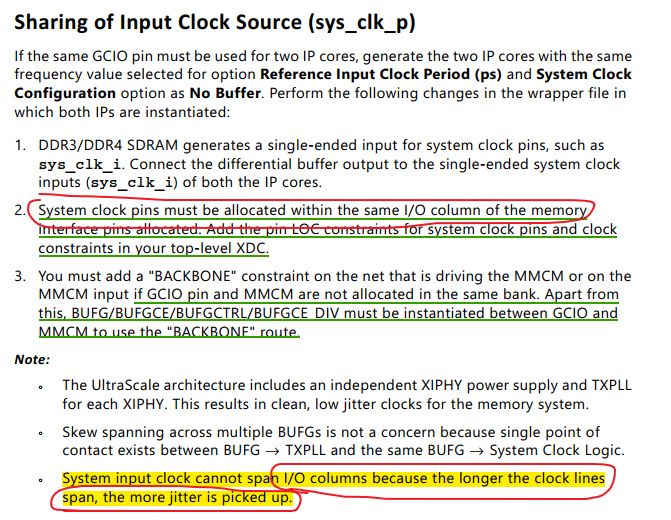

Xilinx FPGA 支持双通道DDR

1,双channel对应于两个DDR MC控制器,既然是双channel,那么两个channel之间必然要做数据同步,组合成更高位宽的DDR。因此对于多die器件,在布局上首先要保证两个channel处于同一个SLR。现在笔记本大多是双通道内存设计,可以用CPU-Z查看: 2,时钟结构 操作记录: 1,两个通道共用主时钟和逻辑复位 2,两个通道均为72bit不能满足同S

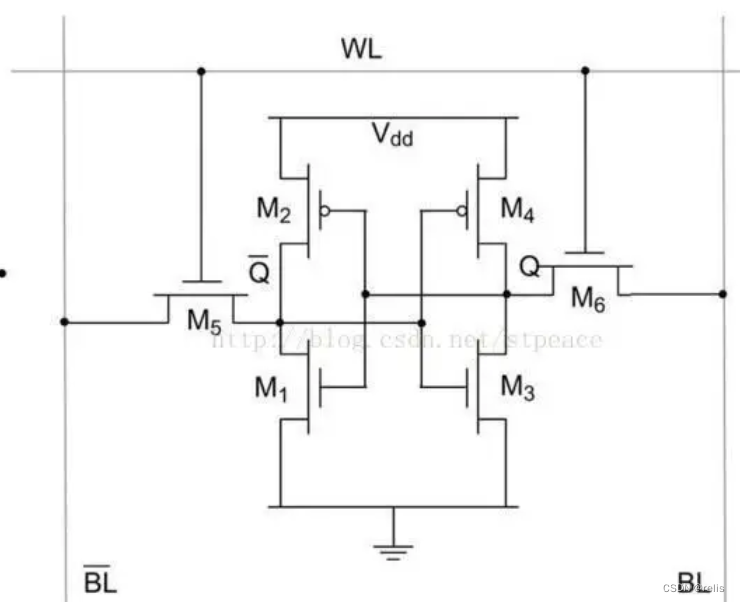

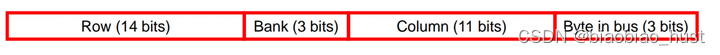

DDR bank 位宽等概念

DDR3中bank, 16bit和32bit等概念 DDR3中bank, 16bit和32bit等概念 最近在看内存相关的东东。 以前认为内存就是块资源,需要的时候,malloc出来一部分使用即可。对内部的东东没有深入了解过。 刚开始看起来,感觉有点丈二和尚。 通过各种查询,并请教牛人,对基本概念有了个初步了解,先总结一把。 先说说bank。 看到bank首先想到了银行,然后是利率

【DDR 终端稳压器】Sink and Source DDR Termination Regulator [C] S0 S1 S2 S3 S4 S5 6状态

TPS51200A-Q1 器件通过 EN 功能提供 S3 支持。EN引脚可以连接到终端应用中的SLP_S3信号。当EN = 高电平(S0 状态)时,REFOUT 和 VO 引脚均导通。当EN = 低电平(S3状态)时,VO引脚关断并通过内部放电MOSFET放电时,REFOUT引脚保持不变。当EN = 低电平且REFIN电压小于0.390 V时,TPS51200A-Q1器件进入伪S5状态。当伪S5

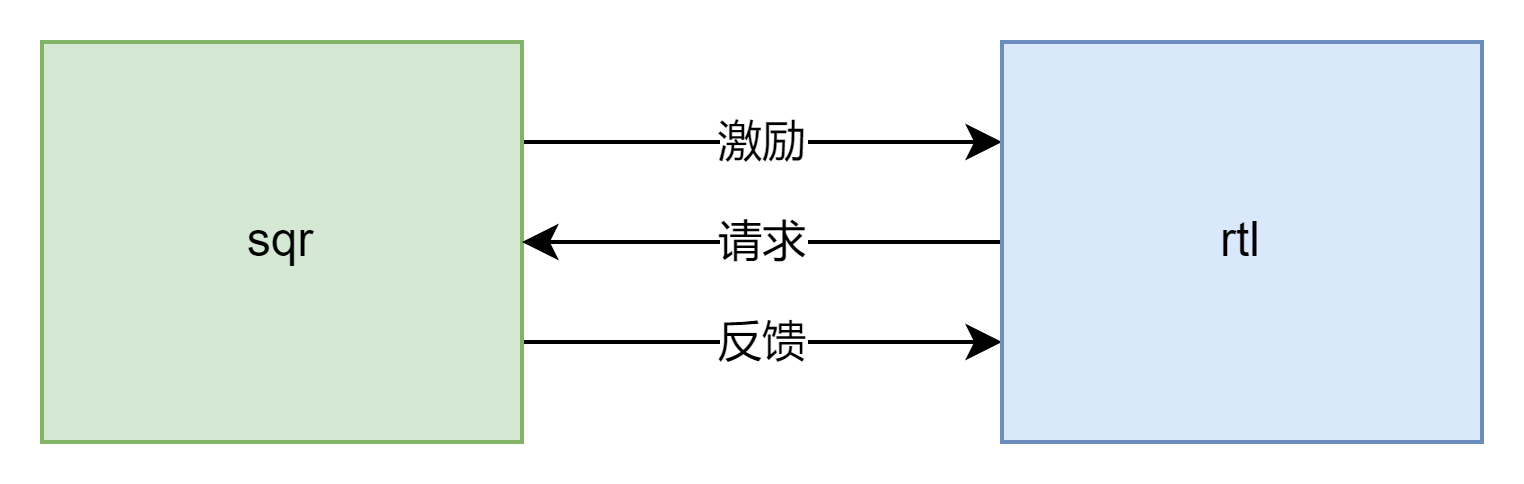

【IC前端虚拟项目】axi ddr/sram验证组件思路与编写

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 在完成了所有的utils包括apb_utils之后,就要进行验证环境的整体搭建,因此我们再把验证环境拿出来看一下: 按照由底至顶层的思路,接下主要有五大部分需要我们完成:ram_model、reference_model、env、base_test和harness,这一篇从最难的ram_model开始说起。这

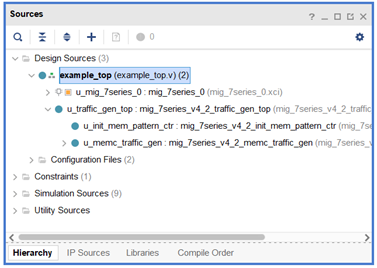

『FPGA通信接口』DDR(4)DDR3内存条SODIMMs读写测试

文章目录 前言1.MIG IP核配置2.测试程序3.DDR应用4.传送门 前言 不论是DDR3颗粒还是DDR3内存条,xilinx都是通过MIG IP核实现FPGA与DDR的读写。本文区别于DDR颗粒,记录几个与颗粒配置不同的地方。关于DDR的原理与MIG IP的简介,请查看前面文章,链接在文末。本文提供了配套的工程源码,链接在文末,本文用的内存条为MT16KTF1G64HZ

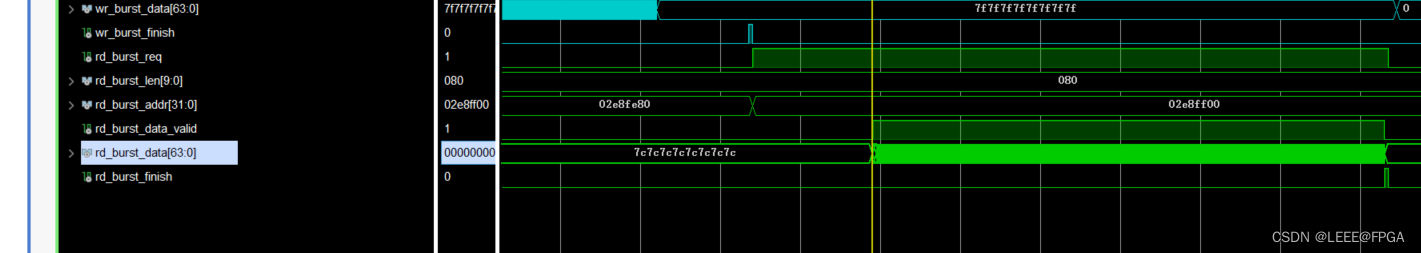

『FPGA通信接口』DDR(3)DDR3颗粒读写测试

文章目录 前言1.配套工程简介2.测试内容与策略3. 测试程序分析4.程序结果分析5.一个IP控制两颗DDR36.传送门 前言 以四颗MT41K512M16HA-125AIT颗粒为例,介绍如何在一块新制板卡上做关于DDR3的器件测试。前面两篇介绍了什么是DDR,并介绍了xilinx给出的FPGA与DDR完美结合的方案MIG IP核,请按照顺序阅读DDR相关文章,链接在文末。D

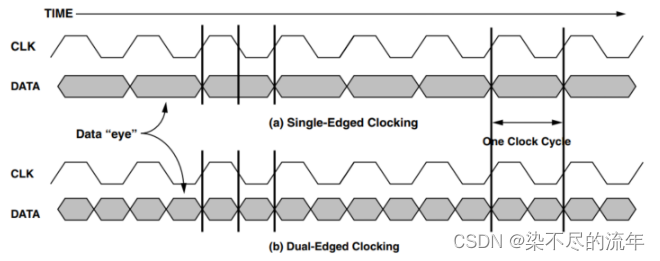

SDR SDRAM和DDR SDRAM的区别

SDR SDRAM(Single Data Rate Synchronous Dynamic Random Access Memory)和DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)是两种不同类型的内存技术,它们的主要区别在于数据传输速率和工作原理,具体如下: 数据传输速率: SDR SDRAM:只能在

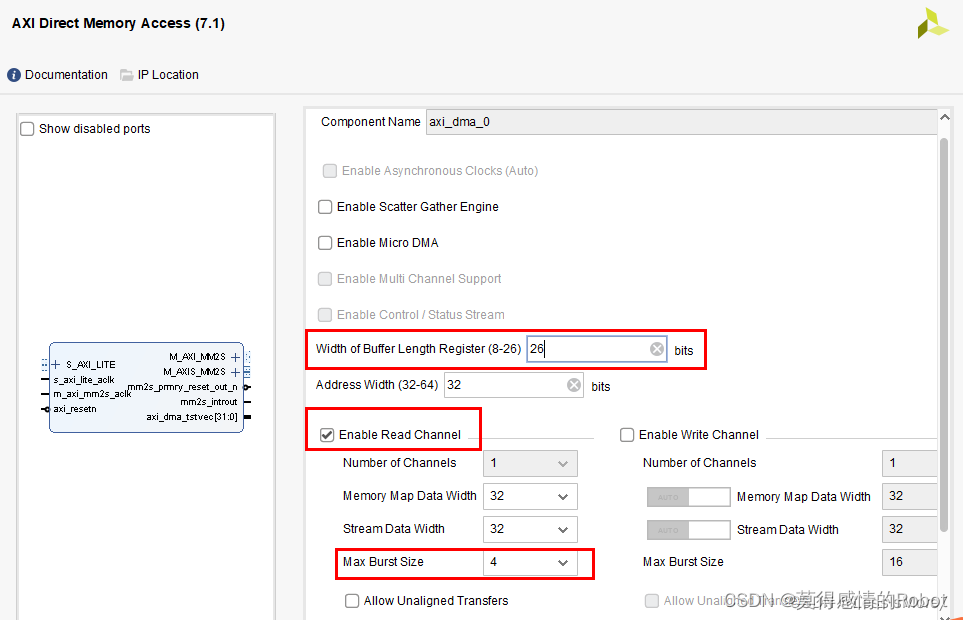

ZYNQ--PL读写PS端DDR数据

PL 和PS的高效交互是zynq 7000 soc开发的重中之重,我们常常需要将PL端的大量数 据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA 的方式来进行,但是各种协议非常麻烦,灵活性也比较差,本节课程讲解如何直接通过AXI总 线来读写PS端ddr的数据,这里面涉及到AXI4协议,vivado的FPGA调试等。 1 ZYNQ 的HP端口使用 zynq

zedboard如何从PL端控制DDR读写(六)

上一节说到了DDR寻址的问题,如下图: 从官方文档上我们看到了DDR的地址是从0008_0000开始的,那么我们开始修改Xilinx给我们提供的IP核代码。其实很简单,上一节已经分析了地址停留在0000_1000的原因,现在我们只需要把write_burst_counter的位宽变大就可以了。 从上表看到地址范围由全0到全1,计算一下就知道需要的宽度为27,即 C_NO_B

zedboard如何从PL端控制DDR读写(四)

PS-PL之间的AXI 接口分为三种: • 通用 AXI(General Purpose AXI) — 一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。 • 加速器一致性端口(Accelerator Coherency Port) — 在 PL 和 APU 内的 SCU之间的单个异步连接,总线宽度

zedboard如何从PL端控制DDR读写(三)——AXI-FULL总线调试

本文主要是总结一下使用AXI-FULL调试的过程。 首先想到的是用RAM IP核来测试,方法是通过AXI接口向RAM写入一组数据并读出,看起来很简单,然而试了好久都没能出结果。如下图所示,其实AXI RAM就是在本地RAM接口的基础上套了一个AXI的壳 在使用modelsim仿真的时候总是会抛出一个警告,具体的警告类型忘了,下次有机会再尝试。试了好多次都这样,

南京观海微电子---MIG IP核的使用——DDR接口专栏(二)

1. 前言 本文将向大家介绍Xilinx FPGA下的MIG IP核使用方法。通过该IP核,用户可以对片外DDR存储颗粒进行读写操作。 2. DDR器件型号 在使用MIG IP核前,我们需要了解待读写的DDR存储颗粒的型号。只有确定了型号,才能对MIG IP核进行正确地设置。这里我们以型号为MT41J256M16HA-125的DDR颗粒举例。 DDR颗粒的型号命名规则如下图所示:

2万字一文带你看懂汽车智能座舱的存储DDR市场、技术

吃瓜群众:机哥,为什么谈到存储DDR,你要命名为武林高手? 机哥:你看过天龙八部吧,整个剧里面的绝顶高手既不是乔峰,也不是段誉,而且在少林寺扫地的那个扫地僧,无论是硬件、软件、测试看到DDR都是心生敬意,实在是高深莫测,看不透,摸不懂。 在很多应用型公司,DDR部分的设计都是按照CPU主芯片搭配过的DDR进行选型设计,不敢越雷池一步,由于DDR跑的速度实在太快,会涉及到

![【DDR 终端稳压器】Sink and Source DDR Termination Regulator [C] S0 S1 S2 S3 S4 S5 6状态](https://img-blog.csdnimg.cn/direct/227ed36e2d5a4fefbb590fa1532e90b7.png)