本文主要是介绍南京观海微电子---MIG IP核的使用——DDR接口专栏(二),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1. 前言

本文将向大家介绍Xilinx FPGA下的MIG IP核使用方法。通过该IP核,用户可以对片外DDR存储颗粒进行读写操作。

2. DDR器件型号

在使用MIG IP核前,我们需要了解待读写的DDR存储颗粒的型号。只有确定了型号,才能对MIG IP核进行正确地设置。这里我们以型号为MT41J256M16HA-125的DDR颗粒举例。

DDR颗粒的型号命名规则如下图所示:

DDR颗粒 I/O管脚时钟频率:

根据Speed Grade中的“-125”我们可以找到图中的tCK = 1.25ns,对应算出DDR颗粒支持的最大IO时钟频率:1/1.25ns = 800Mhz。此处的IO时钟频率也就是DDR3的频率。

DDR颗粒的位宽和存储容量:

根据Configuration中的256M16,可以得知该DDR颗粒的数据位宽是16位,并且存储容量为512MB(256M*16bit = 512MB)。

如果我们将4个该DDR颗粒组成一组,则可以构成一个数据位宽位64bit,最大时钟频率为800MHz,存储容量为2GB的DDR存储器。

DDR颗粒的带宽:

由于DDR传输数据方式是在时钟上升和下降沿都进行传输,所以芯片的一根数据线上的传输速率为2*800Mhz = 1600MT/s,即1600Mbit/s。

如果我们将4个该DDR颗粒组成一组,数据传输带宽计算如下

1600Mbit/s x 16 x 4 = 12.5GByte/s

3. FPGA选型

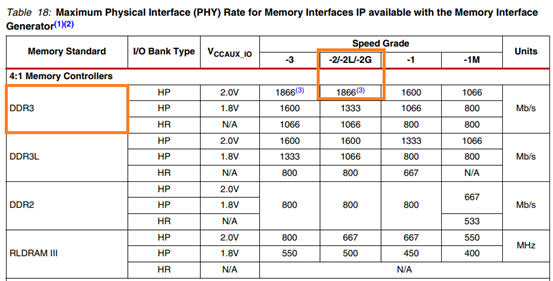

DDR颗粒的选型也会影响到FPGA型号的选择。比如上面选择的DDR颗粒带宽为1600MT/s,则一定要选择速度等级支持大于等于1600MT的FPGA器件,这样才能发挥该DDR颗粒的最大带宽效率。

我们选用的FPGA型号为XC7VX690T,速度等级为-2,通过在Xilinx官网查询DS183文档可知,该器件支持的最大DDR频率为1866MT,因此我们选用的FPGA理论上是可以100%发挥型号为MT41J256M16HA-125 DDR的最大传输带宽的。

4. MIG IP核的设置

下面将详细的介绍Xilinx MIG IP核的使用方式,通过该IP核,用户可以对片外DDR存储颗粒进行读写操作。

(1) 创建新的Xilinx vivado项目,并将FPGA器件选为XC7VX690T,速度等级为-2。

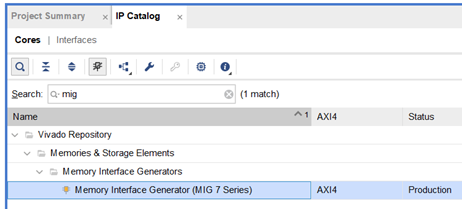

(2) 在Vivado的“Flow Navigator”窗格中,选择“IP Catalog”。在IP目录中搜索“MIG”或“Memory Interface Generator”关键词。双击要使用的IP核。

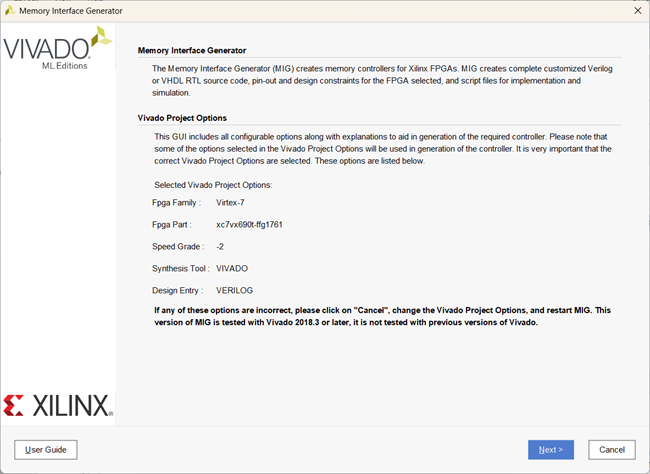

(3) IP配置窗口第一页显示了工程使用的FPGA器件型号,用户需要确认才能进行下一步。

注意,可能有用户发现文章弹出的界面和自己的MIG IP核设置界面不太一样,这个是由于工程选用了不同的FPGA器件,不同的FPGA器件使用的MIG IP是有细微不同,比如我们这个IP核名称后面显示是MIG 7 Series,即该MIG IP是专门用于Xilinx 7系列FPGA的。

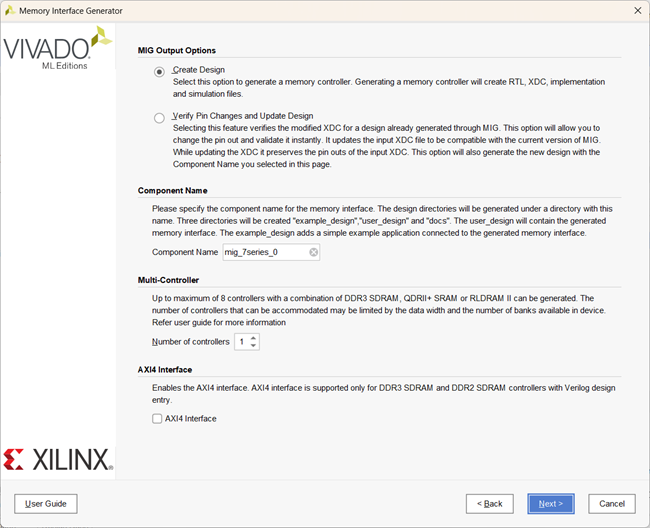

(4) 在MIG Output Options选项中选择Create Design,用于创建新的内存控制器设计。在Compent Name一栏中输入待创建的组件名称。

Multi-Controller一栏中选择需要生成的控制器数量,此处我们默认选择1。

暂时不勾选AXI4 Interface复选框,本文我们先生成一个具备常规的DDR接口的IP核。如果勾选了该选项,则会生成一个AXI4接口的MIG IP核,用户只用遵循AXI接口协议,便可读写AXI接口的MIG IP核。

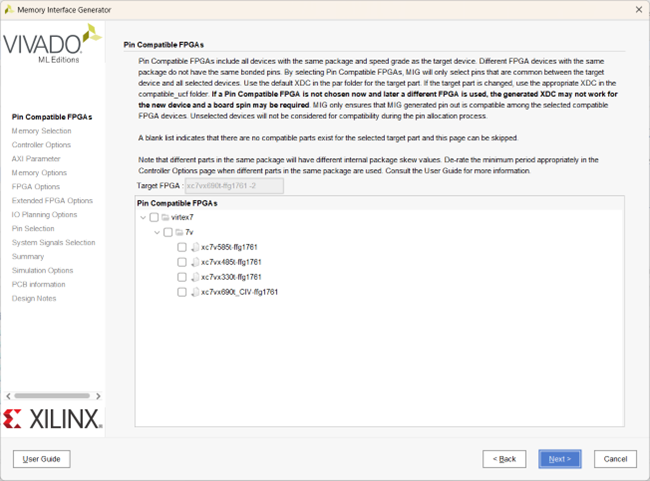

(5) 在Pin Compatible FPGA页面中列出了和本工程使用的FPGA具有相同封装的其他型号FPGA,如果需要IP生成的设计文件兼容其他型号FPGA,在列表中勾选相应型号即可。

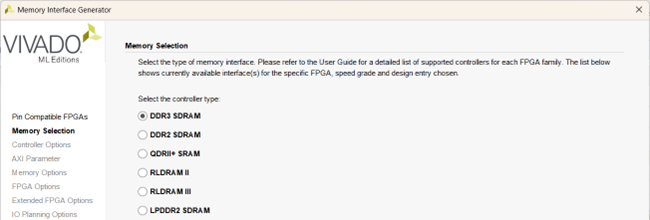

(6) 在Pin Compatible FPGA页面中,选择DDR3 SDRAM类型。

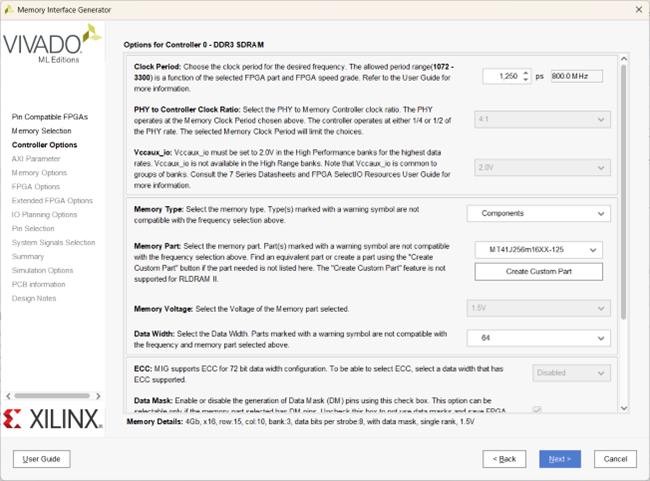

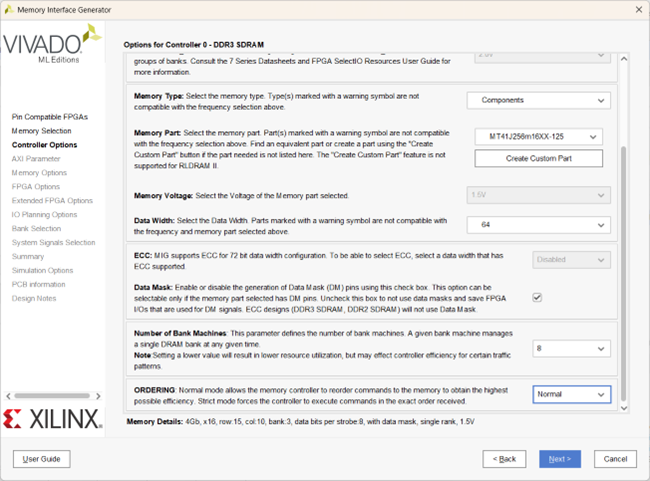

(7) 在Options for Controller 0是关键的配置一步。

Clock Period为DDR工作的时钟频率。在第二章中我们选用的DDR颗粒最高工作主频为800MHz,因此此处我们填写1250ps即800MHz。

PYH to Controller Clock Ratio为PYH工作时钟到DDR控制器工作时钟的转换比例。图中默认设置为4:1,即PHY的工作频率为800MHz,DDR控制器的工作时钟为200MHz。

Memory Part设置为第二章的DDR器件,MT41J256M16HA-125。

MT41J256M16HA颗粒位宽为16bit,由于我们使用的内存条级联了4个该DDR颗粒,因此Data Width设置为16*4=64bit。

Number of Bank Machines一栏显示了该设计配置支持的Bank Machine的数量。如果追求DDR的读写效率,建议该栏选择最大的数量。如果FPGA资源比较紧张,可以将该数量设小些以节约FPGA的片上资源。

其它配置都使用默认值。

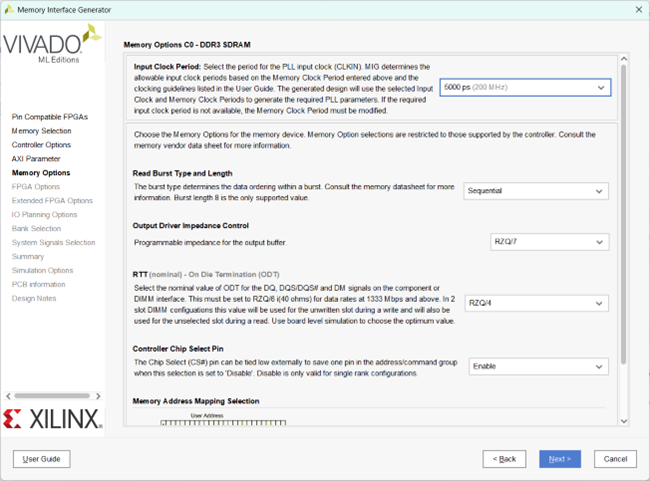

(8) 在Memory Options设置页:

Input Clock Period: 选择5000ps (200MHz)选项,该时钟为DDR PLL的输入时钟。

Output Driver Impedance Control: 设置相应的输出匹配阻抗。根据所选的DDR器件手册,来设置该参数。例如,RZQ/6对应输出阻抗为40Ω,RZQ对应240Ω。

其它参数保持默认,不需要修改。

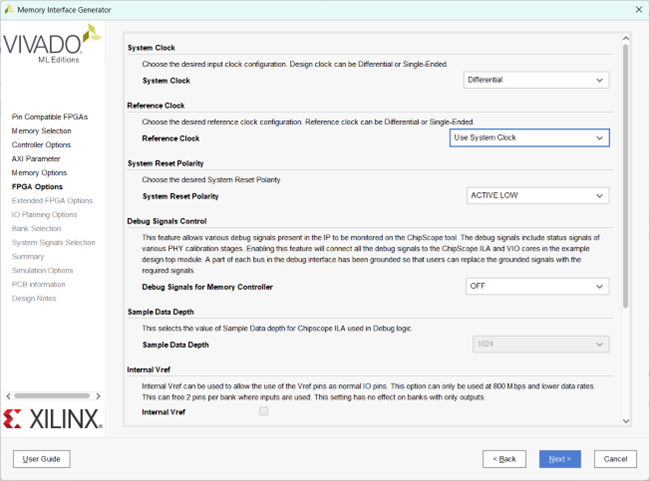

(9) FPGA Options设置页:

System Clock: 为该MIG IP核的系统输入时钟,此处需要选择时钟类型是差分、单端还是“No buffer”类型。注意,如果选择“No buffer”,则该系统输入时钟必须是FPGA的内部时钟。

Reference Clock: 为MIG IP核的参考时钟。此处也是需要选择时钟类型。注意,如果System Clock选择的频率范围为199~201MHz,则Reference Clock类型复选框中会出现“Use System Clock”选项。我们为了简化时钟电路的设计,此处选择“Use System Clock”选项。

System Reset Polarity: 为MIG IP核的复位电平,HIGH代表复位电平为高,LOW代表复位电平为低。

Debug Signals Control 和 Sample Data Depth选项为给该IP添加ILA调试项。

XADC选项要使能,其它参数保持默认,不需要修改。

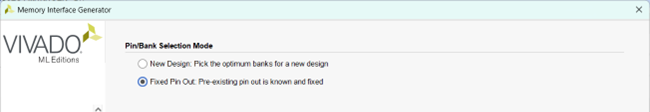

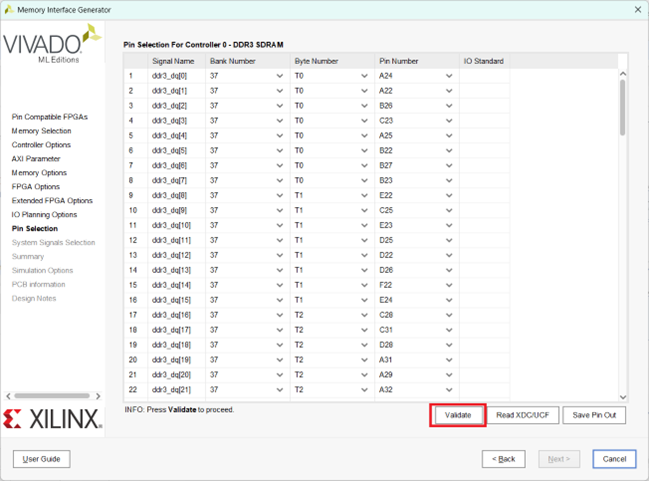

(10) FPGA管脚分配:我们选择Fixed Pin Out 模式,然后根据自己的FPGA开发板原理图填写管脚分配界面。填写完所有管脚后,点击“Validate”按钮。Vivado会自检填写的所有管脚是否符合基本的规则,如果检测通过,便可以点击“Next”按钮进入下一步。

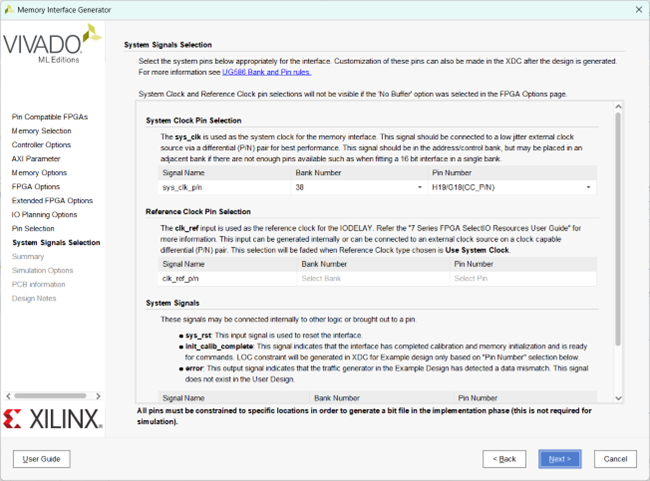

(11) System Signals Selection配置页:该页主要设置连接DDR系统时钟/参考时钟的FPGA输入管脚。由于前面我们设置了参考时钟使用系统时钟的选项,此处只用设置系统时钟管脚即可。

(12) 完成MIG IP核设置。后面MIG设置页面都是些参数总结页面,都直接点击“Next”按钮即可。最后一页点击“Generate”按钮即Vivado开始根据以上参数生成对应的MIG IP核。

5. 生成MIG IP核例程

对刚生成的IP核不知道如何使用,可以采用以下两种方法:

(1) 查找该IP核的User Guide文档,学习使用方法。MIG (7 Series)的IP核User Guide对应的文档编号为UG586。

(2) 查看该IP核的官方示例工程。工程的打开方式如下,右键点击刚生成好的IP核,选择“Open IP Example Design..”选项。

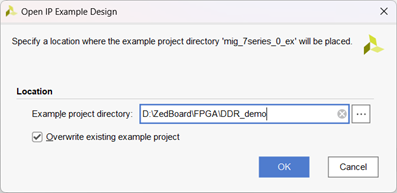

选择待存放Example Design的具体路径,点击“OK”选项。

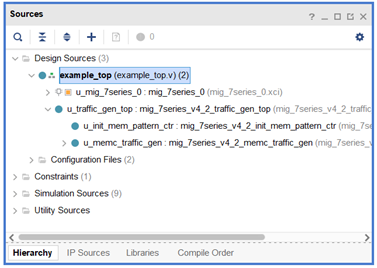

此时Vivado会生成并自动打开示例工程。示例工程的结构如下图。

这篇关于南京观海微电子---MIG IP核的使用——DDR接口专栏(二)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!