mig专题

将Xilinx DDR3 MIG IP核的AXI_FULL接口封装成FIFO接口(含源码)

MIG IP除了支持前文讲解的APP接口,还支持axi_full接口,因此本文使用MIG IP的axi_full接口封装为FIFO接口,取代以太网传输图片工程中的DDR3读写控制模块。 回顾前文APP接口的DDR3读写控制模块,框图如下所示,本文需要将MIG IP的APP接口更换为axi_full接口时序,从而ddr3_rw模块需要重新设计。 图1 DDR3读写控制模块

南京观海微电子---MIG IP核的使用——DDR接口专栏(二)

1. 前言 本文将向大家介绍Xilinx FPGA下的MIG IP核使用方法。通过该IP核,用户可以对片外DDR存储颗粒进行读写操作。 2. DDR器件型号 在使用MIG IP核前,我们需要了解待读写的DDR存储颗粒的型号。只有确定了型号,才能对MIG IP核进行正确地设置。这里我们以型号为MT41J256M16HA-125的DDR颗粒举例。 DDR颗粒的型号命名规则如下图所示:

ZYNQ--MIG核配置

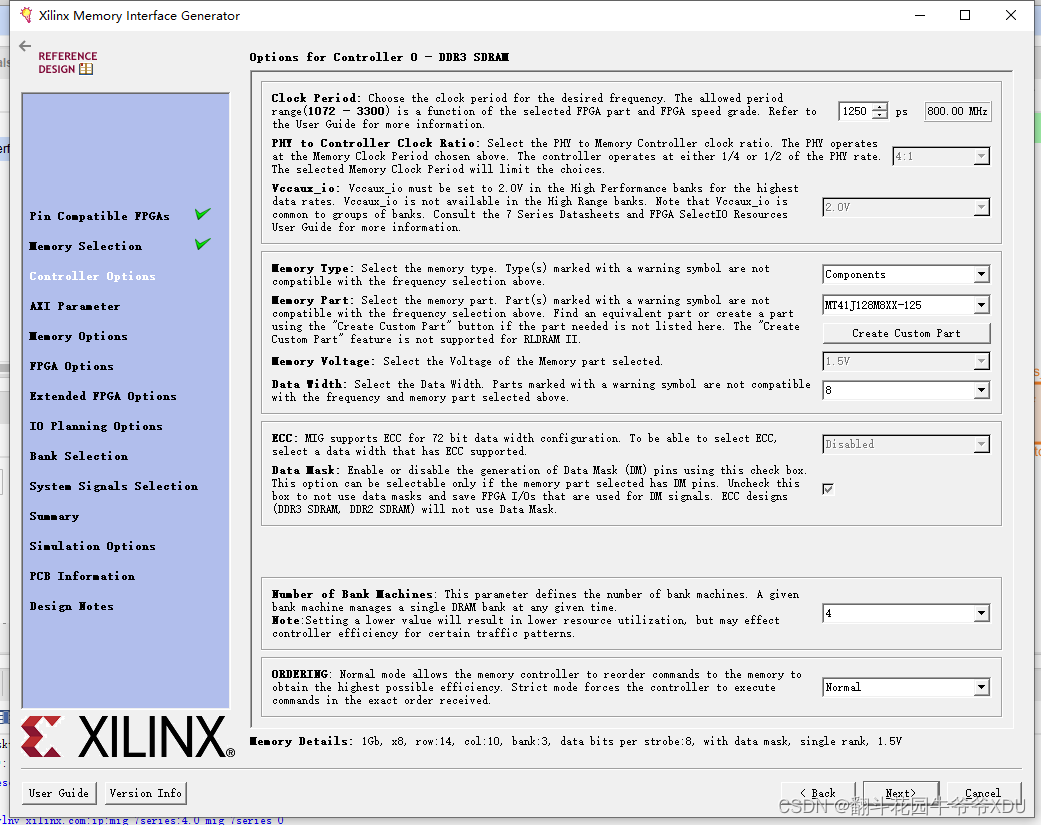

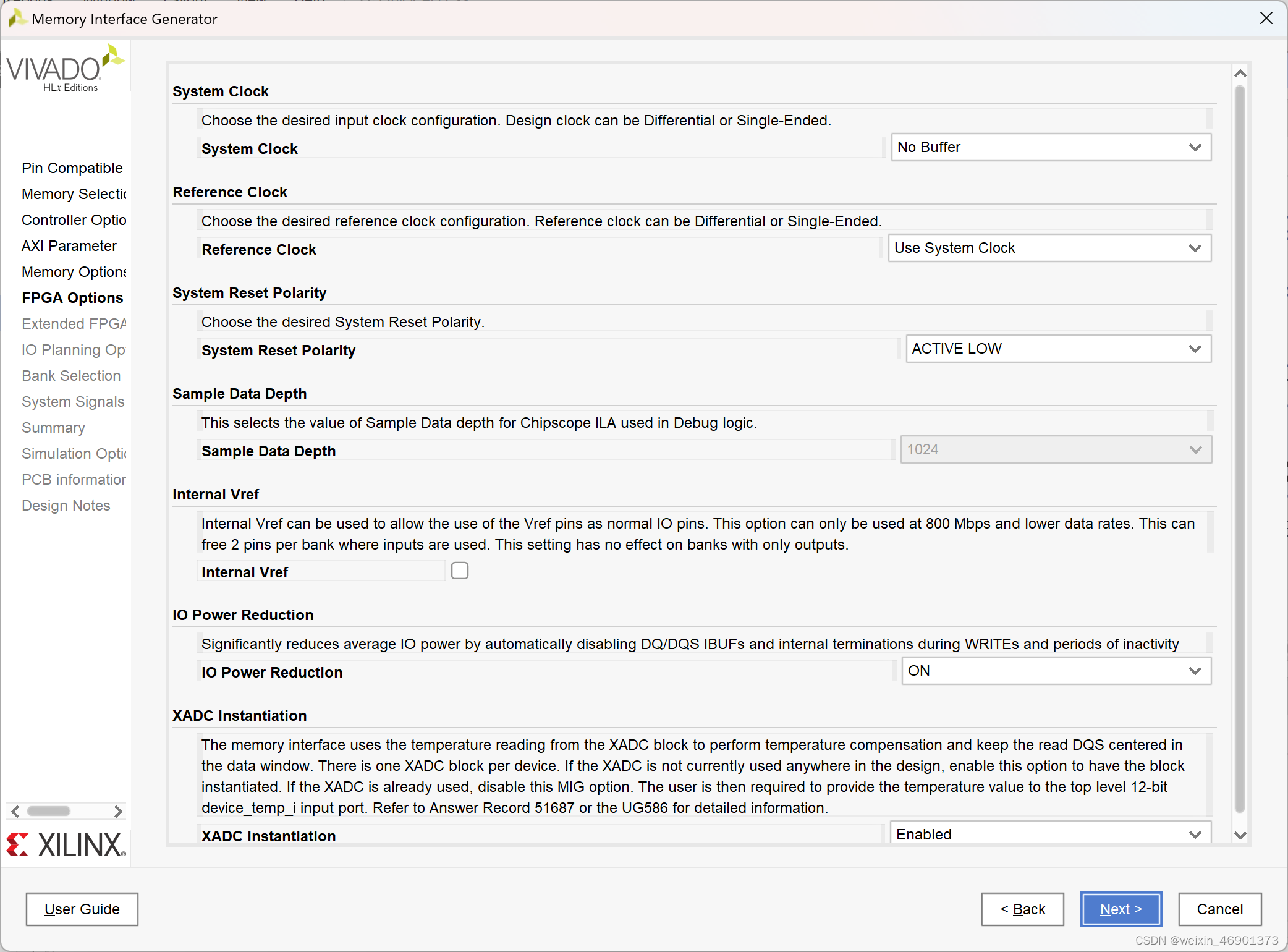

文章目录 MIG核配置界面多通道AXI读写DDR3 MIG核配置界面 Clock Period: DDR3 芯片运行时钟周期,这个参数的范围和 FPGA 的芯片类型以及具体类型的速度等级有关。本实验选择 1250ps,对应 800M,这是本次实验所采用芯片可选的最大频率。注意这个时钟是 MIG IP 核产生,并输出给 DDR3 物理芯片使用的,它关系到 DDR3 芯片具体的运行

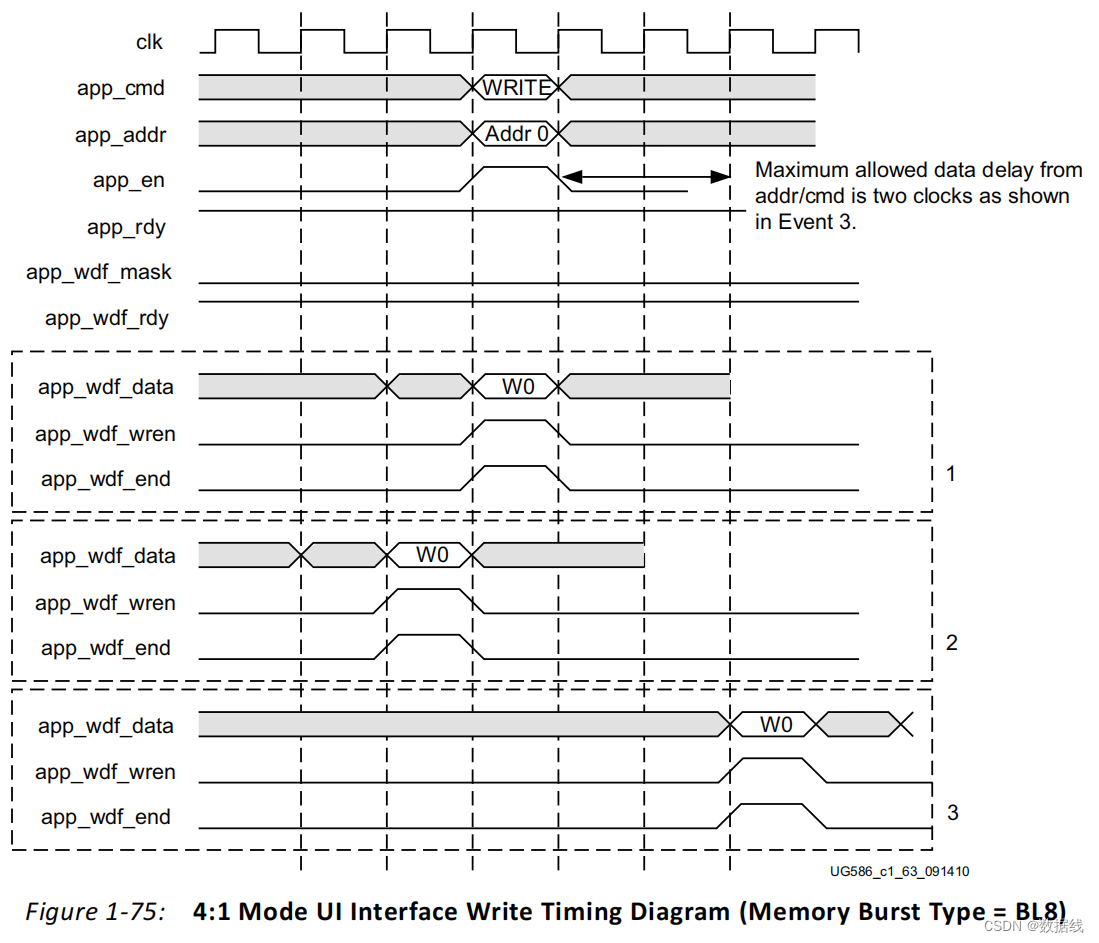

Vivado MIG ip核使用教程(二)

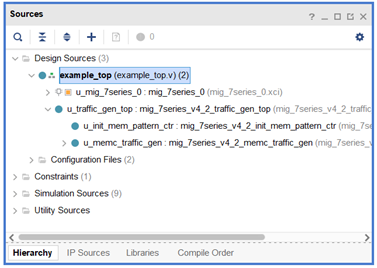

总目录 Vivado MIG ip核使用教程(一) Vivado中MIG ip核的生成流程 Vivado MIG ip核使用教程(二) Vivado中MIG ip核的各个接口介绍 本节目录 1 时钟和复位2 Memory interface ports3 Application interface ports3.1 基本接口3.2 读数据接口3.3 写数据接口3.4 其他接口

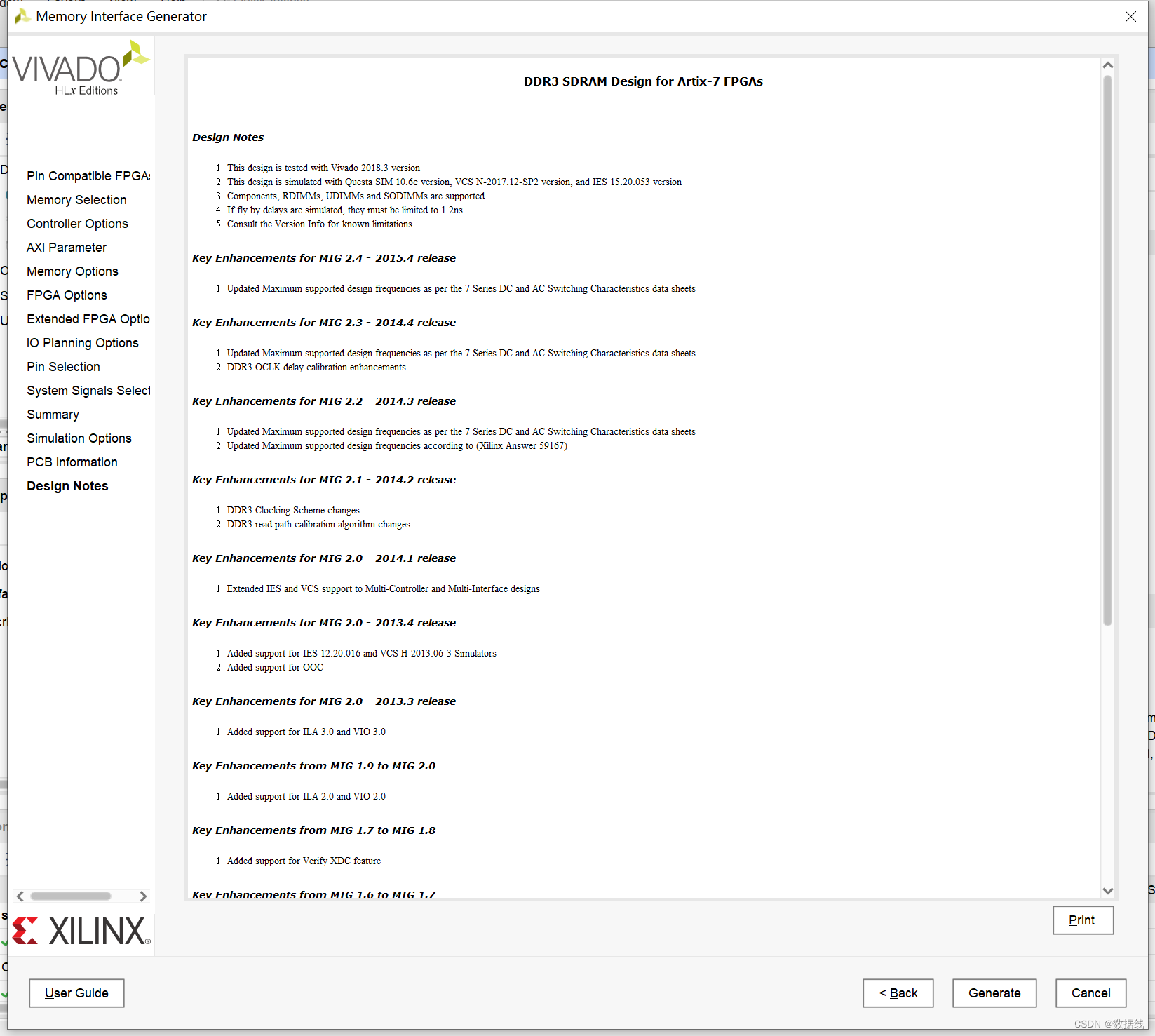

Vivado MIG ip核使用教程

Step 1 在ip catalog中搜索mig ip核并打开,检查硬件配置 Step 2 Step 3 选择对其他芯片类型的兼容性,若无此方面需求,可直接点击next Step 4 选择存储器类型 Step 5 配置DDR3芯片工作频率、用户时钟、mig ip核输入时钟、DDR3芯片类型、突发类型、寻址方式等 Step 6 配置FPGA提供给mig ip核的系统时钟、参考时

DDR3控制器(MIG)各个时钟的含义

首先要知道DDR3的一些时钟含义: 1.DDR3接口时钟:也就是DDR3接口传输速率 2.等效时钟:因为数据在接口双沿采样,因此等效时钟为接口时钟的两倍。 3.DDR3芯片内核工作时钟:DDR3存储芯片内部存储阵列的时钟。 clock period这里就是DDR3接口时钟频率。 PHY to Controler CLock Ratio:2:1或者4:1; 4:1:接口时钟频率为400MHZ,那

【逻辑学习笔记】MIG中各种时钟的含义和如何设置

目录 MIG整体介绍 MIG的时钟架构 MIG配置过程中时钟的含义和设置 Clock Period PHY to Controller Clock Ratio VCCAUX_IO Input Clock Period System Clock Reference Clock MIG整体介绍 MIG的时钟架构 从上面的时钟架构中,可以看出,有以下几种

Xilinx DDR4 MIG 的调试

平台:Vivado2021.1 芯片:xcku115-flva1517-2-i (active) 语言:VerilogHDL 参考文件:pg150.下载地址 pg150-ultrascale-memory-ip.pdf • 查看器 • AMD 自适应计算文档门户 (xilinx.com) DDR4介绍 DDR4,即第四代双倍数据率同步动态随机存储器SDRAM。前面我们学习过DDR3,D

xilinx_FPGA_MIG_DDR3读写控制

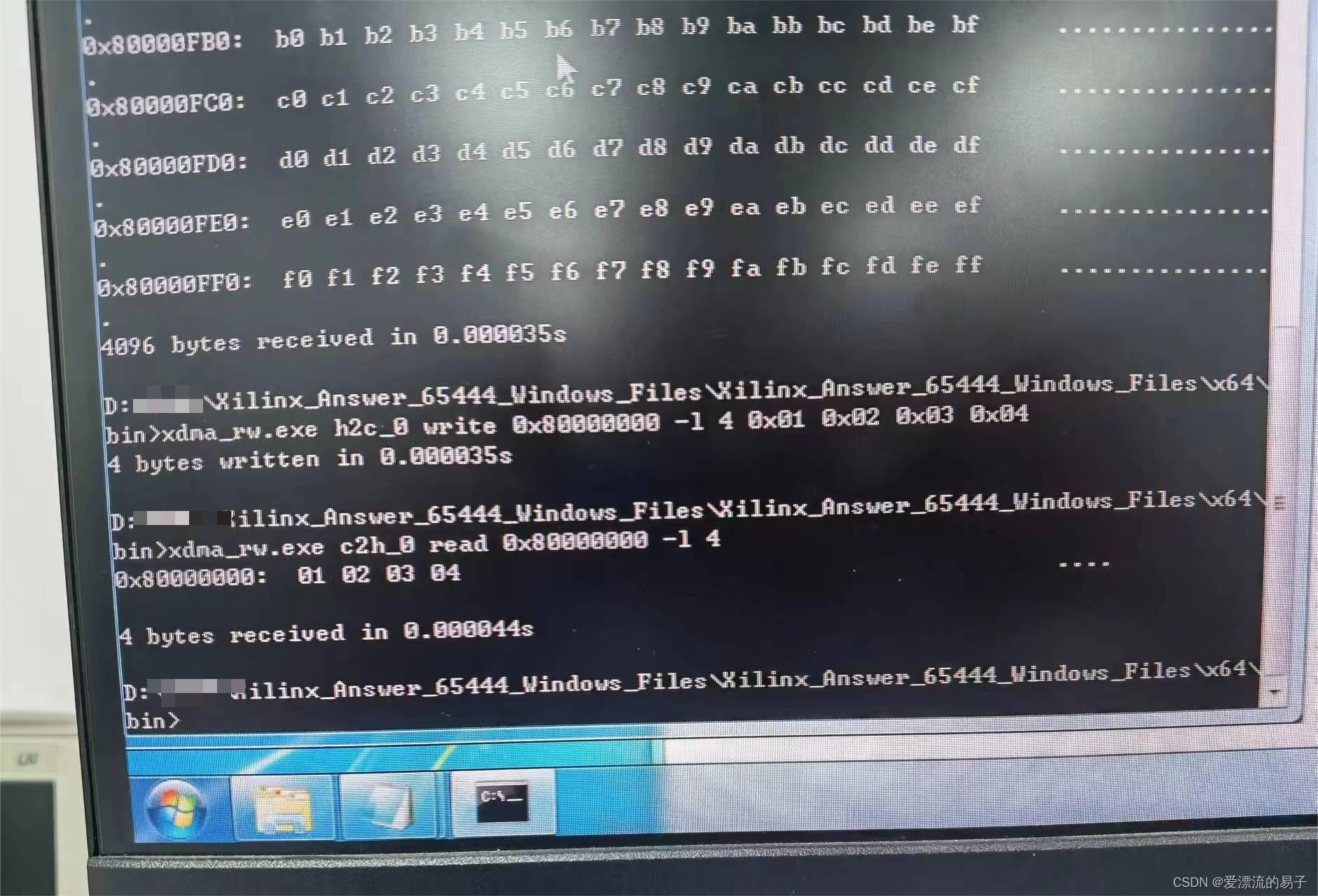

Xilinx MIG UART控制DDR3读写 使用的硬件平台时Kintex7_ECO开发板硬件参数: FPGA型号:xc7k325tffg676-2 DDR3:MT41J256M16 开发环境:Vivado2020.1 功能概述: 通过串口控制DDR3的读写操作,串口终端发送写数据协议(包含协议头55 AA)、读写命令字、读写数据的基地址、读写数据长度,串口模块接收数据发送到协议解析模块,协

DDR-MIG 学习记录

MIG调试总结: 对vivado软件中用于控制DDR2 / DDR3 的 控制器MIG(Memory Interface Generator)IP核进行了仿真测试,以学习如何用IP核来控制FPGA板载SDRAM的读写。我们只需要学会MIG的接口控制就可以。 ①配置IP核 Xilinx 的 DDR 控制器的名称简写为 MIG(Memory Interface Gen

DDR-MIG 学习记录

MIG调试总结: 对vivado软件中用于控制DDR2 / DDR3 的 控制器MIG(Memory Interface Generator)IP核进行了仿真测试,以学习如何用IP核来控制FPGA板载SDRAM的读写。我们只需要学会MIG的接口控制就可以。 ①配置IP核 Xilinx 的 DDR 控制器的名称简写为 MIG(Memory Interface Gen

Xilinx DDR3 MIG系列——项目开发内容介绍及目录

本节目录 一、Xilinx DDR3 MIG项目背景二、Xilinx DDR3 MIG项目学习路线三、Xilinx DDR3 MIG项目目录 订阅本专栏内容的者,可获取任一一份工程源码。具体获取方式,系列文章更新完成后,关注微信公众号“小灰灰的FPGA”,将自己的订阅信息以及所需要的项目,截图并私信给作者。 本节内容 一、Xilinx DDR3 MIG项目背景 对于FPGA开发工作

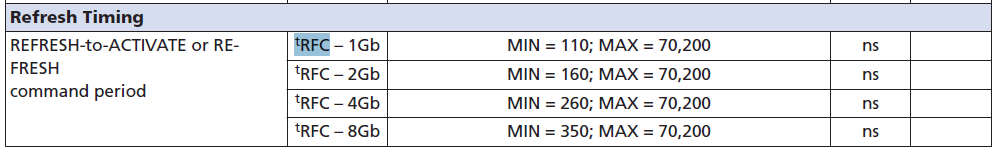

VIVADO MIG核添加列表之外的DDR型号

VIVADO MIG列表支持的DDR型号有限,很多时候需要添加列表之外的DDR型号,我们以MT41K128M16JT-125:K为例进行介绍。 第一步,打开MIG,点击Creat Custom Part。 第二步,输入相应的参数即可,所有参数在Datasheet中都能找到。

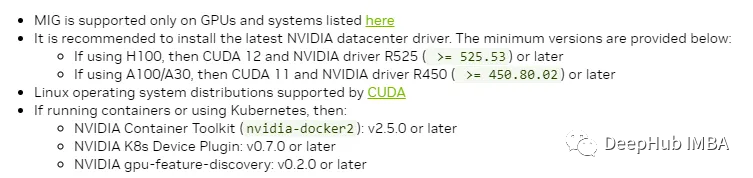

GPU 虚拟化技术MIG简介和安装使用教程

使用多实例GPU (MIG/Multi-Instance GPU)可以将强大的显卡分成更小的部分,每个部分都有自己的工作,这样单张显卡可以同时运行不同的任务。本文将对其进行简单介绍并且提供安装和使用的示例。 什么是MIG NVIDIA Multi-Instance GPU (MIG) 技术是 NVIDIA 推出的一种 GPU 虚拟化技术,允许一块物理 GPU 被分割成多个独立的 GPU 实例,