本文主要是介绍DDR引脚绑定之路,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1 。 EC4CE40F23C8使用quartus13.1 生成DDR2 SDRAM IP 软核。估计是由于版本太低,找不到自己对应的DDR型号:MT47H128M16RT-25E。

使用相近的型号,参考规格书,修改DDR型号参数,就是几个T

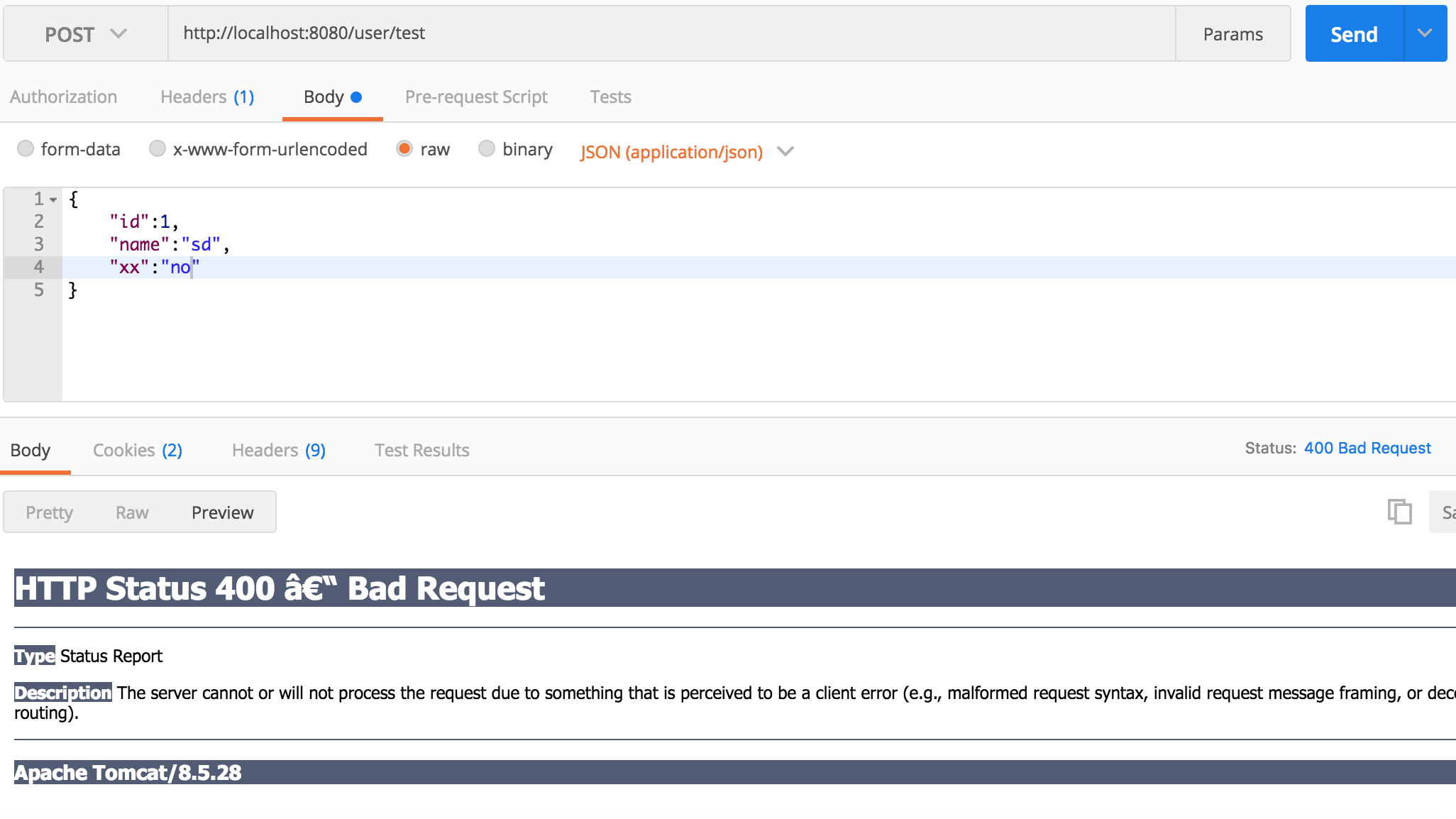

2. 按照硬件工程师原理图绑定管脚,发现出错:1、Error (165050): The assigned location PIN B13 for DQ pin "DDR2A_DQ2" is not a legal location。

参考网上大佬:https://www.cnblogs.com/fhyfhy/p/7657509.html解释:

2.1 DDR控制信号和地址信号可以放到普通IO。

2.2 上面的错误提示是”DDR2A_DQ2”放在了一个非法的地方,也就是放错了地方。对于DDR3/DDR2 IP的DQ,DQS,DM信号在FPGA上对应的pin不是 想当然的随便放置,他们有固定的位置,一般要遵循下面的几个规则:DQS信号必须连接到FPGA的引脚名带有DQS的pin(

这篇关于DDR引脚绑定之路的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!