本文主要是介绍Xilinx FPGA 支持双通道DDR,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

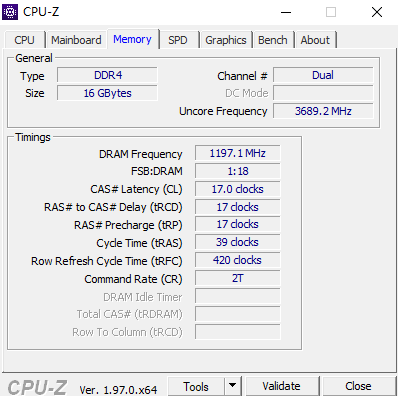

1,双channel对应于两个DDR MC控制器,既然是双channel,那么两个channel之间必然要做数据同步,组合成更高位宽的DDR。因此对于多die器件,在布局上首先要保证两个channel处于同一个SLR。现在笔记本大多是双通道内存设计,可以用CPU-Z查看:

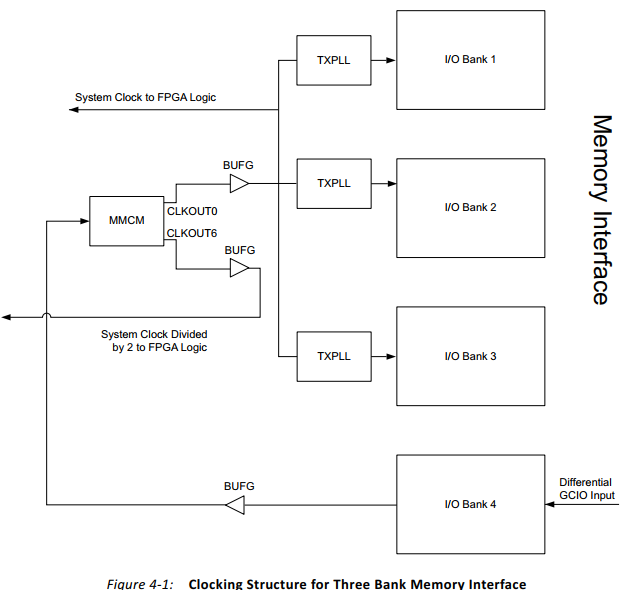

2,时钟结构

操作记录:

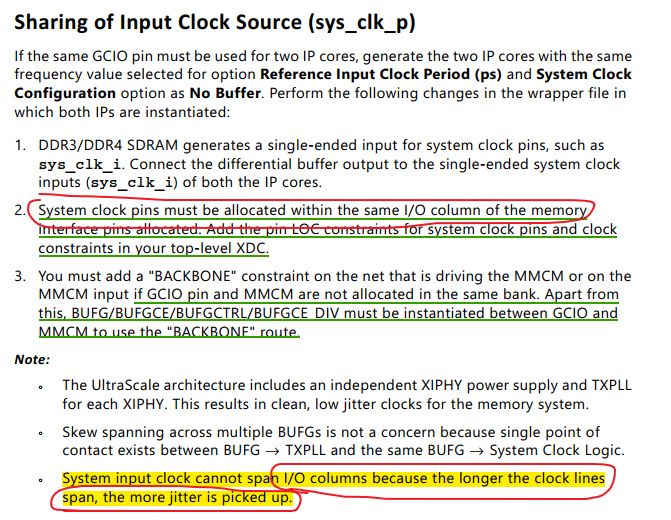

1,两个通道共用主时钟和逻辑复位

2,两个通道均为72bit不能满足同SLR并且同COLUMN的要求(因为一个COLUMN只有

5个BANK,每个DDR控制器要3个BANK)

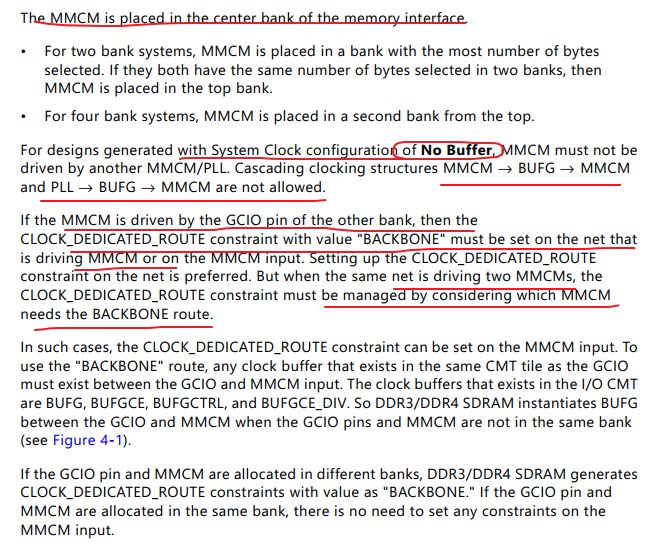

如果时钟源不在中间BANK时钟输入,则需要增加BUFG以及BACKBONE约束:

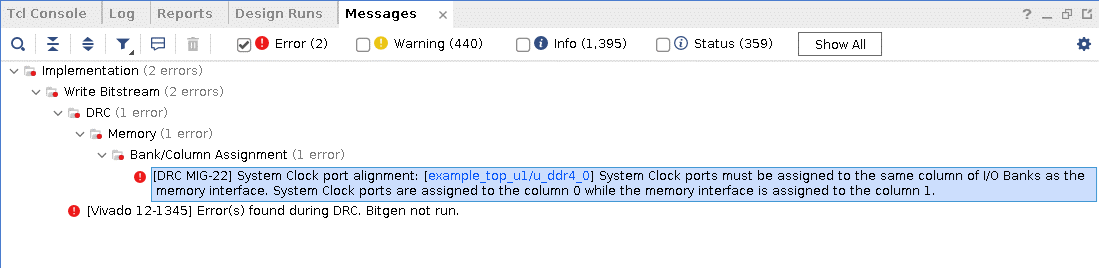

由于无法满足同COLUMN要求:

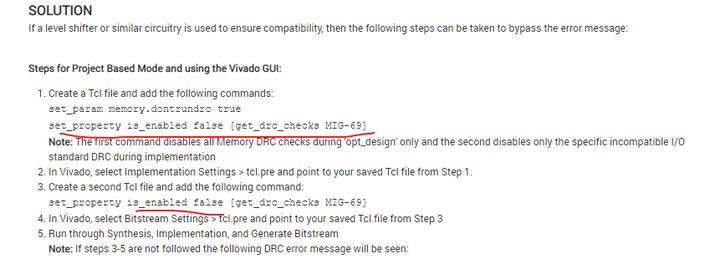

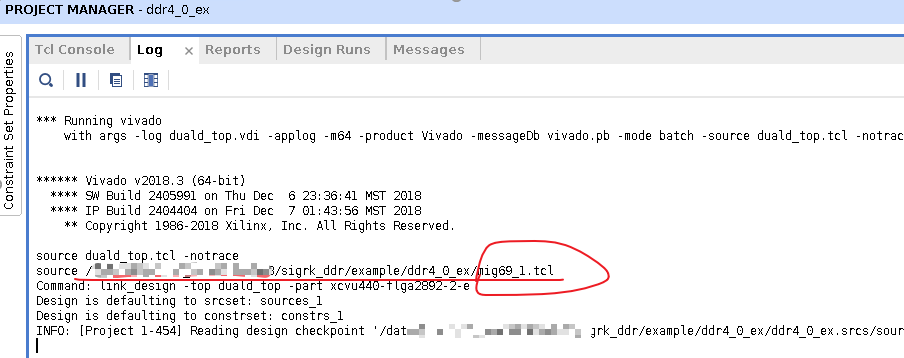

由于跑的频率比较低,尝试关闭DRC测试:(另一种方案是外部输入两个同源时钟,但好像没有意义,DRC肯定不会报错,每个DDR控制器都会有各自的MMCM产生各自独立的用户时钟,两个时钟即使配置一样也应该看为异步关系)

Xilinx Customer Community

DDR控制器共用时钟源:

参考:

1,

超能课堂(202):关于DDR4内存颗粒、单双面、主板布线和双通道的那些事儿 - 超能网

2,

https://www.xilinx.com/support/documentation/ip_documentation/mig/v4_2/pg150-ultrascale-mis.pdf

3,

Xilinx Customer Community

--------------------------

首发地址:timewh - 知乎

这篇关于Xilinx FPGA 支持双通道DDR的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!