本文主要是介绍ARM v8 Cortex R52内核 02 程序模型 Programmers Model,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

ARM v8 Cortex R52内核 02 程序模型 Programmers Model

2.1 关于程序模型

Cortex-R52处理器实现了Armv8-R架构。这包括:

-

所有的异常级别,EL0-EL2。

-

每个异常级别下的AArch32执行状态。

-

T32和A32指令集,其中包括:

-

浮点运算。

-

可选的高级SIMD操作。

-

2.1.1 Advanced SIMD and Floating-point

高级SIMD是一种媒体和信号处理体系结构。浮点执行单精度和双精度浮点操作。

注意:高级SIMD及其相关实现和支持软件通常被称为NEON技术。

所有高级SIMD和浮点运算都是A32和T32指令的一部分。

2.1.2 Generic Interrupt Controller 通用中断控制器

Cortex-R52处理器不支持以下GIC版本3的功能:

-

1of N中断分发。

-

特定区域的外设中断(LPIs)。

-

中断转换服务(ITS)。

2.1.3 Jazelle implementation

处理器支持一个简单的Jazelle®实现。这意味着:

- 不支持Jazelle状态。

- BXJ指令的行为与BX指令相同。

在简单的Jazelle实现中,处理器不会加速执行任何字节码,并且Java虚拟机(JVM)使用软件例程来执行所有字节码。

2.1.4 Instruction set states

处理器通过 PSTATE.T 位控制两种指令集状态:

A32 处理器执行32位、字节对齐的A32指令;

T32 处理器执行16位和32位、半字节对齐的T32指令。

2.1.5 Memory Model 内存模型

Cortex-R52处理器将内存视为一个按升序编号的线性字节集合。例如,字节0-3保存第一个存储的单词,而字节4-7保存第二个存储的Word。

处理器可以以两种方式访问内存中的word:

- 大端格式;

- 小端格式;

注意:指令总是小端格式。

2.1.6 Security state 安全状态

Cortex-R52处理器不实现TrustZone®技术,无法区分安全和非安全的物理内存。

2.2 Armv8-R AArch32 architecture concepts

Cortex-R52处理器的程序员模型主要由其实现的架构定义。本手册不包含对架构程序员模型的重复描述。本手册描述了特定于Cortex-R52处理器实现的功能和行为。

以下部分介绍了在本文档其余部分中使用的主要架构概念和术语。更多详细信息,请参阅Arm® Architecture Reference Manual Supplement Armv8,针对Armv8-R AArch32体系结构配置文件。

注意:阅读本手册的先决条件是理解本节中定义的术语。

2.2.1 Execution state 执行状态

Armv8-R AArch32架构只有一个执行状态,即AArch32。执行状态定义了处理器的执行环境,包括:

- 支持寄存器的宽度;

- 支持的指令集;

- 重要的方面:

- 执行模型 Execution Model

- PMSA (Protected Memory System Architecture)

- Programmers Model

2.2.2 Exception Levels 异常等级

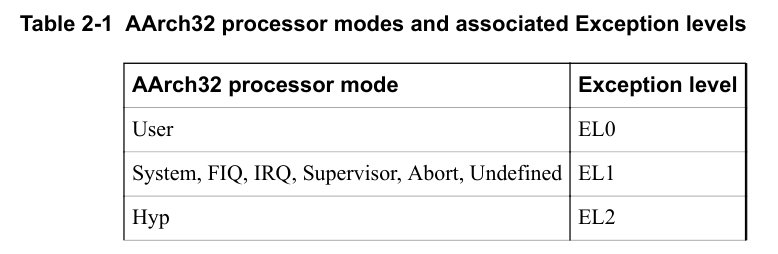

Armv8-R AArch32异常模型定义了EL0-EL2的异常级别,其中:

- EL0具有最低的软件执行特权,而在EL0上的执行被称为非特权执行;

- 增加异常等级,从EL1增加到EL2,表示增加了软件执行特权;

- EL2提供了处理器虚拟化。

执行只能在Armv8-R AArch32异常级别之间进行切换,仅在发生异常时或从异常返回时才会发生切换。

- 在发生异常时,异常级别要么增加,要么保持不变。在发送异常时,异常级别不能减少。

- 在异常返回时,异常级别要么降低,要么保持不变。从异常返回时,异常级别不能增加。

执行过程切换或者保持异常等级被称为异常目标的异常级别,和:

-

每种异常类型都有一个目标异常级别,可以是以下两种情况之一:

-

异常的性质中隐含的。

-

在系统寄存器中通过配置位定义的。

-

-

异常不能针对EL0。

2.2.3 典型的异常等级使用模型

该架构并未规定不同异常级别使用的软件,这些选择超出了架构的范围。然而,以下是异常级别常见的使用模型:

- EL0: Application. 应用(用户等级)

- EL1: Os kernel and associated functions that are typically described as privileged. 操作系统内核和相关函数通常被描述为特权级。

- EL2: Hypervisor. 虚拟化

2.2.4 Exception terminology 异常术语

该部分定义了用于描述异常级别之间导航的术语。

关于提出异常的术语

当处理器首次对异常状态做出相应时,会产生一个异常。

此时处理器的状态是从中换取异常的状态,在接收到异常后立即发生的处理器状态是将该异常带入的状态。

关于异常返回的术语

为了从异常中返回,处理器必须执行异常返回指令。当执行返回指令时,处理器状态是从异常中返回的状态。执行该指令后的处理器状态时异常返回到的状态。

Fast interrupts 快速中断

当快速中断打开时,当接收到中断,处理器会放弃任何已经开始但未完成的可重启内存操作。可重启内存操作是加载和存储指令到普通内存。

为了最小化中断延迟,ARM建议不要对设备内存执行多word传输操作。

2.2.5 指令集状态

处理器指令集状态决定处理器执行的指令集。

在AArch32执行状态下执行的指令集有:

- A32: 这是一个使用32位指令编码的固定长度指令集。在Armv8引入之前,它被称为Arm指令集。

- T32: 这是一个可变长度指令集,使用了16位和32位的指令编码。在Armv8引入之前,它被称为Thumb指令集状态。

2.2.6 AArch32 执行模式

当在AArch32状态下处理器能够执行下面几种模式中的一种,每一种模式都与一个异常等级相关联。一些模式是私有的、分行存储的通用目的寄存器。异常会导致处理器去切换到特点模式。

下面的表展示了AArch32处理器模式和每种模式的异常等级:

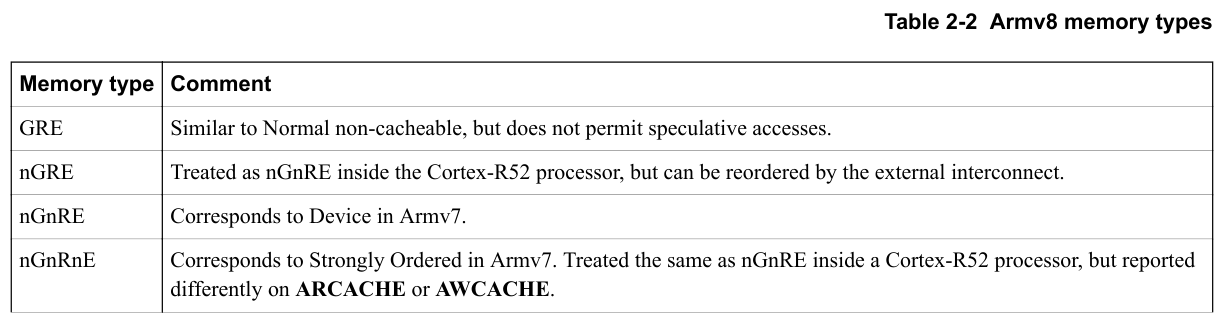

2.2.7 支持ARMv8内存类型

ARM v8提供了互斥的存储类型,内存映射memery map下的每个地址都有一个由MPU确定的内存类型。

地址类型是:

- Normal: 这通常用于大容量内存,包括读写和只读。

- Device: 这通常用于外围设备,可能对读取敏感和写入敏感。ARM架构限制了对访问设备内存怎样被排序、合并或者推测。

ARM v8架构将设备内存细分为几个子类型。这些与以下属性相关:

- G: Gathering. 聚集。将请求收集并合并到一个事务中的能力。

- R: Gathering. 重新排序。具备重新排序转换的能力。

- E: Early-acknowledge. 提前确认。接受来自内联转换提前确认的能力。

下表描述了ARM v8的内存类型:

2.2.8 系统寄存器 System Register

系统寄存器提供控制和状态信息。例如,一个寄存器可以提供有关内核发送异常中断的综合信息,或者提供一个控制来启用或禁止缓存。

系统寄存器使用标准的命名格式,<register_name>,<bit_field_name>,去为了识别特定寄存器以及寄存器内的控制和状态位。位也可以通过他们数字的位置来描述,即 <register_name>[x:y]或者通用形式bits[x:y].

系统寄存器包括:

- ID寄存器

- 通用系统控制寄存器

- Debug调试寄存器

- 通用时钟寄存器

- 性能监控寄存器

- GIC 通用中断控制器CPU接口寄存器

2.2.9 通用目的寄存器

Armv8-R AArch32架构提供了对15个32位通用寄存器R0-R14的访问。其中,有两个具有特殊或受限制的使用方式:

- R13 通常被标识为SP,即堆栈指针;

- R14通常被表示为LR,即链接寄存器。

还有一个32位的程序计数器(PC),R15。

其中一些寄存器是分段的。这些是通过使用相同标识符访问多个物理寄存器,并且执行模式决定了访问哪一个。例如:

- 在中止模式下,对SP的访问会访问物理寄存器SP_abt。

- 在用户模式下,对SP的访问会访问物理寄存器SP_usr。

- 在虚拟化监管者模式下,还有一个额外的专用链接寄存器ELR_hyp。

额外的一组寄存器被高级SIMD和浮点指令使用。这些寄存器可以作为32位单精度寄存器S0-S31访问,也可以作为64位双精度寄存器D0-D31或128位四重精度寄存器Q0-Q15访问,但这些只是相同数据的不同视图。数据可以在高级SIMD和浮点寄存器与整数寄存器之间传输。

2.2.10 程序状态寄存器

程序船台寄存器是Current Program Status Register (CPSR),Application Program Status Register (APSR),和Saved Program Status Register(SPSR ).

CPSR保存的信息包括:

- 可以由某些指令设置的标志位,用于确定其他指令的行为。

- 反映处理器当前模式和其他状态的状态位。

- 确定中断屏蔽和数据字节序等控制位。

在CPSR的许多位都受限使用和仅仅被修改在:

- 特权模式;

- 作为异常或异常返回的副作用。

在运行于异常级别EL0的应用程序中,CPSR所呈现的视图被称为APSR。

每个可以引发异常的模式都有自己的SPSR。当发生异常时,每个SPSR用于保存CPSR的副本,以便在异常返回时恢复它。

2.2.11 数据类型

ARM v8 AArch32架构内核支持以下整数数据类型:

- Byte (8 bits).

- Halfword (16 bits).

- Word (32 bits).

- Doubleword(64 bits).

Armv8-R AArch32架构还支持半精度、单精度和双精度浮点数据类型。

2.2.12 内存模型 Memory Model

Armv8-R AArch32架构定义了PMSAv8内存模型,该模型确定了

-

指令和数据的内存访问方式的排序规则和其他限制。

-

MPU决定了内存访问的权限和其他属性。

Cortex-R52支持PMSAv8,并且没有MMU或地址转换功能。尽管MPU不执行任何实际的转换,但该功能仍然通常被称为转换。这是因为物理地址始终与虚拟地址相同。虚拟和物理地址指的是在转换过程之前由指令生成的地址以及在总线上可见的转换过程之后的地址。对于Cortex-R52来说,虚拟和物理地址可以视为同义词。

2.2.13 GIC Architecture

Cortex-R52处理器支持GIC架构的三个组件:分发器、重新分配器和CPU接口。

分发器包含支持SPI的寄存器,还包括计算每个核心最高优先级待处理中断的优先级逻辑。重新分配器包含支持PPI和SGI的寄存器。CPU接口跟踪当前运行的优先级和虚拟中断,并确定核心是否被中断。

中断被配置为边沿触发或电平敏感。每个中断都有可编程的使能、优先级(0-31)、组别(0或1)和路由(仅适用于SPI)配置以及当前状态。

当接收到中断信号时,它会被挂起。根据其配置,一个被挂起的中断可能会打断核心的执行。软件可以读取中断的ID,这将激活它并产生副作用。软件也可以结束一个中断,从而使其失效。

虚拟中断是由虚拟机监控程序软件写入CPU接口的列表寄存器而创建的,通常是作为对物理中断的响应。虚拟中断与物理中断类似地处理,但只能在核心处于EL0或EL1状态时进行中断。当一个虚拟中断被停用时,可以配置它以使得当虚拟中断被停用时,相应的物理停用消息也会发送到GIC分发器。

翻译来源:

Arm® Cortex®-R52 Processor Technical Reference Manual.

这篇关于ARM v8 Cortex R52内核 02 程序模型 Programmers Model的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!