本文主要是介绍自锁电路设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

自锁电路设计

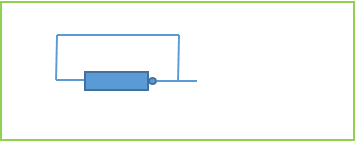

Hi,uu们,是不是经常要用到自锁电路,通常不是使用555芯片就是用比较器来做自锁,今天我们来简单看下自锁电路的设计.图1采用了比较器构建了一个自锁电路,采用低电平复位,当需要复位的时候志需要将反向端的二极管拉低一下即可,免去 三极管控制同相端和电源短接的麻烦。

图1:比较器构建的自锁电路

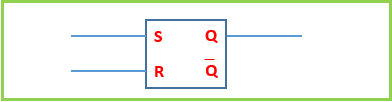

也可以使用555去构建,如下图2所示.

图2:使用555构建的自锁电路

工作原理见555的真值表,真值表如表1所示.

表1:555电路真值表

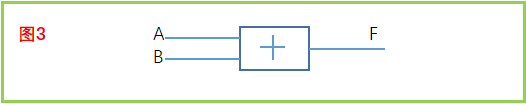

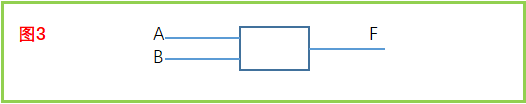

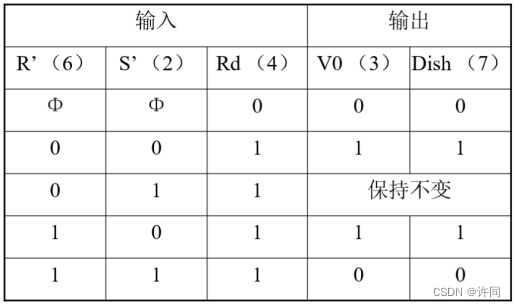

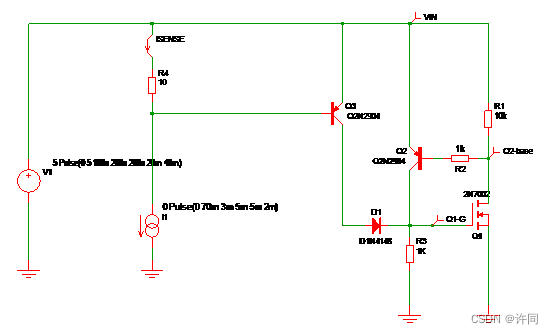

相对来说555还是比较贵,所以我就想能不能有个便宜的方法做个自锁电路,构建电路如下图3所示.

图3:晶体管自锁电路

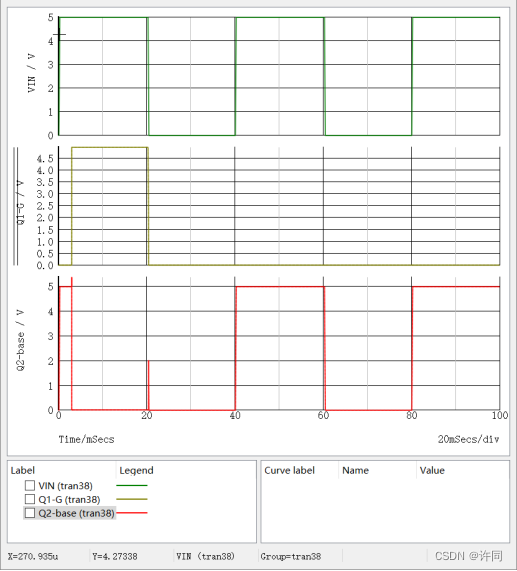

V2做为信号输入,当V2输入一个高电平信号时候,Q1g打开时候Q2-Base拉低,此时Q2导通,此时Q1-G被拉高,Q2-Base被自锁,仿真波形入下图4所示.

图4:仿真波形

仿真代码:

| *#SIMETRIX V1 V1_P 0 5 Pulse(0 5 100u 200u 200u 20m 40m) V2 V2_P 0 5 Pulse(0 5 3m 500n 500n 50u) R1 V1_P R1_N 10k R2 R1_N Q2_B 1k R3 Q2_C 0 1K D1 V2_P Q2_C D1N4148 X$Q1 R1_N Q2_C 0 2N7002 pinnames: D G S Q2 Q2_C Q2_B V1_P 0 Q2N2904 .GRAPH R1_N curveLabel= Q2-base nowarn=true ylog=auto xlog=auto analysis=tran|ac|dc disabled=false PROBEREF=Probe1 .GRAPH V1_P axisType="auto" persistence=-1 curveLabel="VIN" analysis="tran|ac|dc" xLog="auto" yLog="auto" nowarn=true disabled=false PROBEREF=Probe3 .GRAPH Q2_C curveLabel= Q1-G nowarn=true ylog=auto xlog=auto analysis=tran|ac|dc disabled=false PROBEREF=Probe4 .tran 100m |

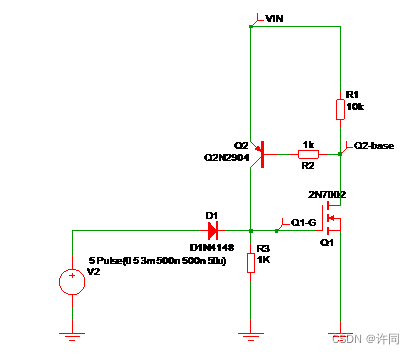

通常自锁电路用于过流保护,所以何不把过流保护一起做掉,简单的过流保护电路如下图5所示.

图5:过流保护自锁电路

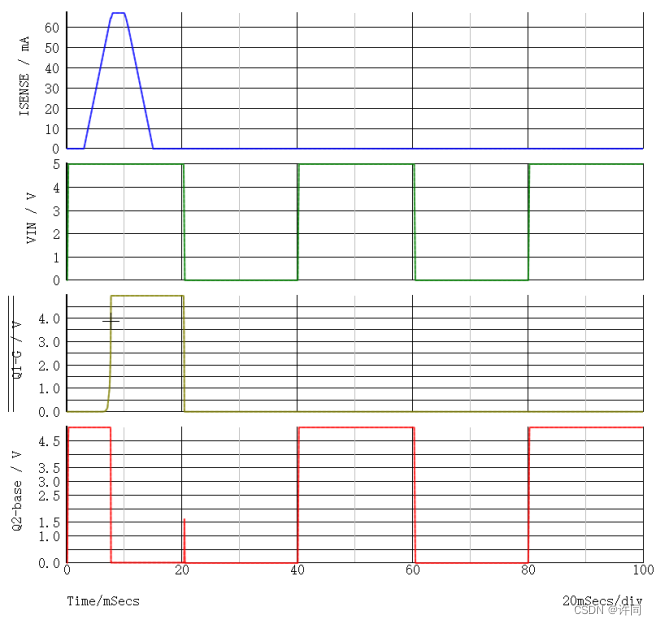

当R4上流过的电流大于Q3的导通压降时候,Q3导通,此时Q1导通完成自锁,如果不需要精确的电流保护值,以上电路足够做过流保护,往往过流保护大于正常工作电流数倍,所以基本上不需要太精确.仿真波形如图6所示.

图6:过流保护电路波形

仿真代码如下所示:

| *#SIMETRIX V1 V1_P 0 5 Pulse(0 5 100u 200u 200u 20m 40m) R1 V1_P R1_N 10k R2 R1_N Q2_B 1k R3 Q2_C 0 1K R4 R4_P R4_N 10 D1 Q3_C Q2_C D1N4148 X$Q1 R1_N Q2_C 0 2N7002 pinnames: D G S Q2 Q2_C Q2_B V1_P 0 Q2N2904 Q3 Q3_C R4_N V1_P 0 Q2N2904 I1 R4_N 0 0 Pulse(0 70m 3m 5m 5m 2m) V$IPROBE1 V1_P R4_P 0.0 .GRAPH IPROBE1#p axisType="auto" persistence=-1 curveLabel="ISENSE" analysis="tran|ac|dc" xLog="auto" yLog="lin" nowarn=true disabled=false .GRAPH R1_N curveLabel= Q2-base nowarn=true ylog=auto xlog=auto analysis=tran|ac|dc disabled=false PROBEREF=Probe1 .GRAPH V1_P axisType="auto" persistence=-1 curveLabel="VIN" analysis="tran|ac|dc" xLog="auto" yLog="auto" nowarn=true disabled=false PROBEREF=Probe3 .GRAPH Q2_C curveLabel= Q1-G nowarn=true ylog=auto xlog=auto analysis=tran|ac|dc disabled=false PROBEREF=Probe4 .tran 100m |

好了,今天就先聊到这里了,拜拜,记得点赞,在看.

关注公众号不迷路

这篇关于自锁电路设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!