本文主要是介绍灵心胜造物,妙手夺天工——Wire Editing(一),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

今天我们要介绍的图形界面工具是Wire Editing。这是我们经常用到的一个修复drc的工具。

想必DRC肯定是每个designer最不想碰到的东西吧,多少个tape out的通宵之夜就花在ECO和修DRC上了。虽说,现在的工具越来越智能,越来越强大,但是每个block跑下来,或多或少,总归有个百十来个DRC被剩下。那这时候怎么办?没关系,我们就得靠我们的双手,来使用Wire Editing。

Wire Editing实现地就是manually画线的功能。当然,这个手动画线的功能不是一般的强大。

但是这功能你要想玩得溜可不容易,首先你得把GUI上的这一排按钮给学会 。

。

下面我就来详细介绍这一排按钮该如何使用。

首先,Wire Editing的对象是Wire。Wire的类型,我们可以分为Regular wire和Special wire。这个大家肯定知道它们的区别吧,Regular wire就是我们平常用的signal wire,用于信号传输线。Special wire就是我们所说的电源线,也就是电源接地线,还有用于flipchip绕线的RDL routing(封装层绕线)。

Regular Wire和Special Wire都需要定义对应的net,spacing和layer值。区别在于Regular Wire需要width是固定的tech lef中layer width值,或者采用定义NDR(non default rule)来修改,通过nanoRouter来生成Regular Via。Special Wire的width是用户自己定义的,通过Via-Gen来生成Special Via。

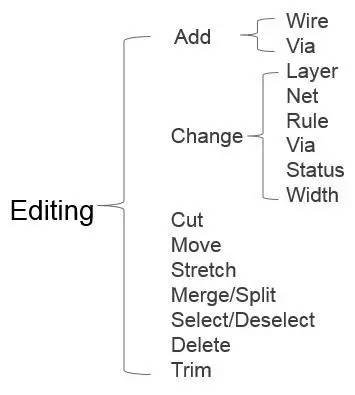

前面说了Wire Editing是一个动作的操作过程,是GUI上的那一排按钮。这些动作和对应的对象可以用下图表示:

1

Add Wire (Basic)

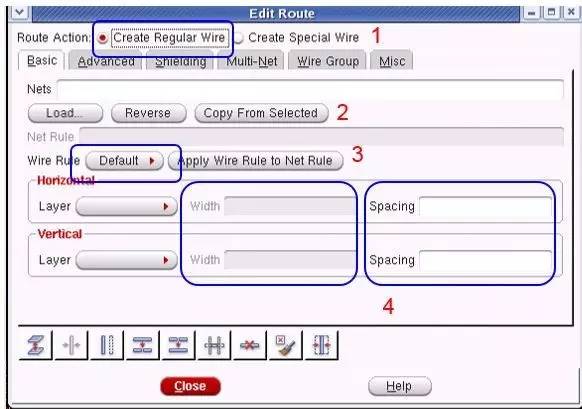

点击GUI上方的 键,或者采用快捷键(Shift+A),进入Add Wire的模式。然后单击“E”键或者“F3”键进行设置。得到如下界面

键,或者采用快捷键(Shift+A),进入Add Wire的模式。然后单击“E”键或者“F3”键进行设置。得到如下界面

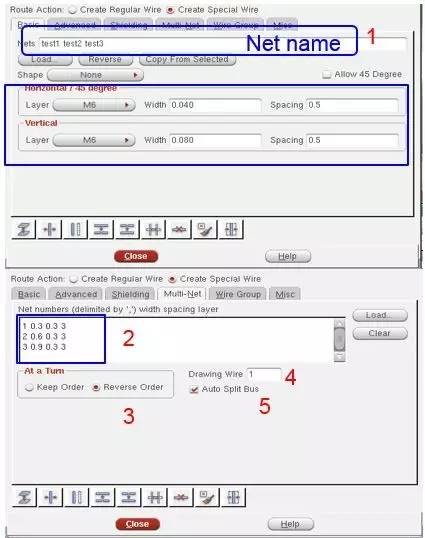

(1)选择创建regular wire还是special wire

(2)输入Net的名字,可以输入多条,或者直接从GUI上copy选中的wire的信息

(3)输入wire的Non Default Rule

(4)指定所要画的Wire的Horizontal和Vertical Layer,Width和Spacing

(5)允许45度的走线,用于Flip chip中的RDL层routing

2

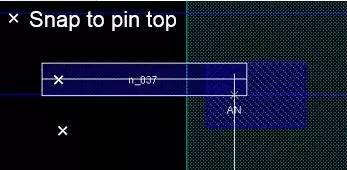

Add Wire (Wire & Via Snap)

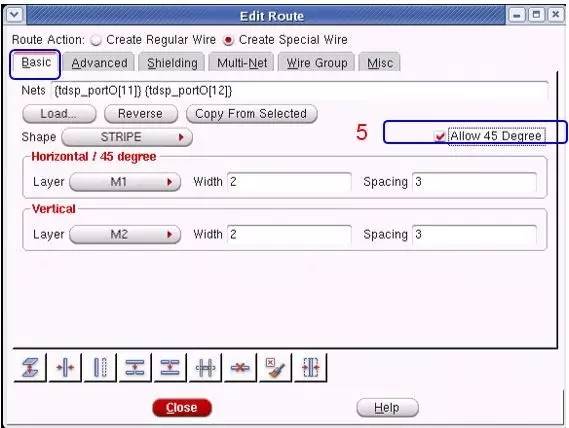

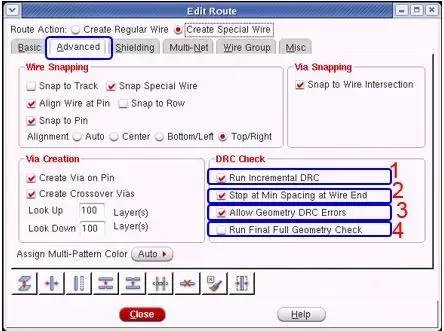

这个界面灵心胜造物,妙手夺天工——Wire Editing(一)可以设定wire和via的snap选项,Regular和Special wire有一定的区别

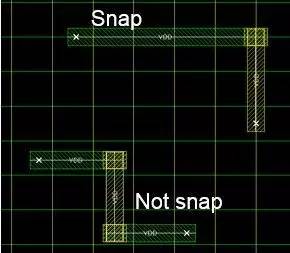

(1)画Regular wire时,自动snap到track上

(2)将Regular wire自动align到pin的方位

(3)自动将via snap到wire的转折点

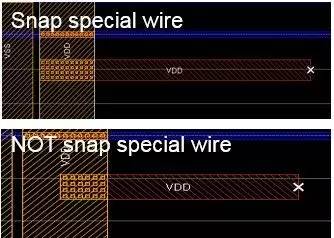

(4)画Special wire时,自动snap到track上

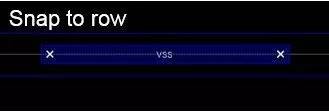

(5)画Special wire时,自动snap到row上

3

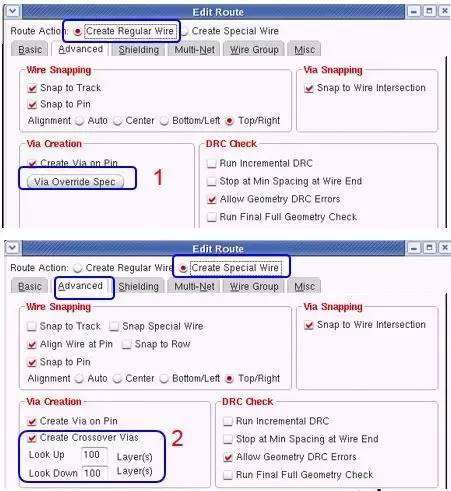

Add Wire(Via creation)

wire edit在画线时,会自动地生成via。下面几个按键可以帮我们控制生成via的属性

(1)自己定义default rule应该选择哪些via,non default rule应该选择哪些via。按照下面的定义规则:

规则:{default via1 via2 ...} {NDR NDRvia1 ...}

例子:{default via12 via23 via45} {SP spvia12}

For the Default rule:

via12 for layer V12

via23 for layer V23

via45 for layer V45

For the non-default rule SP:

spvia12 for layer V12

(2)定义相同Net的不同layer是否要生成Via

Look up, look down layer: 定义在该cut层往上,往下看多少层需要生成Via

4

Add Wire (DRC Check)

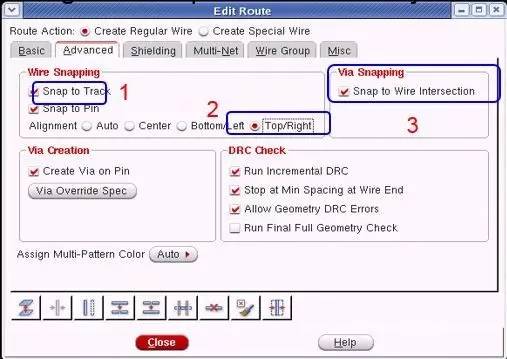

别看wire edit只是画几根线,它的DRC检查机制可是很复杂的呢

(1)画wire时动态地检查DRC

(2)当移动或者拉伸wire时,遇到min spacing的DRC就停止

(3)画wire时是否允许DRC

(4)画完wire后,最后做小范围地检查

5

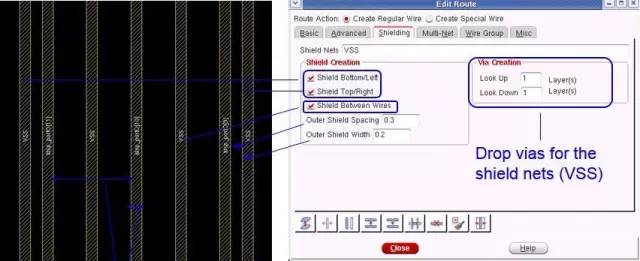

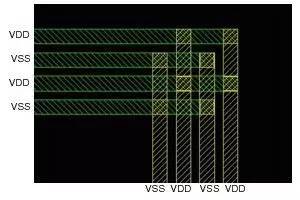

Add Wire (Shielding)

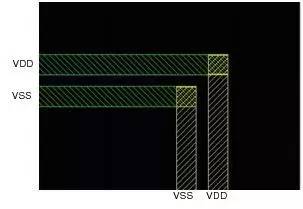

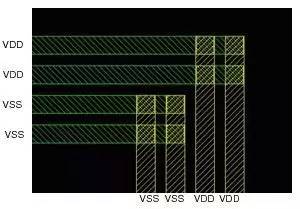

使用这个界面可以给wire加上shielding. 对防止SI效应有作用,这里就不多介绍了。可以选择VSS或者VDD,一般都采用VSS作为shielding net

6

Add Wire (Multi Group)

这个界面可以同时画出多根wire。

(1) 首先需要在Basic form中,指定好多条net

(2) 在框框中填好定义的net的属性

Net number, width, spacing, layer

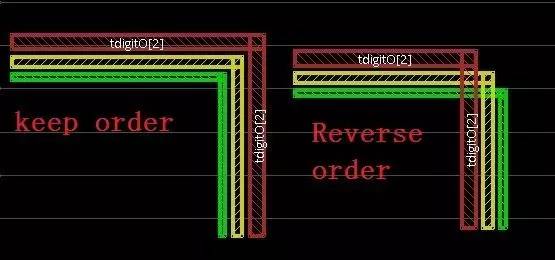

(3) 选择wire拐弯的方向

(4) 画多根wire时,鼠标停留在第几根wire上

(5) 画Bus wire时,遇到障碍物自动分开bus wire

7

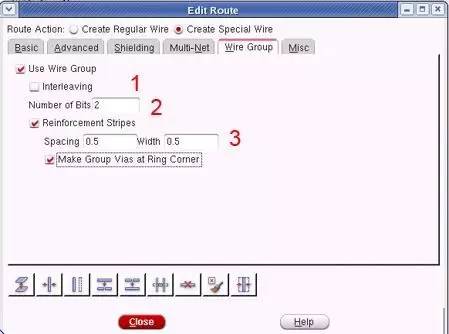

Add Wire (Wire Group)

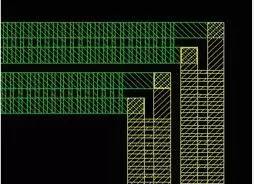

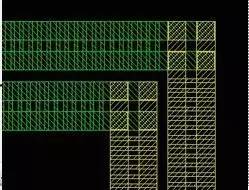

这个命令可以复制多根wire,一起进行操作

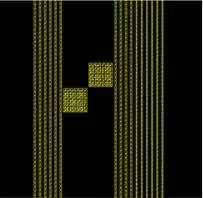

(1)采用wire group,交错画wire

(2)指定wire group中的复制的wire数目

不指定bit

指定bit数为2

(3)在wire中间添加加固线,使得传输能力更强,减小电阻

(4)采用group via

8

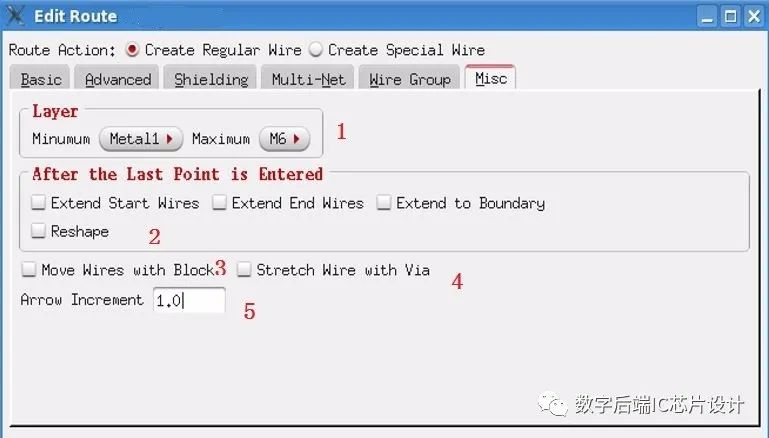

Add Wire (Misc)

最后一个add wire的界面,指定了操作wire的一些其他的option

(1)指定生成wire或者via的最低,最高layer

(2)画完wire时的延伸方向

Extend Start: 延长start起点方向的

Extend End: 延长End终点方向的

Extend to Boundary: 沿着起点或者终点,延长到对应的boundary,必须与前二者同时使用

Reshape: 画完wire后,会自动trim掉多余的wire

(3)移动Block时,wire跟着block一起移动

(4)拉升wire时,via也跟着移动

(5)调整使用键盘上下左右键时,移动的距离

这wire edit功能有点多,界面也有点多,估计也分好几次介绍,虽然上面图片很多,可能有点乱。但这真的是个很强大的工具,大家一定要好好学啊!

下次介绍更加多的Wire editing功能~~

往期回顾

静态时序分析STA合集一

静态时序分析STA合集二

时序基本概念介绍<sdc合集>

数字后端基本概念合集(一)

数字后端基本概念合集(二)

数字后端基本概念合集(三)

Low Power概念介绍合集

数字后端dbGet使用方法合集

号外,数字后端交流群招人啦

IC圈的世界杯 | 论芯片设计的胜利十一人

知否?知否?Block PD应该提交哪些数据?

Timing ECO手修攻略

数字后端面试100问(2019全新版)

数字后端面试100问(校招版)

简历请戳邮箱:taozhang3260@163.com

觉得有用的话,给我点个好看吧

这篇关于灵心胜造物,妙手夺天工——Wire Editing(一)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!