本文主要是介绍vivado WIRE,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

WIRE是用于在Xilinx部件上路由连接或网络的设备对象。一根电线

是单个瓦片内部的一条互连金属。PIP、系紧装置和

SITE_PINs。

提示:WIRE对象不应与设计的Verilog文件中的WIRE实体混淆。那些

电线在设计中与网络有关,而不是与定义的设备的路由资源有关

WIRE对象。

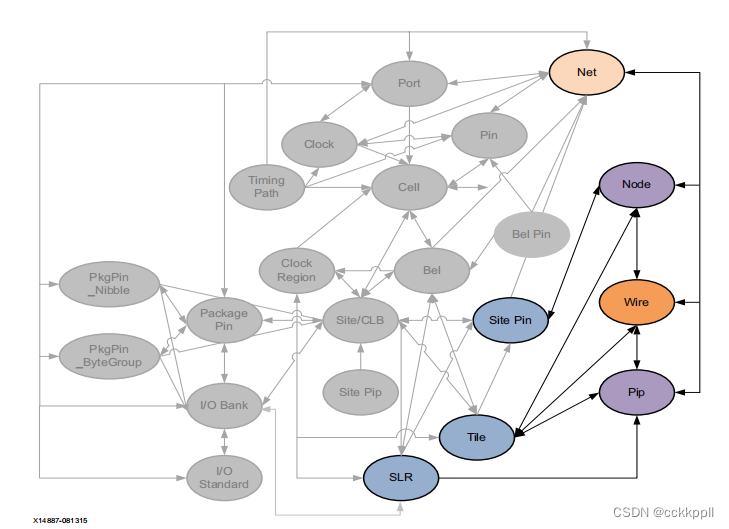

相关对象

如图2-33第119页所示,WIRE对象与TILE、NODE、PIP或NET相关。

您可以使用以下Tcl命令的形式查询WIRE:

get_wires-of[get_tiles INT_R_X7Y47]

您还可以查询WIRE所在的TILE;或相关的NODE和PIP

具有特定WIRE:

get_nodes-of_objects[get_wires INT_R_X7Y47/NW6BEG1]

属性

WIRE对象上的特性可以使用以下命令报告:

report_property-所有[lindex[get_wires-of[get_nodes INT_R_X7Y47/NW6BEG1]]0]

提示:由于设备上的WIRE数量,使用get_WIREs-Tcl命令时不使用

-不建议使用of_objects或-filters来缩小结果范围。

这些属性包括以下内容和示例值:

这篇关于vivado WIRE的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!