wire专题

PyInstaller打包selenium-wire过程中常见问题和解决指南

《PyInstaller打包selenium-wire过程中常见问题和解决指南》常用的打包工具PyInstaller能将Python项目打包成单个可执行文件,但也会因为兼容性问题和路径管理而出现各种运... 目录前言1. 背景2. 可能遇到的问题概述3. PyInstaller 打包步骤及参数配置4. 依赖

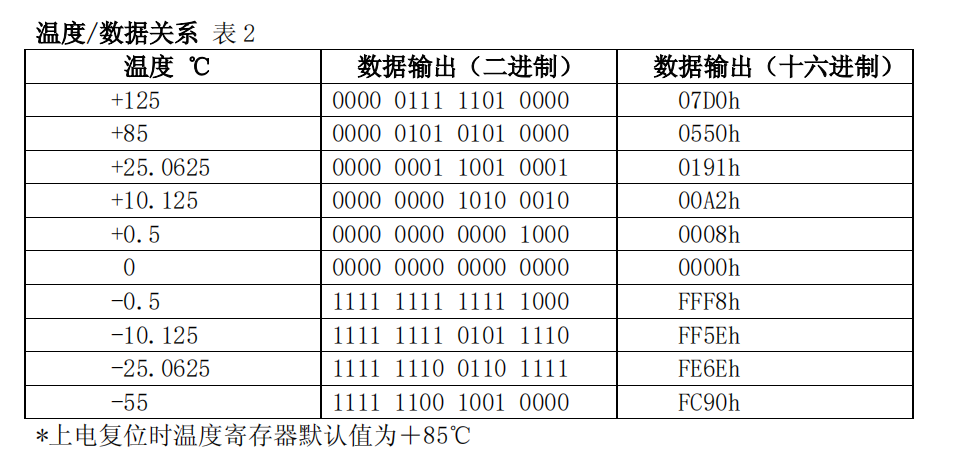

51单片机-第十一节-DS18B20温度传感器(One_Wire单总线)

一、DS18B20温度传感器介绍: DS18B20是一种数字温度传感器。 测温范围:-55C - +125C 通信接口:1-Wire(单总线) 二、引脚及应用电路: 很简单,电源,接地,通讯接口。 三、内部结构: 总图: (1)备用电源 (2)器件地址 (3)控制器 (4)存储器 (5)存储器内部: B1,B2存储最低有效温度和最高有效温度。

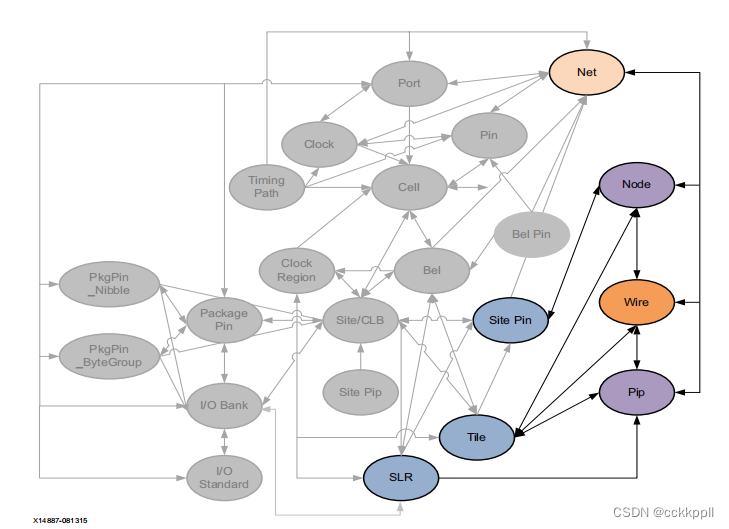

vivado WIRE

WIRE是用于在Xilinx部件上路由连接或网络的设备对象。一根电线 是单个瓦片内部的一条互连金属。PIP、系紧装置和 SITE_PINs。 提示:WIRE对象不应与设计的Verilog文件中的WIRE实体混淆。那些 电线在设计中与网络有关,而不是与定义的设备的路由资源有关 WIRE对象。 相关对象 如图2-33第119页所示,WIRE对象与TILE、NODE、PIP或NET相关。 您可以使用

【无标题】verlog中wire 和reg用法

wire(组合逻辑) wire用来连接模块实例化的输入和输出端口; wire用作实际模块声明中输入和输出; wire 元素必须由某些东西驱动,并且在没有被驱动的情况下,无法存储值; wire 元素不能用在 always模块中 = 或者 <= 的左边; wire元素是assign语句左侧 唯一的合法类型; wire 元素是在基于Verilog的设计中连接两片的无状态方式; wire 只能用在 组合

Verilog中端口应该设置为wire形还是reg形

初学Verilog时,一直搞不清Verilog描述模块时端口应该取什么类型;是reg形?还是wire形?模块对应测试文件的端口类型为什么又与模块的端口类型不一样?因此有必要进行学习与整理: 先写结论: verilog中的端口具有三种传输方向:input、output、和inout,所有的端口均默认为wire类型; 模块描述时,input端口只能为线网形,output端口可以为线网/reg,in

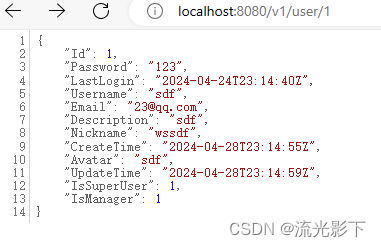

Golang: 依赖注入与wire —— 构建高效模块化应用的秘诀

💝💝💝欢迎莅临我的博客,很高兴能够在这里和您见面!希望您在这里可以感受到一份轻松愉快的氛围,不仅可以获得有趣的内容和知识,也可以畅所欲言、分享您的想法和见解。 推荐:「stormsha的主页」👈,持续学习,不断总结,共同进步,为了踏实,做好当下事儿~ 专栏导航 Python系列: Python面试题合集,剑指大厂Git系列: Git操作技巧GO系列: 记录博主学习GO语言的笔

altera 防止reg/wire 优化

转载:# 关于SignalTap中的节点查找不到的问题_signaltap找不到信号-CSDN博客 关于SignalTap中的节点查找不到的问题 在选择需要查看的信号节点时,有一个信号节点,我翻遍了所有的模块,始终未能看到它的影子,然后上网查了一下,找到了问题所在。 因为在使用quartus编译综合时,某些信号会被优化掉,就会导致在查找此信号节点时,会发现找不见。 解决方法: 1.对

【chisel】chisel怎么给io wire定义初值

在 Chisel 中,为 IO 节点的 Wire 定义初始值通常与特定的信号类型和使用场景有关。以下是一些定义初始值的常见方法: 使用 RegInit 创建寄存器并定义初始值: 当您想要为一个寄存器类型的 Wire 定义初始值时,可以使用 RegInit。以下是一个例子: class MyModule extends Module {val io = IO(new Bundle

[HDLBits] Simple wire

Create a module with one input and one output that behaves like a wire. module top_module( input in, output out );assign out = in; endmodule

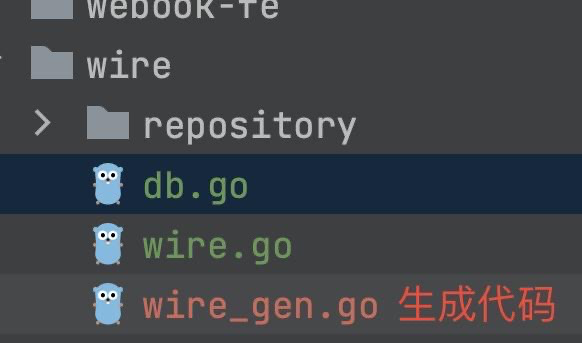

golang beego结合wire依赖注入及自动路由

1 安装wire 1.1 通过命令直接安装 go install github.com/google/wire/cmd/wire@latest 1.2 通过go get方式安装 go get github.com/google/wire/cmd/wire 进入目录编译 cd C:\Users\leell\go\pkg\mod\github.com\google\wire@v0.6.0

golang wire 依赖注入

1 安装wire 1.1 通过命令直接安装 go install github.com/google/wire/cmd/wire@latest 1.2 通过go get方式安装 go get github.com/google/wire/cmd/wire 进入目录编译 cd C:\Users\leell\go\pkg\mod\github.com\google\wire@v0.6.0

Spring auto wire(自动装配) 的 五种方式

Spring auto-wire的 五种方式: 1:no 默认的方式是不进行自动装配,通过手工设置ref 属性来进行装配bean 2:byName 通过参数名 自动装配,如果一个bean的name 和另外一个bean的 property 相同,就自动装配。 3:byType 通过参数的数据类型自动自动装配,如果一个bean的数据类型和另外一个bean的proper

Go 项目依赖注入wire工具最佳实践介绍与使用

文章目录 一、引入二、控制反转与依赖注入三、为什么需要依赖注入工具3.1 示例3.2 依赖注入写法与非依赖注入写法 四、wire 工具介绍与安装4.1 wire 基本介绍4.2 安装 五、Wire 的基本使用5.1 前置代码准备5.2 使用 Wire 工具生成代码 六、Wire 核心技术5.1 抽象语法树分析5.2 模板编程 七、Wire 的核心概念7.1 两个核心概念7.2 Wire 提供

数字后端基本概念介绍Wire

今天我们要介绍的数字后端概念是Wire。需要注意的是,后端工具里面的wire并不是指verilog网表里的wire线型。它是将net物理化的概念,每一条net在后端工具里面是由许多小段的wire组成,每一小段wire我们称之为wire segment. wire按照类型可以分为Regular Wire(信号线),Special Wire(电源线),Patch Wire(补丁线)。 Regu

灵心胜造物,妙手夺天工——Wire Editing(一)

今天我们要介绍的图形界面工具是Wire Editing。这是我们经常用到的一个修复drc的工具。 想必DRC肯定是每个designer最不想碰到的东西吧,多少个tape out的通宵之夜就花在ECO和修DRC上了。虽说,现在的工具越来越智能,越来越强大,但是每个block跑下来,或多或少,总归有个百十来个DRC被剩下。那这时候怎么办?没关系,我们就得靠我们的双手,来使用Wire Editing

请用心画出一个大写的帥——Wire Editing(二)

上次介绍了如何在wire editing中添加一条wire,以及Editing界面中各种option的作用。那其实wire editing还有很多其他action,下面我们就逐个来介绍一下: 1 Move wire 快捷键是M。这边不熟悉的童鞋可能会搞错,GUI上其实有两个move键,,,这两者概念完全不同,虽然都可以移动东西,但是前者用于Floorplan的Object,如果你将它用于移动w

FPGA - 单总线协议(one-wire)

1,简介 单总线(one-wire)是美国 DALLAS 公司推出的外围串行扩展总线技术,与 SPI、I2C 等串行数据通信方式不同,它采用单根信号线,既传输时钟又传输数据,而且数据传输是双向的。它具有节省 I/O口线资源、结构简单、成本低廉、便于总线扩展和维护等诸多优点。 单总线英文名 1-Wire,传输速率一般是 15.3Kbit/s,最大可达 142Kbit/s,通常采用 100Kbit

飞塔防火墙开局百篇——002.FortiGate上网配置——在路由模式下使用虚拟接口对(virtual-wire-pair)

在路由模式下使用虚拟接口对(virtual-wire-pair) 拓扑配置接口配置策略 使用方有透明模式下一进一出的这样需求的组网,可以在路由模式下使用虚拟接口对(virtual-wire-pair)替代。 登陆FortiGate防火墙界面,配置 中文界面。 拓扑 配置接口 选择网络-接口在页面内新建 配置策略 ; wir

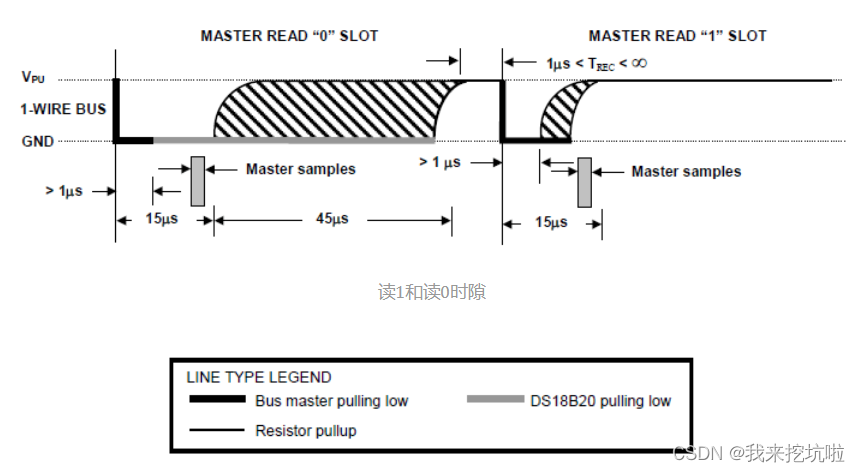

One-wire通信与DS18B20的应用

文章目录 前言一、One-wire通信1.名词解释2.基本通信时序3.具体通信时序4.ROM指令1.Search ROM [F0h] (搜索 ROM指令)2.READ ROM [33h] (读取 ROM指令)3.MATH ROM [55h] (匹配 ROM指令)4.SKIP ROM [CCh] (忽略 ROM指令)5.ALARM SEARCH [ECh] (报警搜索指令) 二、DS18B2

One-wire通信与DS18B20的应用

文章目录 前言一、One-wire通信1.名词解释2.基本通信时序3.具体通信时序4.ROM指令1.Search ROM [F0h] (搜索 ROM指令)2.READ ROM [33h] (读取 ROM指令)3.MATH ROM [55h] (匹配 ROM指令)4.SKIP ROM [CCh] (忽略 ROM指令)5.ALARM SEARCH [ECh] (报警搜索指令) 二、DS18B2

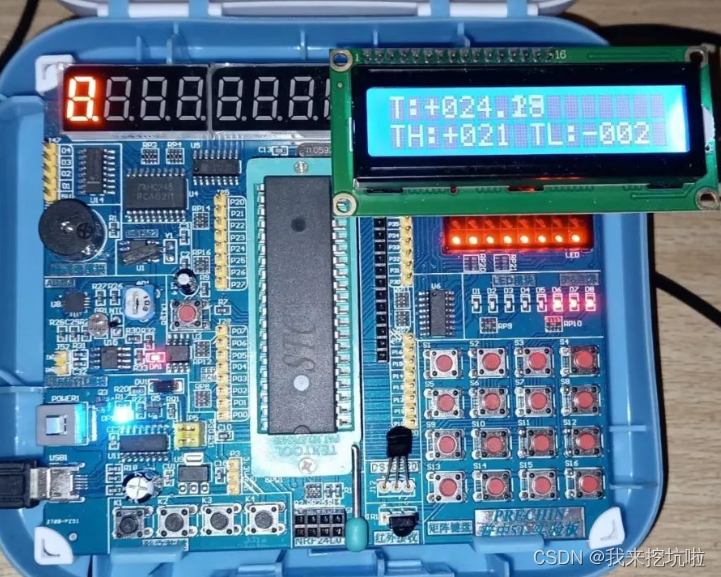

One Wire协议应用篇(c语言板)

一.项目简介 利用DS18B20实时检测温度并显示在LCD1602显示屏上,同时可以通过K1,K2,K3,K4设置最高温度和最低温度利用AT24C02可以实现掉电不丢失,最后当检测温度大于或小于最高温时,会在LCD1602显示屏上显示OV:H或OV:L。 二.准备材料 AT89C52、LCD1602显示屏、4只按键、AT24C02、DS18B20。

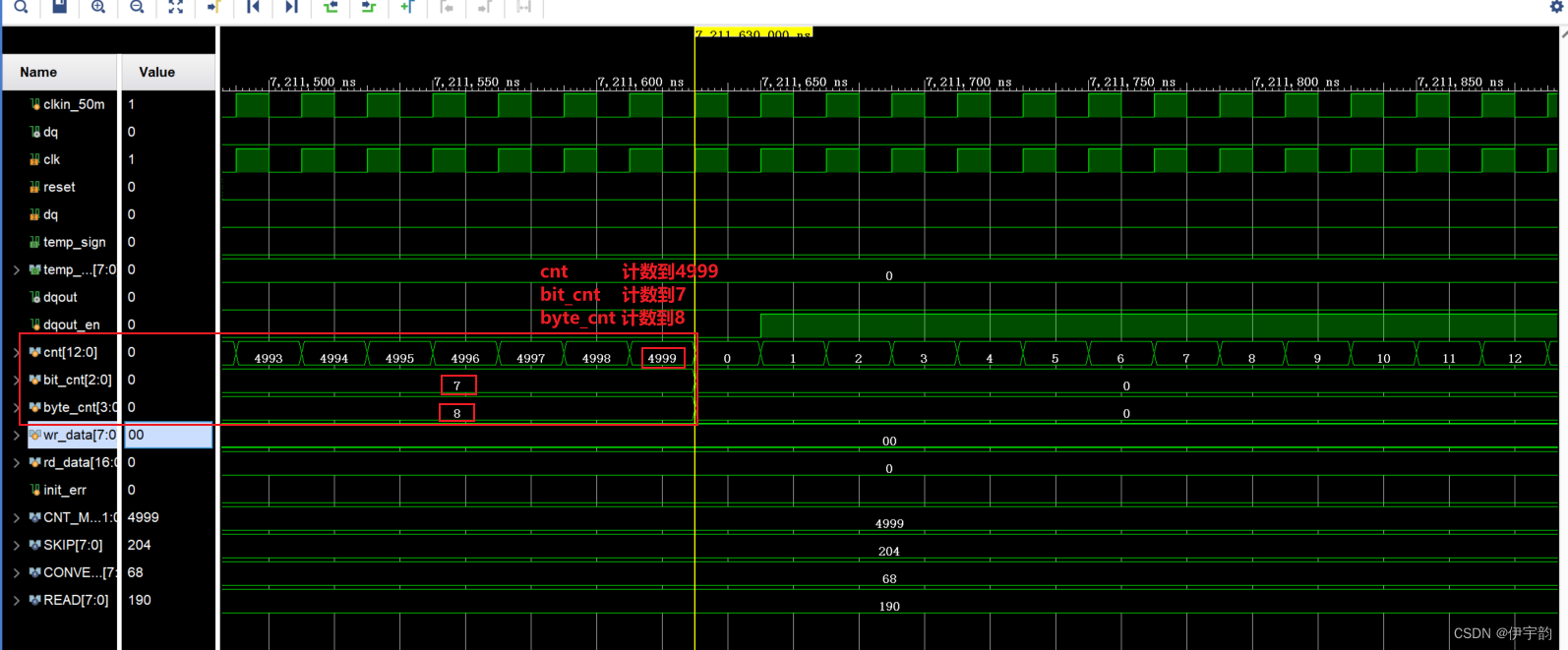

one wire(单总线)FPGA代码篇

一.引言 单总线(OneWire)是一种串行通信协议,它允许多个设备通过一个单一的数据线进行通信。这个协议通常用于低速、短距离的数字通信,特别适用于嵌入式系统和传感器网络。 二.one wire通信优点缺点 优点: 单一数据线: 单总线仅需要一根数据线,这极大地简化了硬件连接。设备可以在同一总线上连接,并且通过地址来区分彼此。低成本: 单总线协议不需要复杂的硬件,

Go 项目必备:深入浅出 Wire 依赖注入工具

当项目中实例依赖(组件)的数量越来越多,如果还是人工手动编写初始化代码和维护组件之间依赖关系的话,会是一件非常繁琐的事情,而且在大仓中尤其明显。因此,社区里已经有了不少的依赖注入框架。 除了来自 Google 的 Wire 以外,还有 Dig(Uber) 、Inject(Facebook)。其中 Dig 和 Inject 都是基于 Golang 的 Reflection 来实现的。这不仅对性能产

Verilog 之 wire与reg 类型的变量

文章目录 `reg` 类型`wire` 类型总结默认情况下的input ,output 变量 在 Verilog 中,reg 和 wire 是用来声明变量或信号的关键字,它们有不同的特征和用途。 reg 类型 reg 类型用于表示寄存器变量。在 Verilog 中,reg 用于存储状态或时序逻辑,通常在 always 块或时钟触发的过程中使用。它可以存储值并在时钟信号触

![[HDLBits] Simple wire](/front/images/it_default2.jpg)