本文主要是介绍基于FPGA的真随机数发生器高效熵提取,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一. 综述

真随机数发生器(TRNG)是硬件加密的重要组成部分,它与伪随机数生成器(PRNG)不同,是利用抖动等不可控因素作为随机数的熵源,所生成的随机数具有真正的随机性。本文讲述一种新颖的熵提取方法,用来提高基于抖动的真随机数发生器在FPGA上的吞吐量。 即通过利用超高速的进位逻辑基元,提高熵提取的效率,从而提高吞吐量。 下面以Spartan-6 FPGA上基于环形振荡器的真正随机数发生器为例说明设计步骤和技术。 这种设计方法同在FPGA上基于抖动的高效TRNG相比,所需要的熵提取累积时间缩短了3个数量级,而且仅仅用了67个slice就实现了14.3 Mbps的吞吐量,并且这项研究提供了对安全性的正式评估。

二. 介绍

早期FPGA的TRNG实现不提供熵模型。 早期研究出的发生器通过使用诸如NIST 和DIEHARD 等统计测试进行验证,但他们缺乏对安全性的正式评估。 在FPGA上仅有少数TRNG设计提供数学模型和熵估计。而我们的新方法从累积的定时抖动中提取高效的熵。不是通过以高能量或面积为代价增加转换数量来提高吞吐量,而是专注于改善单次转换的熵提取。我们的主要想法是基于TRNG吞吐量与采样信号的定时分辨率的平方成比例增加的事实。由于这个原因,即使定时分辨率的适度改进也会导致积累时间和比例吞吐量增益的大幅降低。

在Xilinx FPGA上,两种类型的slices包含一个进位链(carrychain)基元,可用于生成分支,加法器或乘法器。 该基元由连接到触发器的四个延迟级组成,并可配置为抽头延迟线。 可以通过专用路径连接来自同一列上的相邻slice的进位链,以形成更大的延迟线。 这种配置可用于采样时间精度较高的信号,并已用于实现高分辨率时间数字转换器。通过利用进位链进行熵提取,我们的TRNG实现了更小的占位面积, 更大的吞吐量。 并且提供了此TRNG的安全评估。

三. TRNG的实现方案

TRNG评估的早期方法包括收集随机数据并运行一系列统计测试,如NIST和DIEHARD测试。这种黑盒子方法的一个主要缺陷是所有PRNG即使产生完全确定性输出也可以轻松通过统计测试。即使用TRNG设计人员验证自己的设计,这种方法也是有问题的。例如,设计师可能认为,随机性是由热抖动引起的,而实际上它来自不稳定的电源。在这种情况下,如果TRNG与稳压器一起使用,它可能会产生非常弱的抖动。虽然统计测试可用于初始分析或健全性检查,但它们不能代替正式的安全评估。 TRNG的正式安全评估需要TRNG的数学模型和熵评估。 AIS-31为TRNG的设计和评估提供了一个框架。 AIS-31认证的要求之一是熵源的随机模型和生成熵的下边界的估计。

随机模型用于描述随时间演变的概率系统。 它比物理模型(如晶体管模型)更简单,因为它只考虑影响随机性的过程。 这种类型的模型用于描述在电路中产生熵的过程,例如抖动累积或从亚稳状态解析的过程。图1显示了TRNG的框图。 随机模型必须基于明确陈述和实验可验证的假设。 该模型的目标是为平台参数(例如LUT延迟或噪声参数)和设计参数(例如环形振荡器的数量或采样频率)的不同值提供熵估计。 所获得的随机模型基于输入参数(平台和设计参数)来计算最小熵。设计流程的下一个阶段是通过实验获取平台参数。 之后,需要确定最佳设计参数。 这可以通过使用随机模型和平台参数的测量值来计算设计参数的不同值的熵来完成。 然后可以调整设计参数直到达到指定的熵界限。 统计分析在评估的最后阶段完成。

四.实验架构

我们的架构基于高精度采样不稳定信号的概念,从而比标准方法提取更多的熵。 这种方法非常有效,因为吞吐量方面的增益与精度的改进平方成正比。 在这个架构中,熵源和熵提取器作为为独立的块来实现。 系统中的所有随机性由信号边缘的时间不确定性产生。 振荡器信号首先通过抽头延迟线传播,取样并根据捕获的数据片段确定信号边缘的位置。 数字化数据被传播到熵提取器,然后在输出端产生一个随机位。

熵源和数字化模块如图2所示。熵源实现为一个自由运行的n级振荡器,使用一个NAND门和多个缓冲器。 数字化模块由连接到每个延迟元件输出的快速抽头延迟线组成。 这些延迟线正在执行噪声信号的时间 - 数字转换。

图3显示了单抽头延迟线的内部结构。 该行由m个快速缓冲器和一组连接到其输出的触发器组成。 转换的时序分辨率等于分接延迟线单级的延迟。 在时钟上升沿之后,每个缓冲器的输出数据在触发器中被捕获。 这些数据反映了振荡器的内部状态。为了捕捉振荡器的完整状态,必须选择作为抽头延迟线的大小的参数m,抽头延迟线必须被选择为使得抽头线的延迟大于熵源中最慢元素的延迟。 否则,信号边沿可以通过任何线路检测不到。 这也是为了提供鲁棒性,因为振荡器元件的延迟以及转换的时间步长可能因温度或电压变化而变化,并且在最坏情况下必须检测到信号边缘。 由于采样期间的时序违规,一些触发器可能会被驱动到亚稳状态,从而可能产生“气泡”码。

延迟线的预期输出是连续运行'1',然后运行'0'或运行'0'由运行'1'休止。 在大多数情况下,如图4(a)所示,信号沿只会在一个延迟线中捕获。 熵提取器用于解码此边的位置,它必须能够处理两种效果:代码中的多边和边界。 由于单个抽头线的延迟大于振荡器元件的延迟,因此会出现多个边缘。 如果信号边缘看起来靠近延迟线的末端,则信号可以通过下一个振荡器元件传播,这导致在下一行的开始处出现第二个边缘。 熵提取器总是解码第一个边缘而忽略第二个边缘,见图4(b)。 代码中的“气泡”(图4(c))使用优先级解码器进行过滤。

熵提取器的体系结构如图5所示。抽头延迟线(由Ci,j表示,其中i是行数,j是一行中的位数)分为两个阶段进行处理。 首先,所有行均按位进行着色,产生一个m位向量。 该矢量被馈送到边缘检测器,该边缘检测器输出优先级编码器的LSB,使得奇数位置被编码为'0',甚至位置被编码为'1'。

所提出的架构的设计参数是:n环形振荡器的级数,m - 快速延迟线中的级数和tA-抖动累积时间。

五. 随机模型

在本节中,我们提供对拟议设计的正式安全评估。 我们从关于FPGA平台的假设开始,为二元概率计算开发一个简单的随机模型。 主要目标是提供每比特熵的下限,以及确定最佳设计参数,如阶段数和抖动累积时间。

5.1 假设

我们通过以下假设开始初始安全分析:

• 每个LUT的延迟由一个确定性分量d0,LUT和一个随机分量Δd组成。随机分量受局部热噪声的影响。这个随机分量可以用正态分布N(0,σLUT2)来模拟,其中σLUT是标准偏差。

• 除白噪声之外的噪声源可能会对可变分量产生影响。这些包括闪烁噪声,由电源变化引起的全局噪声和攻击者的操纵影响(例如通过EM辐射)。这些噪音在我们的模型中没有量化,因此我们将始终假设最差情况值。

• 抖动实现的白噪声分量是相互独立的。

• 通过快速延迟线传播的噪声信号使用等距bin tstep进行采样。

前三个假设是众所周知的并且通过实验验证。最后一个需要针对特定的实现平台进行实验性调查。

5.2二进制概率计算

TRNG按以下方式运行。 振荡器运行时间tA,之后采样信号被激活。 在此期间,来自每个延迟元件输出的信号通过快速延迟线传播。 由于振荡器是自由运行的,所以抖动随时间积累。 只要延迟线足够长(m·tstep> d0,LUT),就可以保证在延迟线中至少捕获一个噪声信号边缘。 图6显示了熵提取模型。 描述采样边缘和噪声信号之间的相对热抖动使用高斯分布。 由于抖动实现是独立的,在时间tA之后积累的热抖动的标准偏差与转换事件的数量的平方根成比例:

噪声信号以精确的tstep采样并且TDC的邻近状态使用不同的比特进行编码。 1和0的概率等于曲线下的面积。

这些概率取决于采样边缘和噪声信号边缘的最可能位置之间的偏移时间,如图6所示。我们将τ定义为有噪声信号边缘与最接近采样bin中间的间隔,如图所示 在图中:

在不失一般性的情况下,我们可以假设这个bin被解码为1.然后,二元概率由下式给出:

其中Φ是高斯分布的累积概率函数:

5.3熵下界

二进制概率取决于偏移时间τ。 τ的确切值取决于累积时间,序列中样本的数量,还取决于低频噪声和确定性噪声。 由于这些因素不可预测也不可控,所以应该使用最坏情况值来估计熵的下限。 香农熵然后由下式给出:

图7显示了取决于τ的香农熵。 当τ= 0时达到下限。

5.4模型使用

所提出的随机模型可用于根据平台参数和设计参数来估计熵的下限。该模型由一组方程组成,这些方程组可以作为一个Matlab函数实现,该函数根据平台和设计参数产生熵下限。平台参数是实现平台的物理参数,它们应该通过测量来确定。此设计的相关平台参数为:d0,LUT - 单个LUT的平均延迟,带有快速延迟线的tstep-bin以及由单个转换事件生成的热噪声σLUT。

一旦平台参数已知,该模型用于确定不同设计参数值的熵的下限。设计参数为:环形振荡器中的级数,快速延迟线中的m级,fCLK系统时钟频率,tA - 抖动累积时间(也可以表示为NA - 系统时钟周期数)和可选的下采样因子k。下采样可用于通过将k个邻近仓组合成一个仓来提高快速延迟线中的时间 - 数字转换的线性度。随机模型用于确定不同设计参数值的熵值,从而可以探索不同的设计折衷。

因此,TRNG的设计过程由以下四个步骤组成:

步骤1:测量相关的平台参数。

步骤2:基于随机模型和获得的平台参数确定最优设计参数。

第3步:FPGA实现。

步骤4:对生成的比特进行统计评估。

5.5 后处理

生成的位可以使用后处理来改进。 后处理是一种压缩技术,以降低吞吐量为代价提高了每比特熵。 Xor后处理是一个简单的方法,具有紧凑的硬件实现。 它由连续产生的位组成,从而将吞吐量降低np倍。 提出的随机模型可以用来估计生成数的最大偏差,定义为:

使用压缩率np的后处理序列的偏差为:

然后可以计算新的熵值。

六.实施

使用Xilinx Spartan-6 FPGA实现。熵源和数字转换器的实现方法如图8所示。环形振荡器的阶段使用LUT实现,快速延迟线使用进位链基元实现。 在Spartan-6上,一半的片包含这些进位原语。 这些切片位于偶数列中。 通过连接来自相同列中相邻切片的进位基元来形成长进位链。 振荡器的延迟级放置在快速延迟线正下方的切片中。 这些是我们在实现中使用的唯一布局约束。 设计的其余部分是自动合成和实现的。

6.1平台参数

感兴趣的平台参数是LUT延迟d0,LUT,热抖动的标准偏差σG,LUT和TDC转换的时间步长tstep,即进位链中单个元件的延迟。

LUT延迟是通过实现一个环形振荡器并在固定时间内计算转换次数来确定的。发现d0,LUT = 480ps。

抽头行延迟步骤通过捕获长进位链中的振荡器输出并计数时钟周期的级数来确定。结果大约是tstep = 17ps。

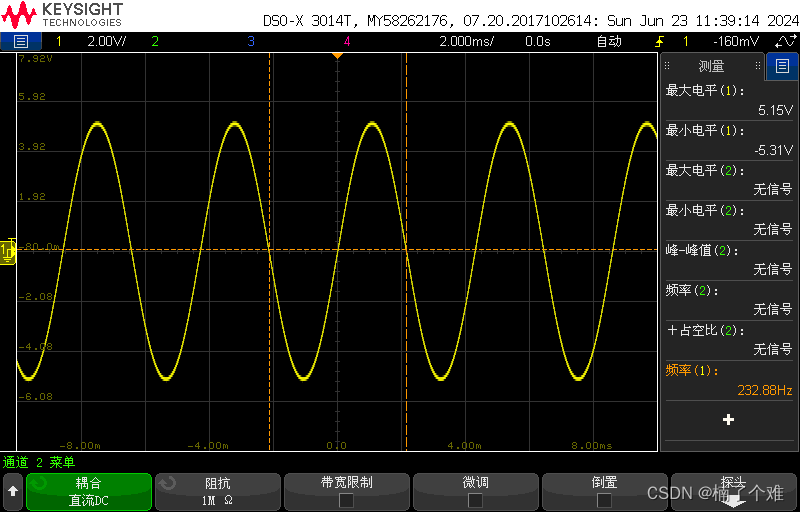

热抖动测量必须非常小心地执行,因为此参数非常重要。从历史上看,有很多论文高估了这个参数,为了获得准确的结果还有几个挑战需要克服。进行测量的最可靠的方法是,因为可以在引脚,封装和示波器上过滤出热噪声。根据文献[4]给出的电路模型,测量时间需要很短(1μs或更短),否则低频噪声占主导地位。测量必须有差别地进行,以便考虑全球噪声源,例如电源的不稳定性。我们提出了一种简单的方法来确定使用进位链逻辑的FPGA上的抖动。两个相同的环 -

振荡器被实现并放置得彼此靠近。振荡器启用20ns,并使用基于carry4原语的快速抽头延迟线捕获输出。捕获的数据然后发送到PC进行分析。通过观察两个振荡器的信号边沿之间的差异来确定累积抖动。抖动的标准偏差从1000个测量结果中估算出来。得到的结果表明σG,LUT≈2ps。

6.2 设计参数

环形振荡器的级数n不在熵模型中。为了实现最紧凑的实现,应该选择此参数的值尽可能小。我们选择n = 3的值,因为这是最短的环形振荡器,我们可以可靠地测量频率和抖动参数。

快速延迟线m的级数必须选择为始终检测到信号边沿,这种情况发生在m> d0,LUT / tstep。对于我们的平台参数,这个条件变成m> 29。由于每个carry4原语有4个元素,m必须是4的倍数。最初,我们尝试使用8个进位原语(m = 32),但测量结果表明信号边缘是没有在0.8%的案例中被捕获。这可能是由于d0是平均延迟值,而一些LUT可能较慢。为了提供更好的鲁棒性,我们决定使用9个carry4阶段(m = 36),测量结果表明边缘总是被捕获。没有进一步增加米的好处。

要克服的挑战之一是进位链的非线性,即不同的仓具有不同的宽度。在[6]中进行的一项研究表明,这种非线性的主要原因是不平衡的时钟树。同样的文章还建议通过使用跨越一个时钟区域的进位链来提高线性度。在Spartan-6上,时钟区跨越16行。由于我们的设计仅使用9个carry4阶段,因此可以设置放置约束以确保所有9个阶段都处于同一时钟区域。时间 - 数字转换的非线性的另一个原因是carry4原语的内部结构以及过程变化的影响。这可以通过使用k = 4的下采样来改善,这导致了更宽的分箱和更高的tA要求。为了探索设计空间,我们实现了多种版本的TRNG,使用k = 1和k = 4。积累时间tA必须是10ns的倍数,因为平台时钟频率是100MHz。我们针对两种版本的TRNG探索不同tA值的设计空间。

6.对比

使用随机模型和获得的平台参数,我们将熵提取方法与基本TRNG在同一平台上使用的方法进行比较。 基本TRNG由一个由系统锁定采样的自由振荡器组成。 抖动累积过程与我们的模型中所描述的完全相同,但是熵提取是不同的,因为有噪声的信号是在定时 - 等于环形振荡器的半周期的情况下采样的。 在最好的情况下,环形振荡器仅使用一个LUT来实现,这会导致tstep,RO = d0,LUT。

由于吞吐量与采样精度的平方成比例地进行缩放,因此我们在k = 1时获得的吞吐量改进是:

这几乎是3个数量级。

对于k = 4,改进因子是49.8。

七. 结果

我们在Xilinx Spartan-6 FPGA上实现了两种版本的TRNG。两个版本的参数值都是n = 3和m = 36。一个版本使用down-sampling(k = 4),另一个版本不使用down-sampling(k = 1)。对于k = 1的TRNG占据包括熵源和熵提取器的67个slices。 TRNG版本k = 4更小,因为它只占用40个slices。

表1显示了不同设计参数的统计评估和吞吐量结果。生成的数据使用异或后处理进行压缩,nNIST是通过所有统计测试所需的最小压缩率。根据模型计算压缩前后的每比特熵(HRAW和HNEW)。压缩后的吞吐量报告在最后一列。

表2总结了与相关工作的比较。除[1]外,我们的设计实现了比所有TRNG更高的吞吐量。然而,[1]中的TRNG仅使用了511个LUT用于熵源,在Xilinx平台上最多为128个slice(本文中未报告确切的利用率结果)。我们的熵源是一个环形振荡器,它只消耗3个slices,完整的设计消耗40个slices。

在这项工作中,我们提出了一种用于FPGA上高吞吐量,真随机数发生器的新型熵提取技术。 这种技术依靠进位逻辑原语对累积抖动进行有效采样。 该技术以Xilinx Spartan-6 FPGA上实现的高吞吐量TRNG为例进行说明。 显示了所有设计和评估步骤,包括平台参数测量,探索设计空间和运行统计评估。 最快的TRNG实施占用67个slices,达到14.3Mb / s的吞吐量。 最紧凑的实现消耗40个slices并实现1.53Mb / s的吞吐量。未来的工作将侧重于在不同的实现平台上应用所提出的方法,并开发嵌入式测试以进行实时评估。

这篇关于基于FPGA的真随机数发生器高效熵提取的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[FPGA][基础模块]跨时钟域传播脉冲信号](/front/images/it_default.gif)