本文主要是介绍DDS信号的发生器(验证篇)——FPGA学习笔记8,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

前言:第一部分详细讲解DDS核心框图,还请读者深入阅读第一部分,以便理解DDS核心思想

三刷小梅哥视频总结!

小梅哥![]() https://www.corecourse.com/lander

https://www.corecourse.com/lander

一、DDS简介

DDS(Direct Digital Synthesizer)即数字合成器,是一种新型的频率合成技术,具有低成本、低功耗、高分辨率、频率转换时间短、相位连续性好等优点,对数字信号处理及其硬件实现有着很重要的作用。 DDS的基本结构主要由相位累加器、相位调制器、波形数据表 ROM、 D/A 转换器等四大结构组成,其中较多设计还会在数模转换器之后增加一个低通滤波器(LPF)。 DDS 基本结构图如下图所示。

由上图可以看出, DDS 主要由相位累加器、相位调制器、波形数据表以及 D/A 转换器构成。其中相位累加器由 N 位加法器与 N 位寄存器构成。每来一个时钟,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟的作用下,不断对频率控制字进行线性相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。当相位累加器累加满量时就会产生一次溢出,完成一个周期的动作。相位累加器输出的数据就是合成信号的相位。相位累加器的溢出频率,就是 DDS 输出的信号频率。

通过改变相位控制字 P_WORD 可以控制输出信号的相位参数。令相位加法器的字长为 M,当相位控制字由 0 跃变为 P_WORD 时,波形存储器(ROM)的输入为相位累加器的输出与相位控制字 P_WORD 之和,因而其输出的幅度编码相位会增加 P_WORD/2M,从而使输出的信号产生相移。

用相位调制器输出的数据,作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完后相位到幅度的转换。 N 位的寻址 ROM 相当于把 0° -360°的正弦信号离散成具有 2N个样值的序列。若波形存储器中有 D 位数据位,则 2N 个样值的幅值以 D 位二进制数值固化在波形存储器当中。按照地址的不同可以输出相应相位的正弦信号幅值。相位—幅度变换原理图如下图所示:

数模转换器(D/A)的作用是把合成的正弦波数字量转化为模拟量。正弦幅度量化序列经数模转换器转换后变成了包络为正弦波的阶梯波。频率合成器对数模转换器的分辨率有一定的要求,其分辨率越高,合成的正弦波台阶数就越多,输出的波形精度也就越高。 DDS 信号流程图如下图所示:

这里相位累加器位数为 N 位( N 的取值范围实际应用中一般为 24~32),相当于把正弦信号在相位上的精度定义为 N 位,所以其分辨率为。

若 DDS 的时钟频率为Fclk,频率控制字 fword 为 1,则输出频率为 ,这个频率相当于“基频”。若 fword 为 B,则输出频率为

。

因此理论上由以上三个参数就可以得出任意的输出频率。且可得出频率分辨率由时钟频率和累加器的位数决定的结论。当参考时钟频率越高,累加器位数越高,输出频率分辨率就越高。

从上式分析可得,当系统输入时钟频率Fclk不变时,输出信号频率由频率控制字 B 所决定,由上式可得: 。 其中 B 为频率字且只能取整数。为了合理控制 ROM 的容量,此处选取 ROM 查询的地址时,可以采用截断式,即只取 32 位累加器的高 M 位。这里相位寄存器输出的位数一般取 10~16 位。

频率控制字理解:

此变量A可以控制取点速度,实际就是对应框图中的频率控制字fword。time_r截取寄存器高11位与ROMd11位地址线对接,time_r低位做累加控制高位变化速率实现频率调控。

此为DDS核心所在!!

此部分正是框图中的相位累加器!!!!

相位控制字理解:

实际为控制相位初始值,说白了就是改变读取ROM数据表的起始位置!B不会改变读取频率,但可以改变初始位置,变量B就是相位控制字!!!!

二、公式讲解

![]()

若 DDS 的时钟频率为Fclk,N及对应time寄存器位宽,此处A为频率控制字,Fout为最终输出的信号频率。由此即可实现根据输出频率计算对应频率控制字的目的。

计算举例:输出一个完整波形需要的时间:2048(11位RAM寄存器)*10ns(100MHz晶振) = 20480ns = 0.00002048s 对应频率为48828.125Hz

公式计算:A为22‘h10_0000(计算选取相位累加器高11位,[31:21],A取低11位[21:0],目的是为了每次增加可以改变寄存器第21位数值!)计算的频率为48828.125Hz

三、代码设计

1、验证部分顶层

`timescale 1ns / 1ps

module DDS_top(input sys_clk,//100Mhzinput sys_rst_n,// input [31:0] Fword,// input [10:0] Pword,output [9 :0] da_data);wire [10:0] rom_addr;

wire clk_100mhz;

assign da_clk = clk_100mhz;parameter Fword = 32'd10000;

parameter Pword = 11'b0;DDS_FP u_DDS_FP(.sys_clk (sys_clk) ,

.reset_n (sys_rst_n) ,

.Fword (Fword) ,

.Pword (Pword) ,.rom_addr (rom_addr)

);ROM_10x2048sin u_ROM_10x2048sin (.clka(sys_clk), // input wire clka.addra(rom_addr), // input wire [10 : 0] addra.douta(da_data) // output wire [9 : 0] douta);endmodule

顶层给出固定的频率控制字,和相位控制字,下面进行理论计算:

2、验证部分DDS逻辑层

`timescale 1ns / 1psmodule DDS_FP(input sys_clk,input reset_n,input [31:0] Fword,input [10:0] Pword,output [10:0] rom_addr);

reg [31:0] r_Fword;

reg [10:0] r_Pword;reg [31:0] Fcnt;always @(posedge sys_clk ) beginr_Fword <= Fword;r_Pword <= Pword;

endalways @(posedge sys_clk or negedge reset_n) beginif(!reset_n)beginFcnt <= 32'd0;endelse beginFcnt <= Fcnt + r_Fword;end

endassign rom_addr = Fcnt[31:21] + r_Pword;endmodule

3、仿真部分代码

`timescale 1ns / 1ps

module DDS_tb;reg sys_clk ;reg sys_rst_n ;// reg [31:0] Fword ;// reg [10:0] Pword ;wire [9 :0] da_data ;DDS_top u_DDS_top(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

// .Fword (),

// .Pword (),

.da_data (da_data)

);initial beginsys_clk = 1;

endalways #5 sys_clk = !sys_clk;initial beginsys_rst_n = 0;#200sys_rst_n = 1;

endendmodule四、测试分析

1、仿真测试结果

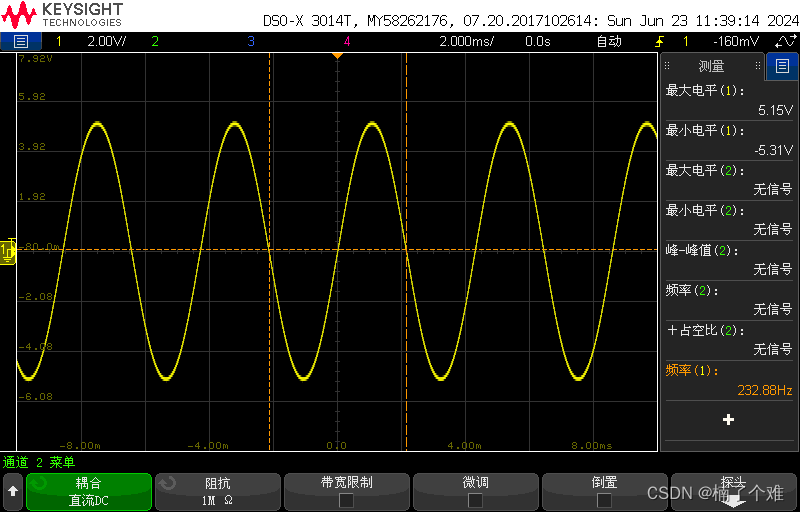

2、上板验证

测试频率与实际计算频率相差不大,验证成功,

五、未来改进

可以使用外部按键控制,想要的频率,通过给出的计算公式计算对应的频率控制字,控制最终输出波形的频率,亦可多次例化ROM IP,添加其他不同波形。

这篇关于DDS信号的发生器(验证篇)——FPGA学习笔记8的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!