本文主要是介绍Cadence Allegro PCB设计88问解析(三十四) 之 Allegro 中 DDR等长处理,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一个学习信号完整性仿真的layout工程师

在进行PCB设计时 ,会遇到一些单端的信号要做等长处理,比如DDR的数据线,交换机之间的数据线之类的。这时需要我们建立match group,来做等长。下面简单介绍在Allegro中怎么做等长:

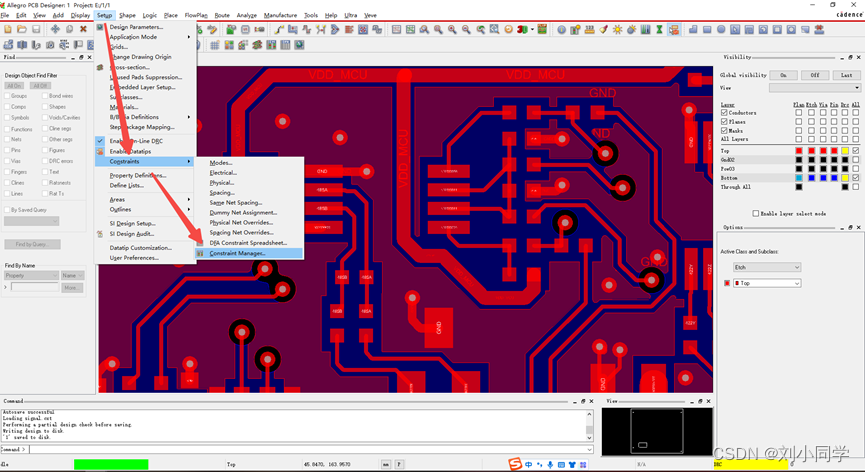

1. 在Allegro的菜单下选择setup命令,点击constraints,选择Constraint Manager,如下图所示:

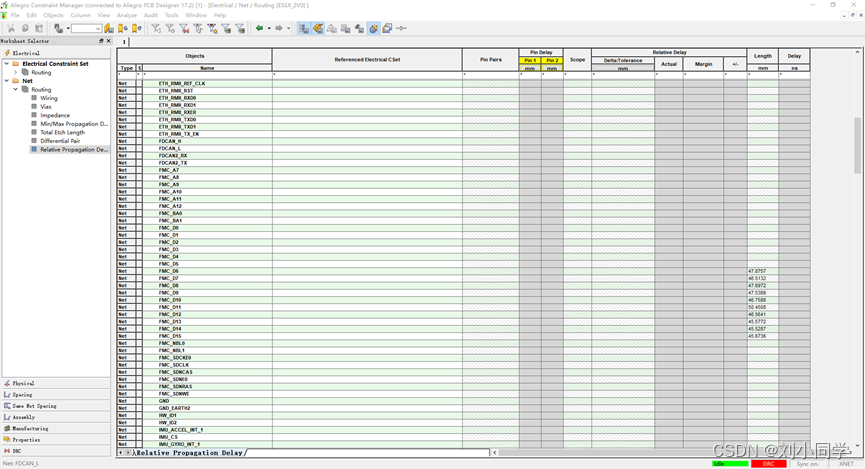

就会弹出如下对话框,如下图所示:

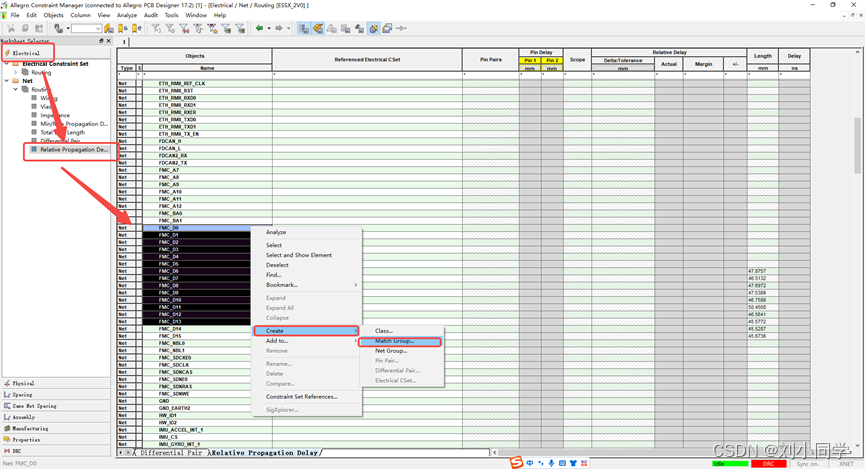

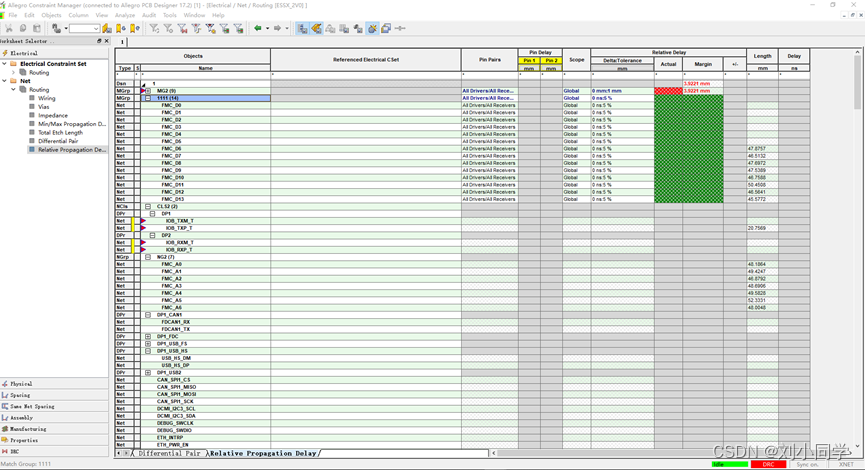

2.先选择电气属性,然后点击Net,选择下面的Relative Propagation Delay,然后框选需要做等长的网络,如下图所示:

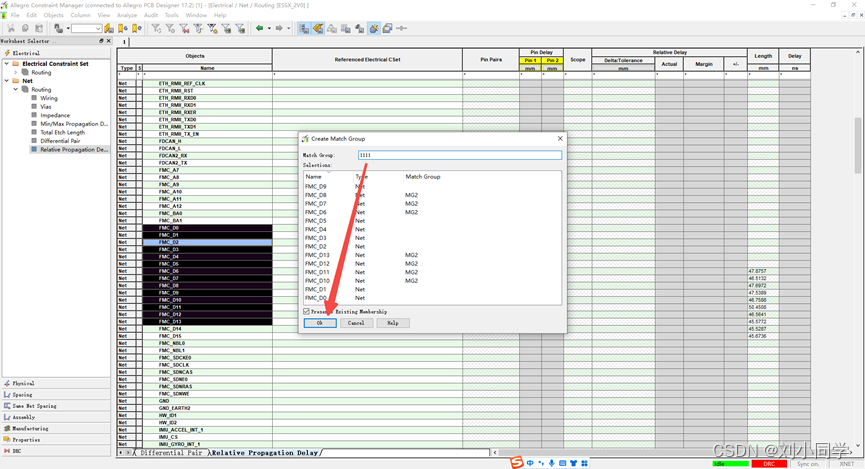

然后弹出如下对话框,给match 命名,然后点击OK,如下图所示:

如下是我们创建好的Match Group:

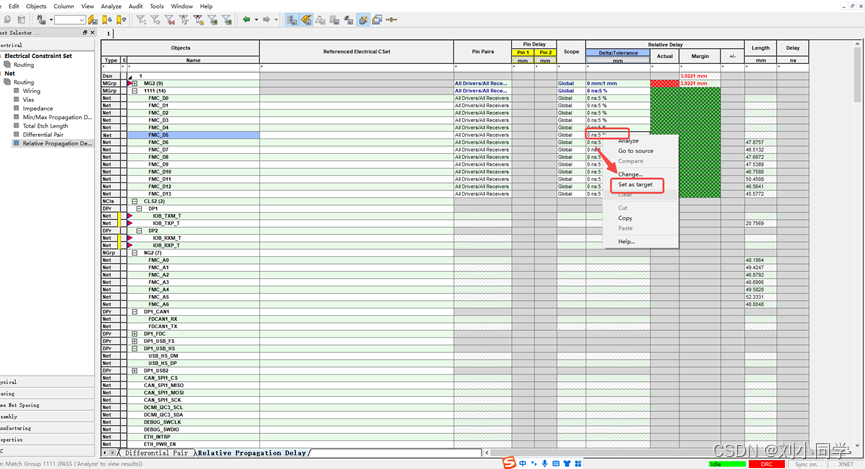

3.设置好组之后,根据自己的设计,选择一根比较合适的网络,设置为target,如下图所示:

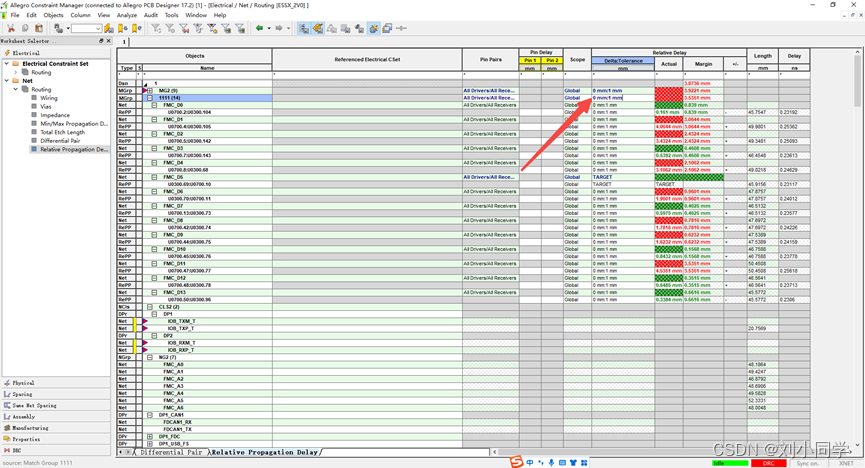

4.在设置好目标走线之后,然后需要设置余量,如下图所示。在组后面设置已目标走线为基础的正负1mm,如下图所示:

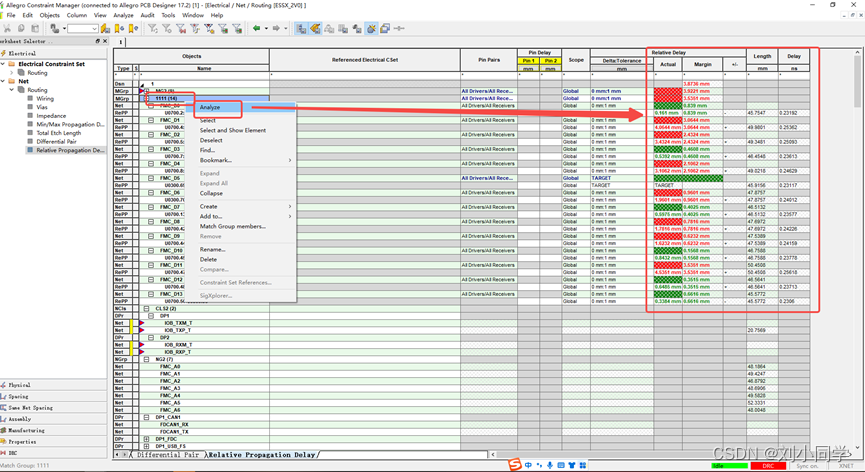

5.以上完成之后,需要做等长处理,点击match右键,点击analye,可以看到后面的走线长度更新,这时就可以做等长:

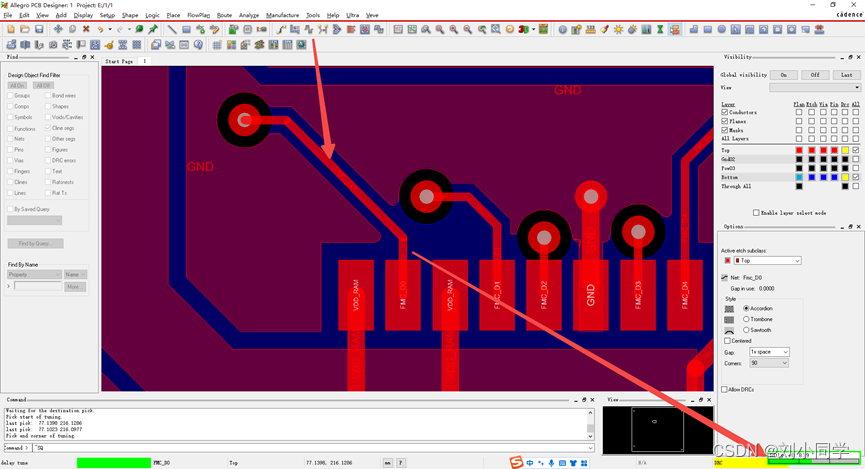

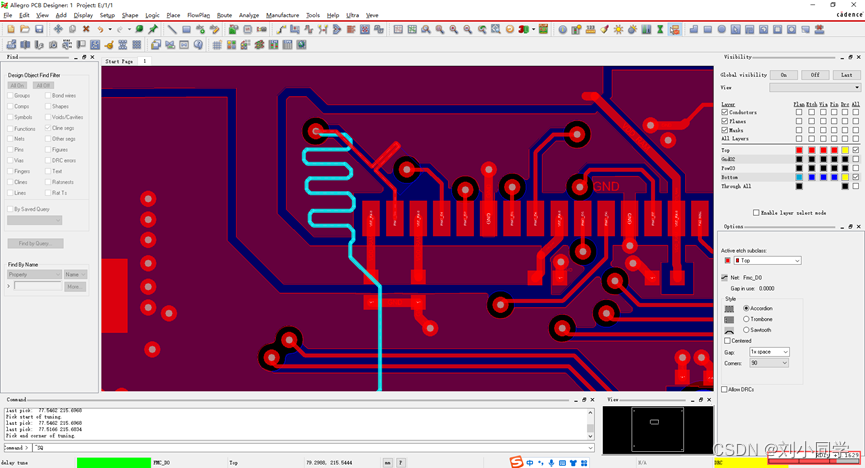

在设计界面中选择Delay tune,然后选择走线,就会弹出下面的绿色示意图,如下图所示:

绿色表示等长满足自己的设置余量,如果显示红色,那就不满足,需要做等长处理:

****上一篇文章:Cadence Allegro PCB设计88问解析(三十三) 之 Allegro 中 Quick Reports的使用的链接如下,大家可以点击查看哟 , 链接: link

以上资料主要是本人在PCB设计中和网络搜索整理而成

如有雷同或错误,希望各位大神留言指正,感谢!!!**

这篇关于Cadence Allegro PCB设计88问解析(三十四) 之 Allegro 中 DDR等长处理的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!