本文主要是介绍保护模式 x86 PDE-PTE中的PWT_PCD位,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

PDE-PTE中的PWT_PCD位

目录

文章目录

- 目录

- 先了解CPU缓存

- PWT 位 [3]

- PCD 位 [4]

先了解CPU缓存

1>CPU缓存是位于CPU与物理内存之间的临时存储器,他的容量比内存小得多,但是交换速度却比内存要快得多.

2>CPU缓存可以做的很大,有几K,几十K,几百K甚至上M的也有.

CPU缓存与TLB的区别:

TLB :

线性地址<----->物理地址

CPU缓存:

物理地址<------>内容

简单来说,CPU可以通过TLB来快速将线性地址转换成物理地址,而CPU缓存又能较为快速的从物理地址获取内容

缓存的机制这只是简单的介绍,具体内容需要查找intel白皮书:

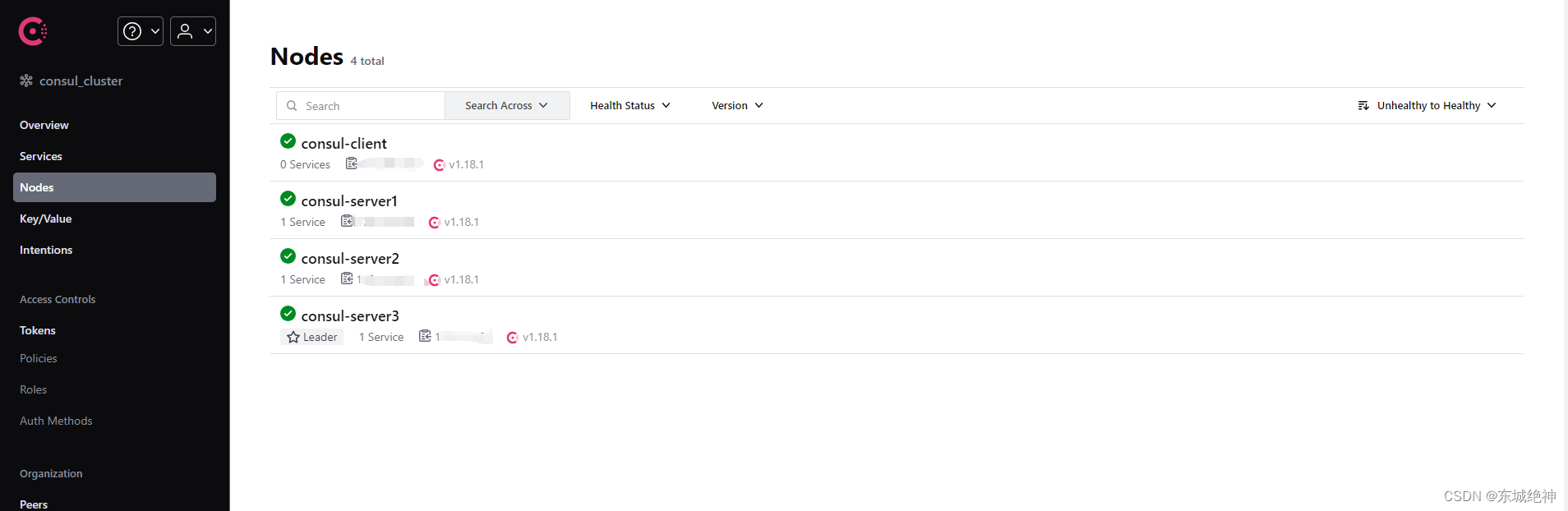

接下来开始说PWT和PCD这两个标志位与CPU缓存的关系,先把PDE,PTE结构再拿出来一遍,怕又是忘记了…

PWT 位 [3]

PWT = Page Write Through

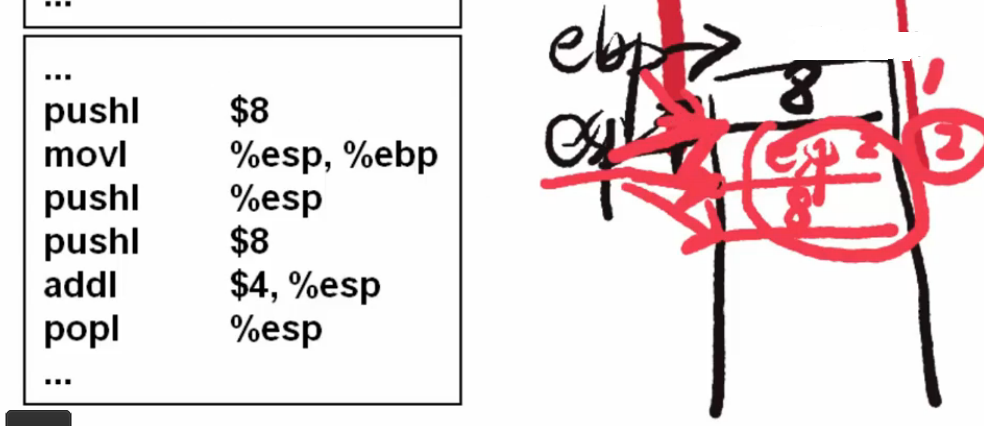

PWT = 1 时,往缓存中写数据时,同时将数据也写入到内存中PWT = 0 时,往缓存中写入数据后,由CPU缓存控制器决定什么时候将缓存写入内存.

PCD 位 [4]

PCD = Page Cache Disable

PCD = 1时,禁止当前页写入缓存,直接写入内存.读写时CPU直接读写内存比如,做页表用的页,已经存储在TLB中,可能不需要再缓存了.所以要求直接写入内存

这篇关于保护模式 x86 PDE-PTE中的PWT_PCD位的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!