本文主要是介绍FPGA的乒乓球游戏机ISE,verilog,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

名称:乒乓球游戏机(代码在文末付费下载)

软件:ISE

语言:Verilog

要求:

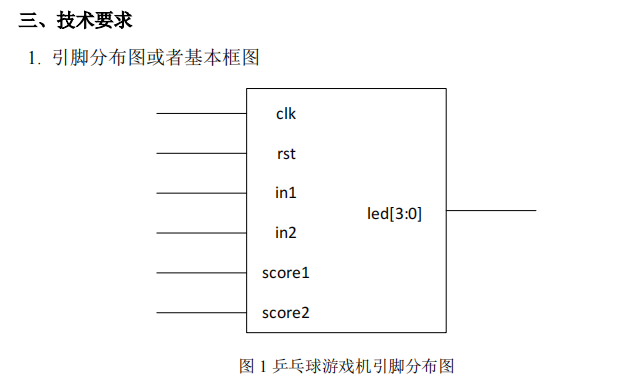

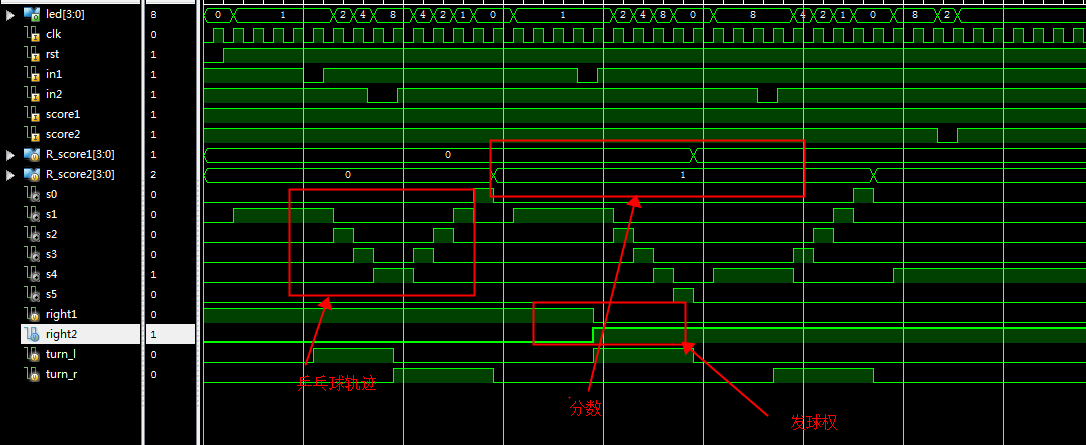

设计一个由两人参赛的乒乓球游戏机,用 4 个 LED 排成一条直线,两边各 代表参赛双方的位置,其中一只点亮的 LED 指示球的当前位置,点亮的 LED 一 次从左到右,或者从右到左,其移动速度应能调节。当“球”将运动到某方的最 后一位时,参赛者应能果断地按下位于自己一方的按钮开关,即表示启动球拍击 球,若击中,则球向相反方向移动;若未击中,球掉出桌外,则对方得一分。双 方各设一个 LED 表示拥有发球权,每隔两次自动交换发球权,拥有发球权的一 方发球才有效。设置计分电路,其中参赛选手各有一个可显示自己当前分数的按 钮,当按下个人分数按钮,可用 LED 灯显示自己分数,当某一方率先达到 11 分 时,所有 LED 灯闪烁,表示比赛结束。

代码下载:乒乓球游戏机ISE,verilog_Verilog/VHDL资源下载

代码网:hdlcode.com

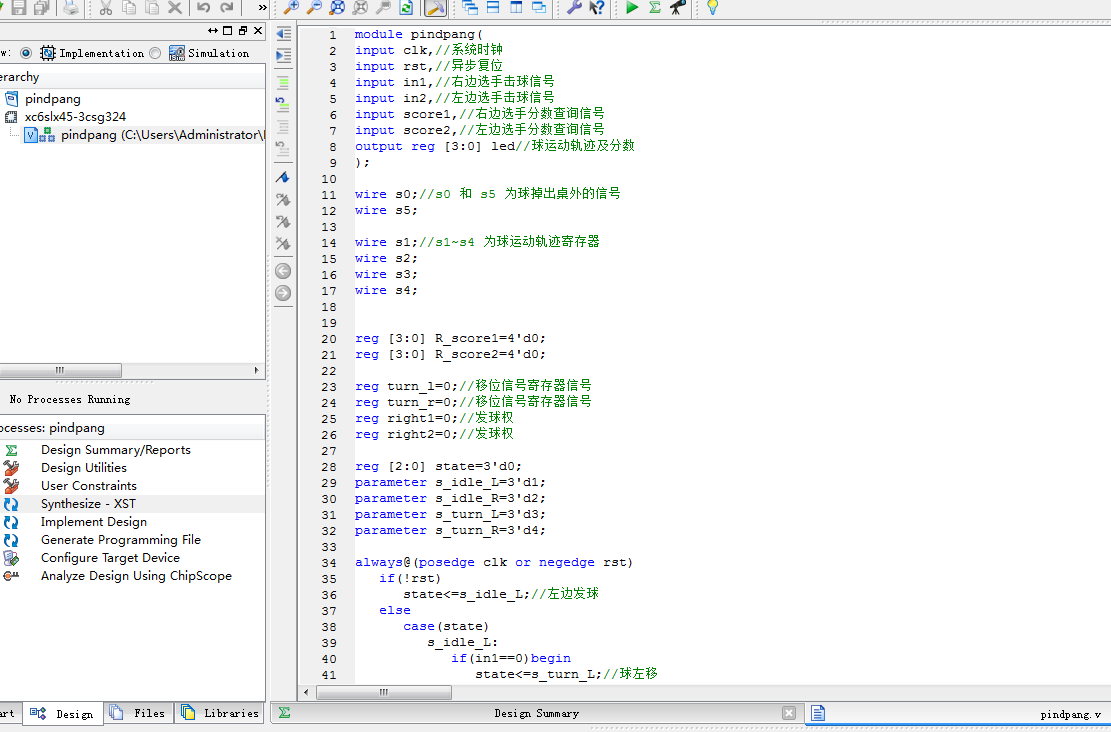

部分代码展示

module pindpang( input clk,//系统时钟 input rst,//异步复位 input in1,//右边选手击球信号 input in2,//左边选手击球信号 input score1,//右边选手分数查询信号 input score2,//左边选手分数查询信号 output reg [3:0] led//球运动轨迹及分数 ); wire s0;//s0 和 s5 为球掉出桌外的信号 wire s5; wire s1;//s1~s4 为球运动轨迹寄存器 wire s2; wire s3; wire s4; reg [3:0] R_score1=4'd0; reg [3:0] R_score2=4'd0; reg turn_l=0;//移位信号寄存器信号 reg turn_r=0;//移位信号寄存器信号 reg right1=0;//发球权 reg right2=0;//发球权 reg [2:0] state=3'd0; parameter s_idle_L=3'd1; parameter s_idle_R=3'd2; parameter s_turn_L=3'd3; parameter s_turn_R=3'd4;

设计文档(文档点击可下载):

1. 工程文件

2. 程序文件

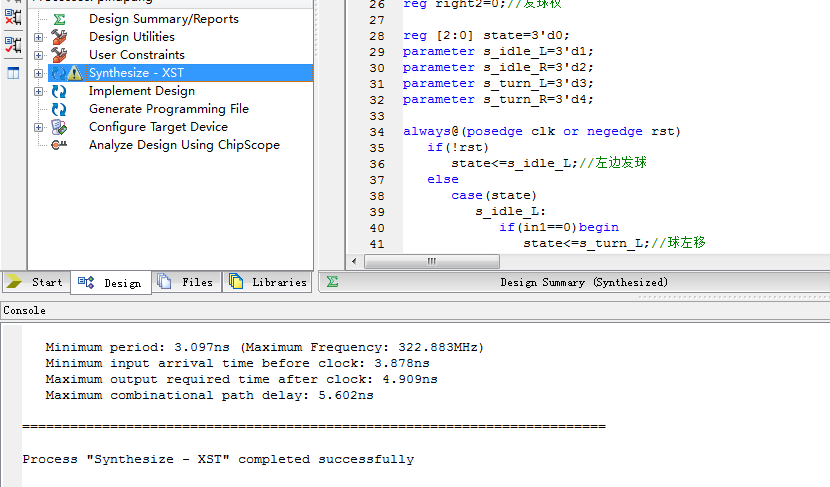

3. 程序编译

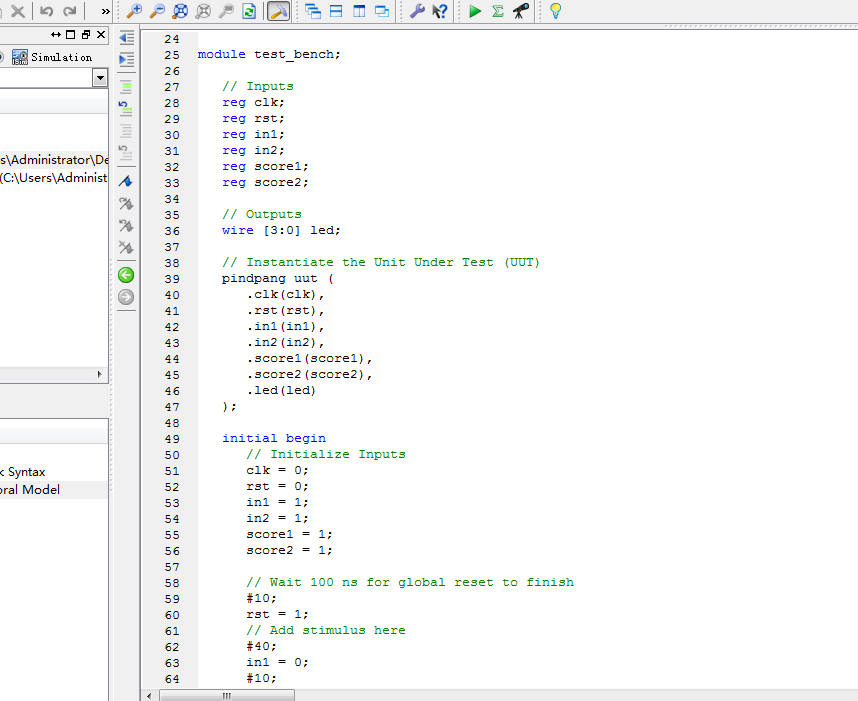

4. Testbench

5. 仿真图

这篇关于FPGA的乒乓球游戏机ISE,verilog的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!