本文主要是介绍FPGA随记——小说 可综合和不可综合,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

当然我在网络上找到了些可综合和不可综合的解释 感觉也很有参考价值:

https://wenda.so.com/q/1378362174074040

综合就是把你写的rtl代码转换成对应的实际电路。

比如你写代码assign a=b&c;

EDA综合工具就会去元件库里拿一个二输入与门出来,然后输入端分别接上b和c,输出端接上a

假如你写了很多这样的语句

assign a=b&c;

assign c=e|f;

assign e=x^y;

……

综合工具就会像搭积木一样的把你这些“逻辑”电路用一些“门”电路来搭起来。当然,工具会对必要的地方做一些优化,比如你写一个电路assing a=b&~b,这样工具就吧a恒接为0了,而不会去给你找一个与门来搭这个电路。

所以,“综合”要做的事情有:编译rtl代码,从库里选择用到的门器件,把这些器件按照“逻辑”搭建成“门”电路。

不可综合,是指找不到对应的“门”器件来实现相应的代码。

由于在正式代码中看到了#8 这种写法,所以单独查看了#能否被综合

关于Verilog 的“#”能够被综合的情况

可以综合的情况:

1、在Verilog中,# 是一个延迟操作符,用于在仿真中指定一个时间延迟。然而,# 操作符是否可以被综合,取决于它用在何处以及如何使用。

可以综合的情况:

时钟边沿延迟:当 # 操作符用于时钟边沿触发的 always 块中,并且与时序逻辑相关时,它可以被综合。例如,在触发器的输出中使用 # 来表示时钟延迟是可综合的。

always @(posedge clk) begin

reg_out <= #1 reg_in; // 可综合,表示一个时钟周期的延迟

end

2、有限的延迟值:如果 # 后面跟的是一个有限的整数值,这通常表示一个固定的延迟,这样的用法在某些综合工具中可能被视为可综合的。

不能被综合的情况:

任意延迟:如果 # 后面跟的不是一个整数值,或者是一个表达式,这通常被视为不可综合的,因为它不能直接映射到硬件。

1、任意延迟:如果 # 后面跟的不是一个整数值,或者是一个表达式,这通常被视为不可综合的,因为它不能直接映射到硬件。

always @(posedge clk) begin

reg_out <= #(some_expression) reg_in; // 通常不可综合

end

2、非时钟边沿:如果 # 操作符用于非时钟边沿触发的 always 块中,它通常被认为是不可综合的。

always @(some_signal) begin

reg_out <= #1 reg_in; // 可能不可综合,取决于上下文

end

3、编译器指令:# 也可以用于编译器指令,如 define 和 ifdef,这些指令在编译阶段就被处理,与综合无关。

还看到了一个inital模块也用在正式代码里面,也没有报错。

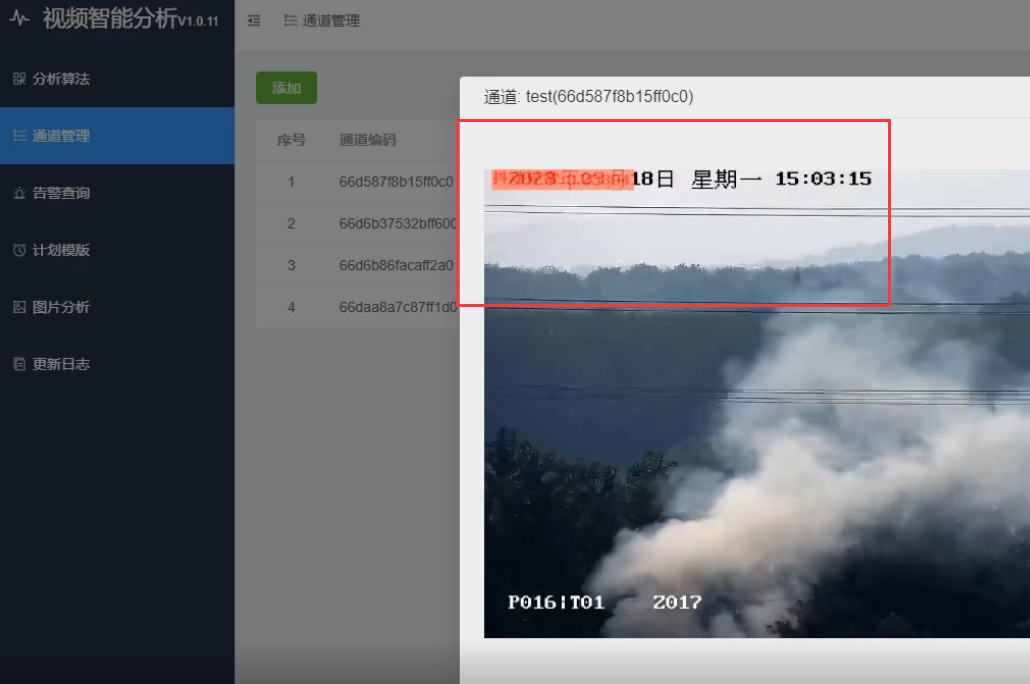

然后综合得到如下电路:

我一直误解为这些不可综合的语句是不能出现在设计里面,只能出现在仿真里面的。我以为如果出现在设计里面了也会被忽略掉。但是我发现 initial 里面的语句实际中确实起了作用,它初始化了counter,我把代码(sof)下载到FPGA开发板进 确实是从0开始计数的。然后我咨询了公司的研发工程师,他是这样解答的:

initial 是不可综合,但是这里只是赋了一个初值(初始化寄存器的值)。没有行为描述。说的不可综合是指的不能生成实际的电路,不是说设计里面写了 initial 会报错 或者被忽略。

这里initial之所以不能综合,是因为它只能执行一次,而always会根据时钟条件无限次触发,所以always里面语句就像硬件电路,来一个时钟,执行一次。而initial就像是初始化程序,最开始把变量初始化,执行一次后不能再执行,直到再次复位。

这里综合的含义是指能生成对应的硬件电路,而这里的initial就像是一个纯软件的初始化。

你提到的有些设计会被忽略是因为综合器认为这个地方是无效的,没有必要的,所以忽略掉,不生成电路,自动优化掉。

这个感觉倒是也符合intial的定义和作用,但是没有行程电路。确实也没办法行程电路,软件还是聪明。

这篇关于FPGA随记——小说 可综合和不可综合的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!