ise专题

Win10 Xilinx ISE License Load 闪退

原因是使用了64位的 License Manager,可以使用 32 位的装载许可证 C:\Xilinx\14.7\ISE_DS\common\bin\nt\xlcm.exe 或者 将启动 ISE 的快捷方式改为启动 32 位

ISE约束文件UCF的基本语法

(一)约束的分类: 利用FPGA进行系统设计常用的约束主要分为3类。 (1)时序约束:主要用于规范设计的时序行为,表达设计者期望满足的时序条件,知道综合和布局布线阶段的优化算法等。 (2)布局布线约束:主要用于指定芯片I/O引脚位置以及指导软件在芯片特定的物理区域进行布局布线。 (3)其它约束:指目标芯片型号、接口位置、电气特性等约束属性。 (二)约束的主要作用 (1)提高

ISE在Win10系统下闪退及impact连接不上下载器解决方法

1. ISE在Win10系统下执行open project时会闪退,解决方法如下,本人在ISE14.4及ISE14.7版本亲测有效 找到程序安装路径下的这两个文件夹 D:\Xilinx\14.7\ISE_DS\ISE\lib\nt64 D:\Xilinx\14.7\ISE_DS\common\lib\nt64 首先在第一个文件夹中,重命名libPortability.dll为libPortabi

从ISE 无法启动modelsim

在ISE14.7 中双击启动modelsim仿真后,出现如下报错: ERROR: Platform mismatch! ERROR: Error(s) encountered while extracting pre-compiled simulation library information. 原因 :当前工程是用32bit ISE14.7版本打开,而modelsim是6

如何编写Xilinx ISE环境下的综合约束文件ucf

FPGA综合工具所用的sdc文件和前端Design compiler和PR所用的sdc的格式完全不一样。不能套用设计前端的sdc约束文件。 ISE 工具的约束文件为*.ucf文件。可采取以下步骤生成: 1)对于管脚分配,根据FPGA验证板的实际情况,手动在ucf文件中做好相应的配置。 2)对于时钟约束。先用synplify 工具跑一下,该工具会自动识别出设计中的时钟。我们在synpl

add ise source 闪退_Win10系统下Xilinx ISE软件出现闪退的解决方法

Win10下安装低版本ISE会出现闪退的情况,例如Version 14.7版本,很多用户遇到这个问题却不会解决,其实方法很简单,下面装机之家分享一下Win10系统下Xilinx ISE软件出现闪退的解决方法,来看看吧。 解决方法: 找到程序安装路径下的这两个文件夹: X:\Xilinx\14.6\ISE_DS\ISE\lib\nt64 X:\Xilinx\14.6\ISE_DS\common\

ISE约束--UCF编辑的入门介绍

http://www.openhw.org/yq000cn/blog/12-07/185475_6dce2.html 摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx FPGA设计约束的分类 Xilinx定义了如下几种约束类型: • “Attributes

vivado XDC / ISE UCF 约束文件

1、CLOCK_DEDICATED_ROUTE(不打算使用板子上的晶振) vivado XDC:set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets XXX] set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {clk_wiz_0/inst/clk_i

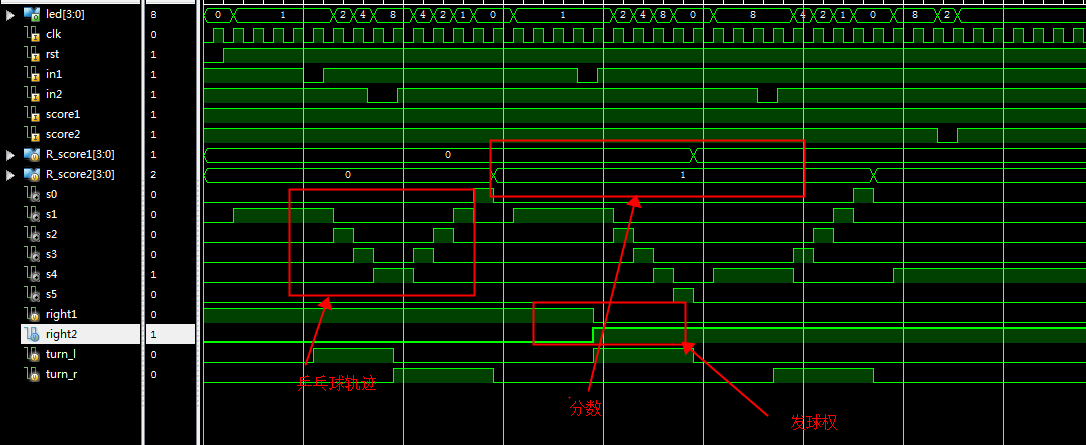

FPGA的乒乓球游戏机ISE,verilog

名称:乒乓球游戏机(代码在文末付费下载) 软件:ISE 语言:Verilog 要求: 设计一个由两人参赛的乒乓球游戏机,用 4 个 LED 排成一条直线,两边各 代表参赛双方的位置,其中一只点亮的 LED 指示球的当前位置,点亮的 LED 一 次从左到右,或者从右到左,其移动速度应能调节。当“球”将运动到某方的最 后一位时,参赛者应能果断地按下位于自己一方的按钮开关,即表示启动球拍击 球,

NAC;ACS;ISE区别

NAC(network admission control)是检查客户端的安全装备的,防止内网的攻击,虽然账户合法了,但是接入设备不一定合法,检查包括:操作系统,杀毒软件,补丁等若干新旧程度,不符合要求的客户端就无法接入网络。 ACS (access controlserver)是检查客户端使用者身份的:是否拥有指定的账号,控制指定账号的访问权限,没有账号的客户端,使用者无法接入网络。 ACS

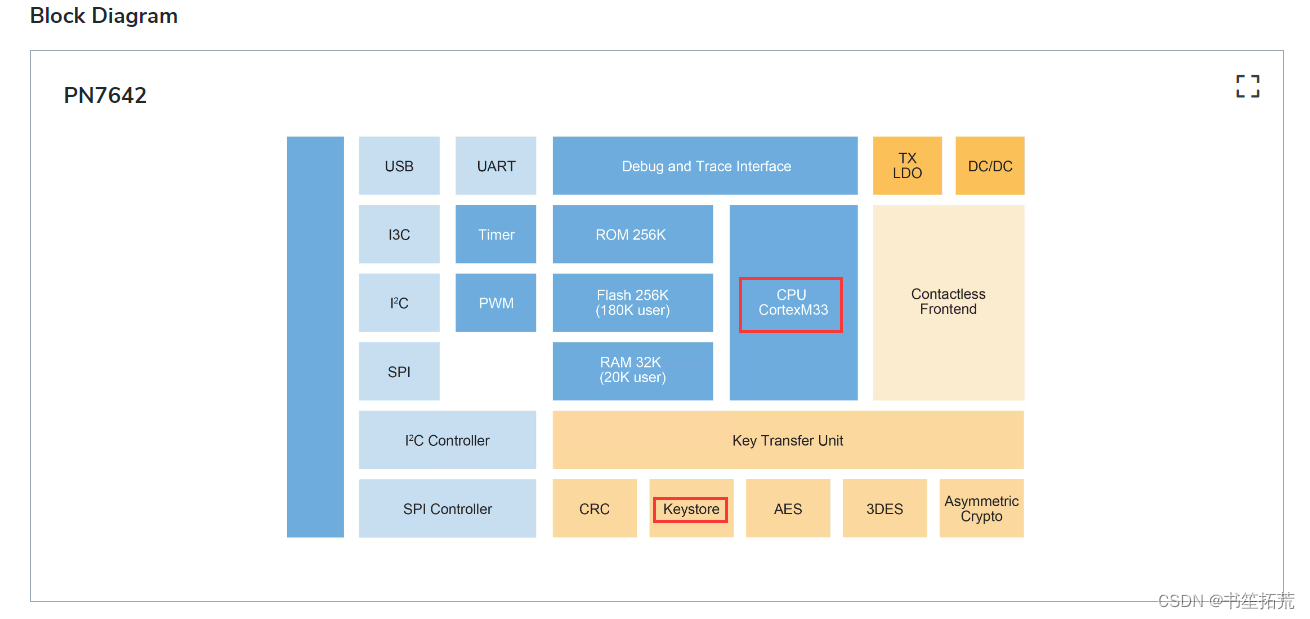

我的NPI项目之Android 安全系列 -- 用eSE还是iSE

是什么是iSE,什么又是eSE?借用Secure-IC provides a silicon-proven Root of Trust | Secure-IC 从这两张图里面就能清晰的看到eSE和iSE的差异了。那么问题来了ST33J2M0是iSE还是eSE? eSE通常不是单单的一个Secure IP,而是一个combo chip(possesses two chips)。例如,nfc

初入FPGA之ISE遇到的问题(1)

1.编译时出现报错: ERROR:Pack:1107 - Pack was unable to combine the symbols listed below into a single IOB component because the site type selected is not compatible. 即名字为IP_LXXX_X的引脚只能作为专用输入引脚,而不能作为输出引

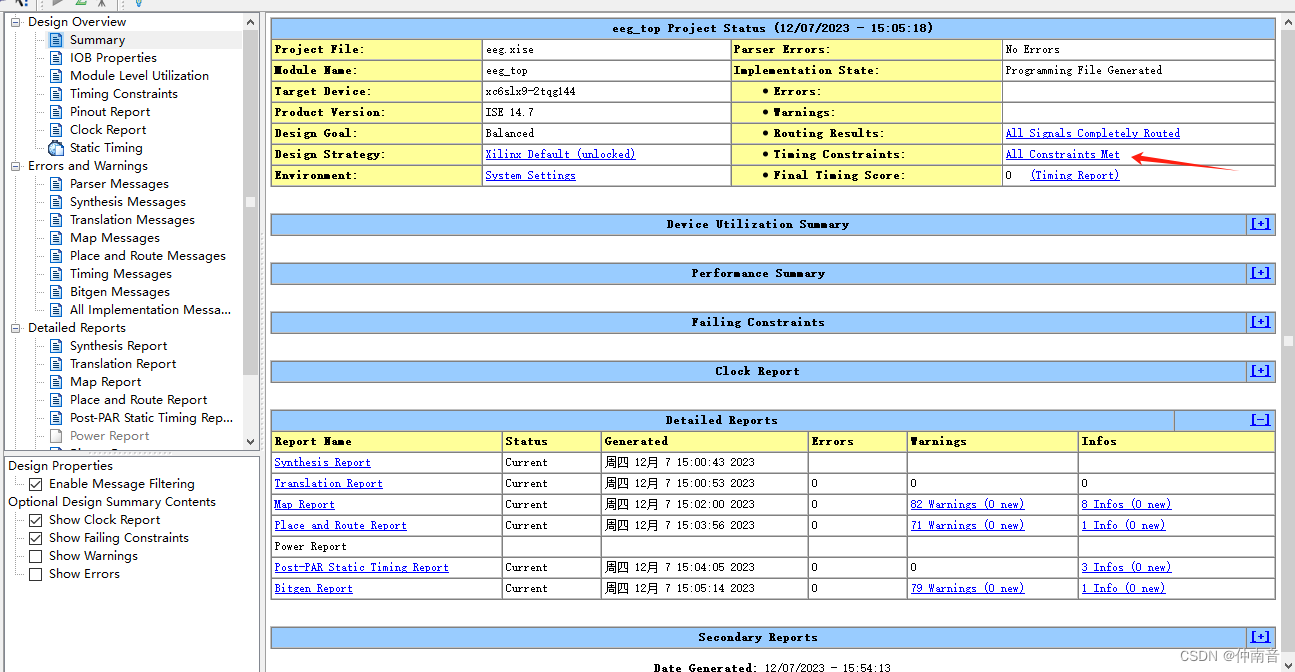

Xilinx FPGA——ISE时序约束“建立时间不满足”问题解决记录

一、现象 最近使用赛灵思的FPGA设计项目时,出现时序约束失效问题。 点进去发现如下: 一个始终约束没有生效,有多处报错。 二、原因 出现这个问题的原因是,建立时间不满足。 时序违例的主要原因是建立时间和保持时间不满足要求,那么什么情况下会出现建立时间和保持时间不满足要求呢? 建立时间不满足要求通常是因为组合逻辑处

【XILINX】ISE chipscope出现错误 Can‘t load jre bin client jvm.dll

记录一个ISE软件使用过程中遇到的问题及解决方案。 问题 ISE chipscope出现错误 Can't load jre bin client jvm.dll C:\Xilinx\14.7\ISE_DS\ISE\bin\nt C:\Xilinx\14.7\ISE_DS\.xinstall\bin\nt C:\Xilinx\14.7\ISE_DS\.xinstall\bin\nt64 C:

Xilinx FPGA——ISE的UCF时序约束

时序约束是我们对FPGA设计的要求和期望,例如,我们希望FPGA设计可以工作在多快的时钟频率下等等。 设计是要求系统中的每一个时钟都进行时序约束。 一、分组约束语法(NET、PIN、INST) TNM是最基本的分组约束语法,其语法定义如下: {NET|INST|PIN} "net_or_pin_or_inst_name"

FPGA实验:实验一 熟悉Xilinx幵发工具ISE

文章目录 一、创建工程二、添加HDL源文件三、仿真 实验目的: 了解FPGA的开发流程;熟悉Spartan-3E开发套件的功能特点;清楚PicoBlaze 8位控制器的特性。 相关文件: 链接:https://pan.baidu.com/s/1xhmYqBMyNjkAFeaT8KPtwQ 提取码:s96i 一、创建工程 选择菜单栏中的File—New Project 选

ISE使用中无法打开已有工程的问题

当使用ISE打开已有文件时,弹出这样的提示框。应该是当前文件包含在含有中文的路径下造成的原因。 将文件或文件的副本保存在不含中文的路径下,选择“File”-“Open Project”-选择新路径下的文件,即可正常打开。

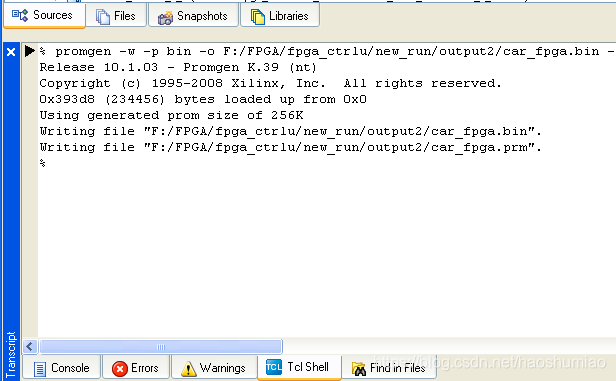

ISE中如何生成bit文件和bin文件

有两种方法可以得到bin文件 方法一、在 Generate Programming File中,对其参数进行如下设置,选中bit文件和bin文件,运行Generate Programming File,在工程目录下即可同时得到bit文件和bin文件。 方法二、利用ISE中自带的promgen.exe 将生成的bit文件转换为bin文件 (1)在 TCLShell界面中输入命令行然后回车即可在对

基于xilinx ise开发流程介绍

本文转自于http://blog.csdn.net/jbb0523/article/details/6907480 第3节 基于ISE的开发流程 本节所有的讲解都以例4-3所示的代码为基础展开。 例4-3 ISE开发流程演示代码,将输入的数据加1寄存并输出。 module test(clk, din, dout); input clk; input [7:0] di

第4章 ISE开发环境使用指南[FPGA开发实用教程]——第3节 基于ISE的开发流程

第3节 基于ISE的开发流程 本节所有的讲解都以例4-3所示的代码为基础展开。 例4-3 ISE开发流程演示代码,将输入的数据加1寄存并输出。 module test(clk, din, dout); input clk; input [7:0] din; output [7:0] dout; reg [7:0] dout; always @(posedge cl