本文主要是介绍FPGA实验:实验一 熟悉Xilinx幵发工具ISE,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 一、创建工程

- 二、添加HDL源文件

- 三、仿真

实验目的:

- 了解FPGA的开发流程;

- 熟悉Spartan-3E开发套件的功能特点;

- 清楚PicoBlaze 8位控制器的特性。

相关文件:

链接:https://pan.baidu.com/s/1xhmYqBMyNjkAFeaT8KPtwQ

提取码:s96i

一、创建工程

- 选择菜单栏中的File—New Project

- 选择下列参数,并单击Next按钮。

- Family(器件类别):Spartan3E;

- Device(器件型号):XC3S500E;

- Package(封装):FG320;

- Speed(速度等级):-4;

- Synthesis Tool(综合工具):XST(VHDL7Verilog);

- Simulator(仿真工具):ISE Simulator (VHDL/Verilog);

- Preferred Language(偏好语言):Verilog

- Finish

二、添加HDL源文件

- 单击New Source按钮

- 将文件

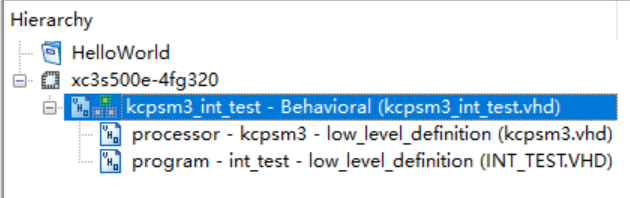

INT_TEST.VHD、kcpsm3.vhd、kcpsm3_int_test.vhd添加进去

- 现在分层显示列表区域变成了这样

- 单击Add Copy of Source按钮

5. 将文件test_bench.vhd添加进去

6. 现在分层显示列表区域变成了这样

三、仿真

- 选中

Simulation模式

- 选择菜单栏里的Process→Process Properties按钮

- 修改仿真时间为

25000ns

- 双击 Simulate Behavioral Model 仿真设计

- 然后等一会就会弹出一个仿真的程序界面,包含着两个文件:

.wcfg以波形方式显示仿真结果,.vhd以HDL格式显示testbench文件。

6. 打开.wcfg文件查看波形结果。

这篇关于FPGA实验:实验一 熟悉Xilinx幵发工具ISE的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!