本文主要是介绍基于DAC1282的数模转换电路设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

一、数模转换原理

1.1 数字信号与模拟信号

1.2 DAC(Digital to Analog Converter)数模转换原理

1.3 DCA受限条件

二、DAC1282 面向抗震应用的低失真数模转换器

2.1芯片简介

2.2 芯片框图

2.3 引脚介绍

2.4 电源及时钟

2.5详细说明

2.5.1概述

2.5.2 芯片配置

2.5.2.1 片选

2.5.2.3 DIN与DOUT

一、数模转换原理

1.1 数字信号与模拟信号

数字信号:在时间和量值上都是离散的。

模拟信号:在时间和量值上都是连续的。

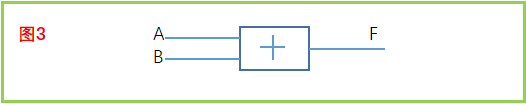

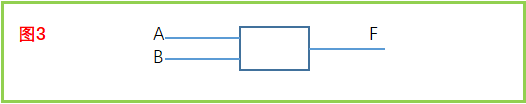

1.2 DAC(Digital to Analog Converter)数模转换原理

数模转换即将离散电平转为连续波形。

数字信号的离散量(高低电平)组成多位二进制数,对其加权展开转换为十进制数据后连接成平滑曲线即可获得对应模拟信号。

一般使用低通滤波器与DAC进行配合使用,对阶梯信号进行滤波,使转换后的波形更加平滑。

1.3 DCA受限条件

采样率,采样率越高,波形还原越真实。

抖动,系统钟抖动将影响还原精度。

偏移,无输入时DAC产生的输出即为偏移量。

增益误差,对信号进行加权增益时产生的误差。

二、DAC1282 面向抗震应用的低失真数模转换器

2.1芯片简介

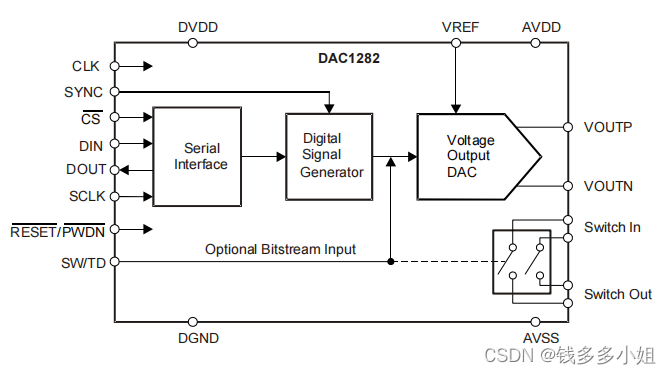

DAC1282是一款全集成数模转换器 (DAC),此转换器可提供低失真,数字合成电压输出,适合于测震设备的测试。集成了一个数字信号生成器,一个DAC,和一个可生成正弦波,dc,和脉冲输出电压的输出放大器。

输出频率可编程范围为0.5HZ至250HZ之间并且震级由模拟和数字控制进行计算。模拟增益和数字增益分别可在6dB步长和0.5dB步长内调节。模拟增益设置与ADS1282上那些用于高分辨率增益下测试的设置相匹配。

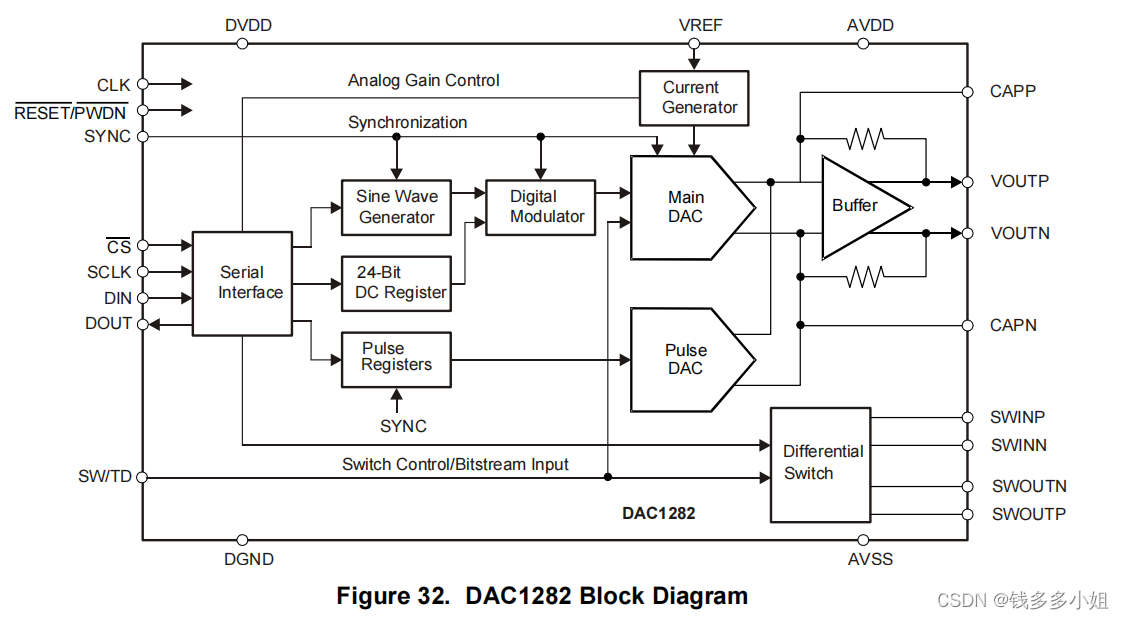

2.2 芯片框图

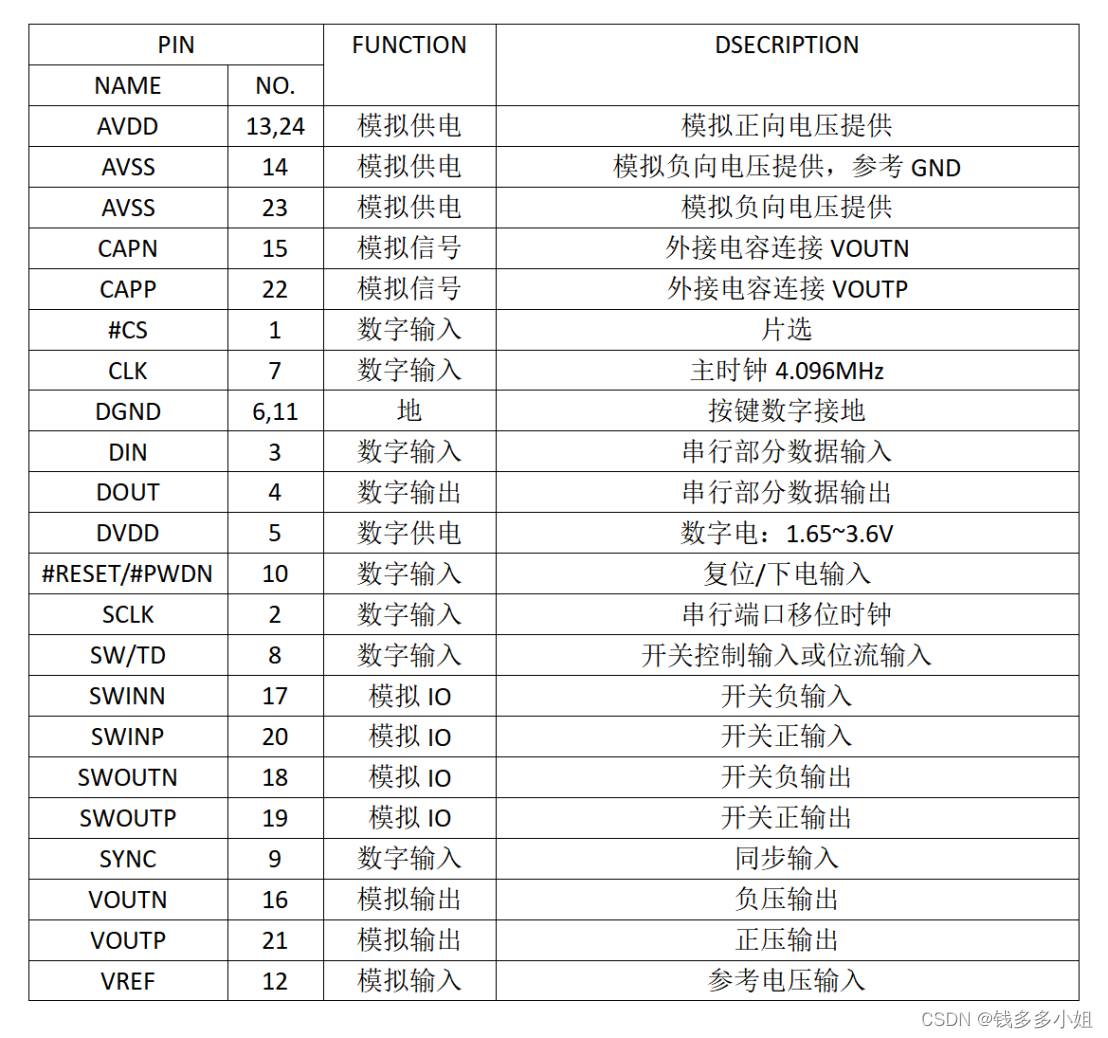

2.3 引脚介绍

2.4 电源及时钟

模拟电源可以是单个5V或双极±2.5 V。数字电源范围为1.65 V至3.6V。

电源可以按任何顺序顺序开启或关闭,但模拟或数字输入不得分别超过AVDD或AVSS或DVDD。在这种情况下,内部ESD保护二极管可能开始进行。输入电流必须始终按照绝对最大额定值表中的规定进行限制。

复位低有效。

2.5详细说明

2.5.1概述

DAC1282是一种数模转换器(DAC),可以产生低失真正弦波和脉冲输出信号,可以满足地震记录设备测试要求。

与外部控制器以SPI串行接口连接,可以接收外部控制器进行配置。

其电压输出完全差分,并通过VOUTP/VOUTN引脚输出。

CAPP/CAPN引脚连接到外部滤波器电容,以降低输出噪声。

参考输入电压设置DAC1282全尺寸输出。在VREF和AVSS引脚之间施加DAC参考电压。

DAC被优化为使用5V参考数据进行操作。

正弦波发生器可通过寄存器进行编程,以设置正弦频率和振幅。频率范围可编程从0.4883 Hz到250 Hz。输出电平由模拟增益(6dB步)和数字增益(0.5dB步)控制。

2.5.2 芯片配置

2.5.2.1 片选

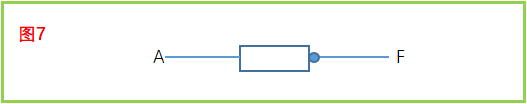

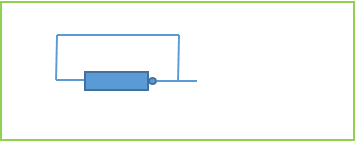

CS(芯片选择)选择DAC1282进行通信。要选择设备,请将CS拉低。在命令序列持续期间,CS必须保持在较低水平。当CS值过高时,重置串行接口,忽略输入命令,DOUT进入高阻抗状态。

2.5.2.2 串行时钟

串行时钟(SCLK)是一个由施密特触发的输入,用于时钟数据进出DAC1282。SCLK可以高也可以低。如果SCLK空闲低,则SPI超时特性处于活动状态。如果SCLK空闲较高,将禁用SPI超时功能。尽管内置了施密特触发器,SCLK还是要尽可能保持干净,以防止故障意外移动数据。串联端接印刷电路板(PCB)痕迹通常有助于减少铃声和超调(串联端接电阻约为20 Ω至50 Ω)。如果SCLK低2个18 fCLK周期,串行接口将重置。该超时特性可用于在发生噪声故障时自动恢复SPI端口。避免在此时间间隔之后启动新命令,以防止在下一个命令瞬间出现意外的串口重置。

2.5.2.3 DIN与DOUT

上升沿输入数据,下降沿输出。

手册资料下载连接:https://pan.baidu.com/s/1QDvZxsF0dzyCoQFGOxAdIQ

提取码:t35m

这篇关于基于DAC1282的数模转换电路设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!