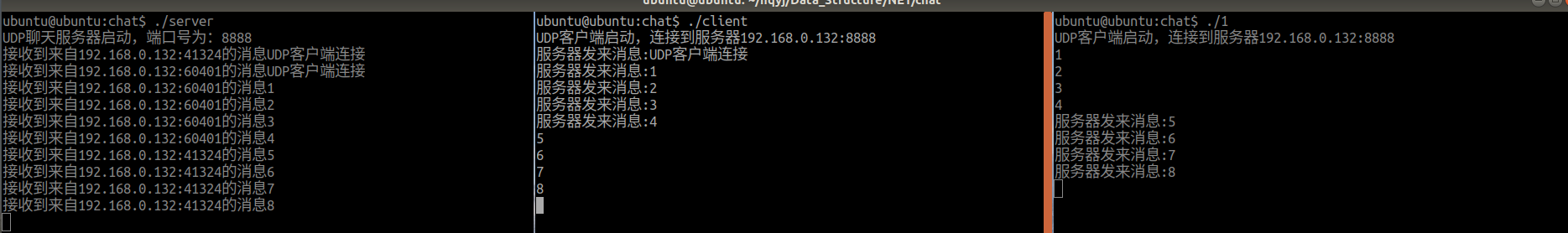

本文主要是介绍FPGA UDP RGMII 千兆以太网(1),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1 RGMII 接口

PHY 的 MII 接口有很多种, 例如 MII、 GMII、 RGMII、 SGMII、 XGMII、 TBI、 RTBI 等。其中 RGMII的主要优势在于,它可同时适用于 1000M、 100M、 10M 三种速率,而且接口占用引脚数较少。但也存在缺点,其一, PCB 布线时需要尽可能对数据、控制和时钟线迚行等长布线。其二,对其时序约束。对较为严格。

基于FPGA千兆以太网的开发(1)

RGMII(Reduced Gigabit Media Independent Interface)是Reduced GMII(吉比特介质独立接口)。RGMII均采用4位数据接口,工作时钟125MHz,并且在上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。

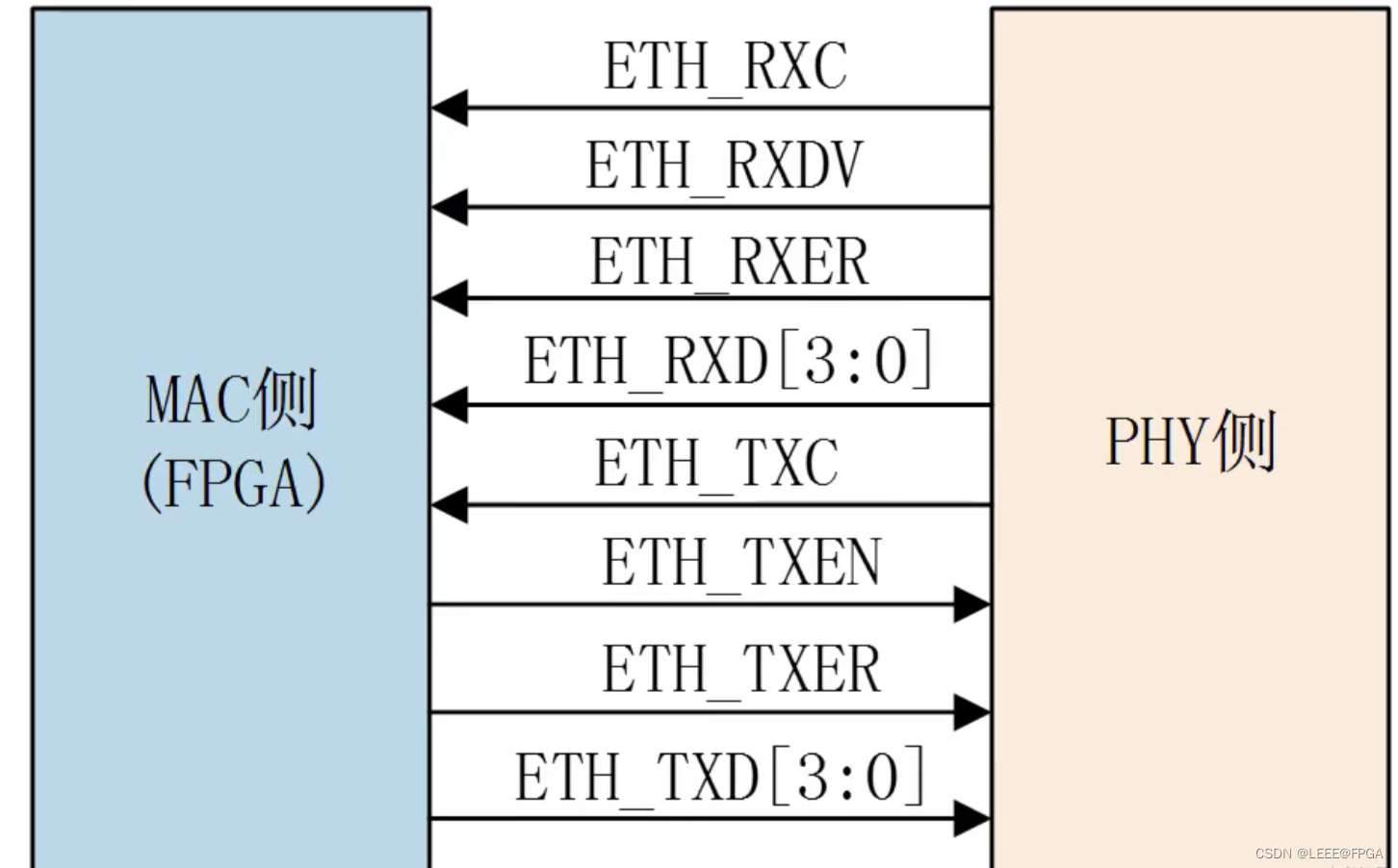

2 RGMII信号定义

RGMII 使用 4bit 数据接口采用上下沿 DDR(Double Data Rate)的方式在一个时钟周期内传输 8bit 数据信号,即上升沿发送或者接收数据的低 4 位[3:0],下降沿发送或者接收数据的高 4 位[7:4]。 同理,使用 1bit 控制接口采用 DDR的方式在一个时钟周期内传输 2bit 控制信号,即在上升沿发送或者接收数据使能信号(TX_EN、RX_DV),下降沿发送数据错误信号与

这篇关于FPGA UDP RGMII 千兆以太网(1)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!