rgmii专题

RK3288 RGMII 连接百兆PHY DP83822

RGMII 通常用于连接千兆PHY, 使用125M时钟,但公司的板子使用RGMII连接百兆PHY DP83822 ,这里记录一下调试该PHY 芯片的过程。 电路图如下: 首先,修改设备树: 重新编译内核升级boot.img到板子,发现PHY的link指示灯亮,说明MAC和PHY之间的SMI接口通信正常,但怎么都ping不同局域网内IP, ifconfig 查看网卡数据流量

RGMII接口--->(001)FPGA实现RGMII接口(一)

(001)FPGA实现RGMII接口(一) 1 目录 (a)FPGA简介 (b)IC简介 (c)Verilog简介 (d)FPGA实现RGMII接口(一) (e)结束 1 FPGA简介 (a)FPGA(Field Programmable Gate Array)是在PAL (可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASI

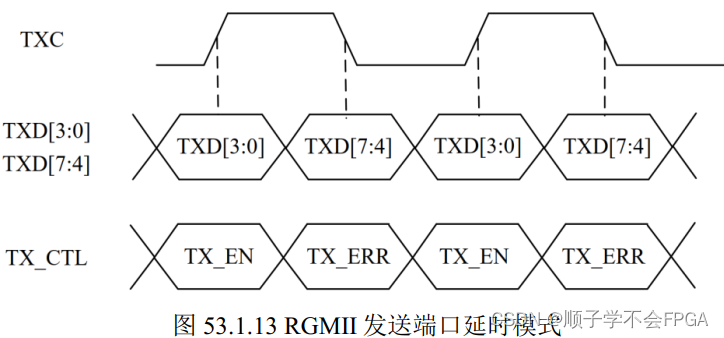

基于FPGA的UDP协议栈设计第七章_RGMII模块设计

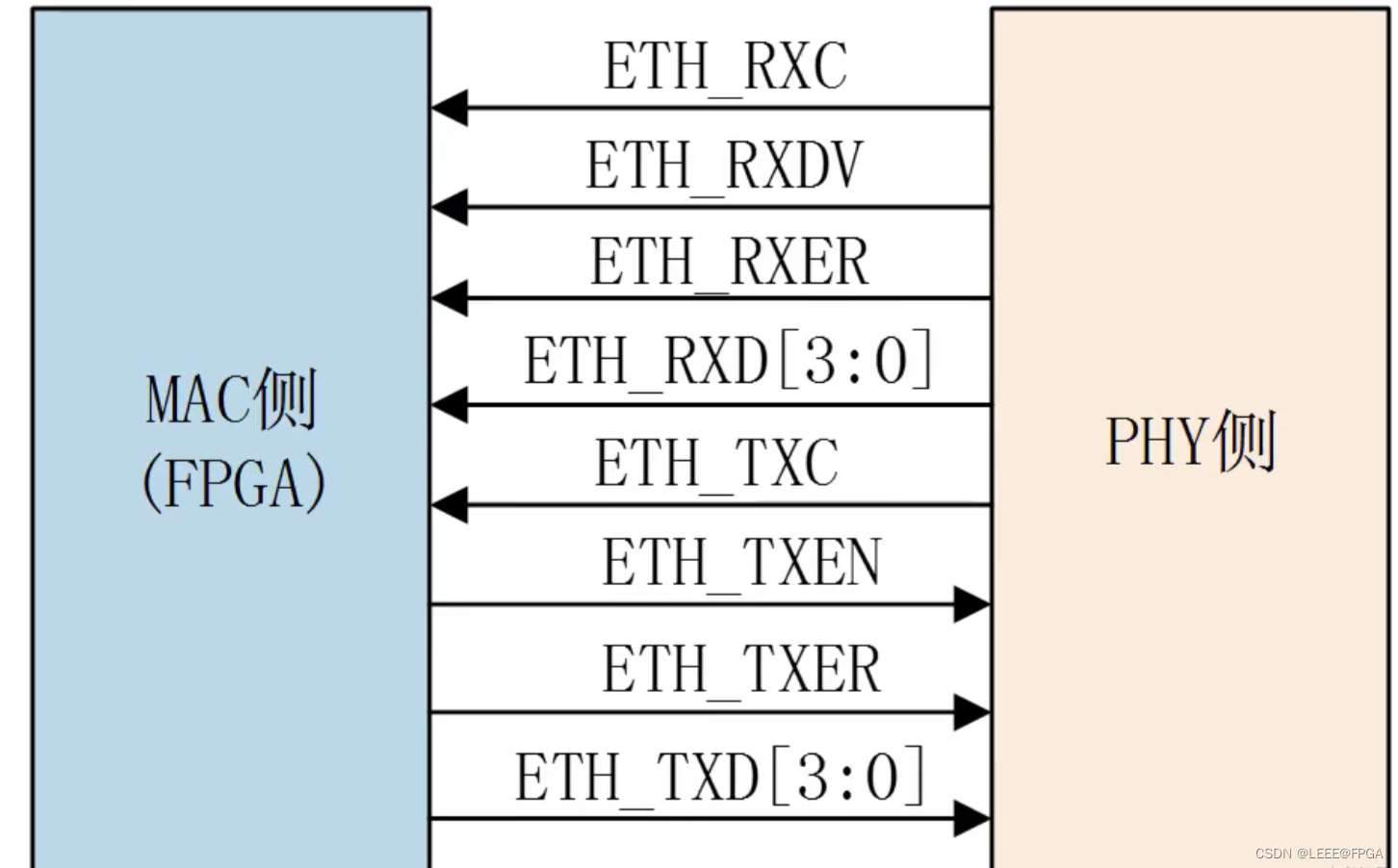

文章目录 前言:一、GMII和RGMII简介1.1、接收数据过程1.2、发送数据过程 二、IDDR、ODDR、IDEALY2和ODELAY2三、BUFG和BUFIO四、FPGA代码设计 前言: 该部分内容主要需要掌握各种IO和时钟相关的原语使用 一、GMII和RGMII简介 以太网的通信离不开PHY芯片,PHY芯片实现实现了RGMII接口到网口(RJ45)的转换,RGMII接

T2080 AR8031 RGMII to 1000Base-X(fiber)

前段时间在调试FT-M6678和C6678的板卡,结果中途来了一个T2080网络配置的更改需求,就临时处理了一下,花了一点功夫,记录下来,为大家做个参考。 这个问题完成后,就得继续开发FT-M6678了~ uboot下面phy配置更改(board/freescale/tx208xrdb/eth_t208xrdb.c) a. 配置芯片模式配置为B

FPGA——三速自适应以太网设计(2)GMII与RGMII接口

FPGA——以太网设计(2)GMII与RGMII 基础知识(1)GMII(2)RGMII(3)IDDR GMII设计转RGMII接口跨时钟传输模块 基础知识 (1)GMII GMII:发送端时钟由MAC端提供 下降沿变化数据,上升沿采集数据 (2)RGMII 时钟是双沿采样 RGMII:ETH_RXCTL线同时表示有效和错误,有效和错误位相异或得到。 时钟偏移,方便

FPGA UDP协议栈:基于88E1111,支持RGMII、GMII、SGMII三种模式,提供3套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐我这里已有的以太网方案本协议栈的 1G-UDP版本本协议栈的 10G-UDP版本本协议栈的 25G-UDP版本1G 千兆网 TCP-->服务器 方案1G 千兆网 TCP-->客户端 方案10G 万兆网 TCP-->服务器+客户端 方案 3、该UDP协议栈性能4、详细设计方案设计架构框图网络调试助手网络PHYIDELAYE源语1G/2.5G Ethern

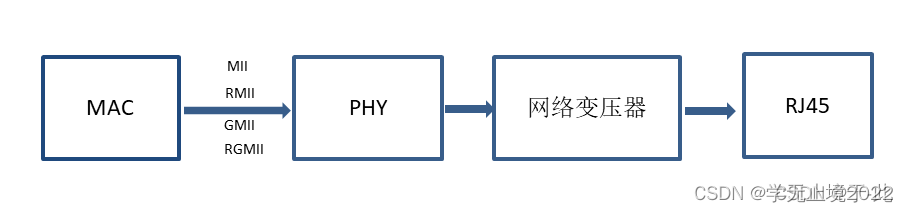

【必读】从MII到RGMII,一文了解以太网PHY芯片不同传输接口信号时序!

1、概述 不管是使用FPGA还是ARM,想要实现以太网通信,都离不开以太网PHY芯片,其功能如下所示,FPGA或者ARM将以太网数据发送给PHY芯片,PHY会将接收数据转换成模拟的差分信号传输到RJ45座子,最后通过网线与CPU、FPGA等网线连接的设备通信。PHY芯片实现的功能相当于OSI模型中的物理层。 图1 phy信号传输图 上述介绍适用于三速以太网(10M/100

MII、RMII、GMII、RGMII接口是什么 用在什么地方

mac芯片和phy芯片之间的通信接口 MII(Media Independent interface):媒体独立接口,也叫介质无关接口。它是MAC和PHY之间的通信接口。MII数据接口有2根控制线和16根数据线组成。当CLK信号为25MHz(对应100Mb/s)或2.5MHz(对应10Mb/s)。 RMII(Reduced Media Independent Interface):独立于介质接

FPGA UDP RGMII 千兆以太网(1)

1 RGMII 接口 PHY 的 MII 接口有很多种, 例如 MII、 GMII、 RGMII、 SGMII、 XGMII、 TBI、 RTBI 等。其中 RGMII的主要优势在于,它可同时适用于 1000M、 100M、 10M 三种速率,而且接口占用引脚数较少。但也存在缺点,其一, PCB 布线时需要尽可能对数据、控制和时钟线迚行等长布线。其二,对其时序约束。对较为严格。 基于FPGA千

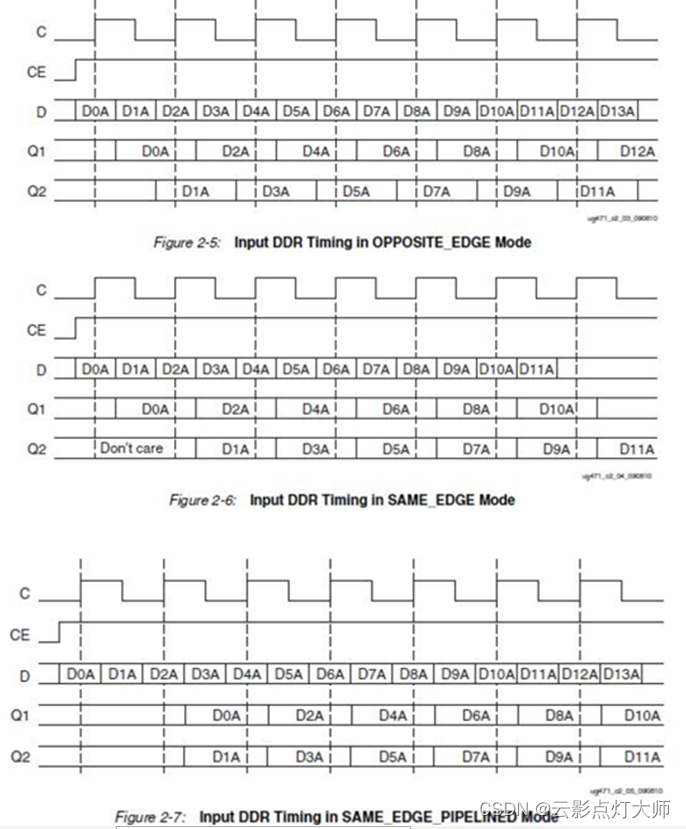

FPGA UDP RGMII 千兆以太网(2)IDDR

1 xilinx原语 在 7 系列 FPGA 中实现 RGMII 接口需要借助 5 种原语,分别是:IDDR、ODDR、IDELAYE2、ODELAYE2(A7 中没有)、IDELAYCTRL。其中,IDDR和ODDR分别是输入和输出的双边沿寄存器,位于IOB中。IDELAYE2和ODELAYE2,分别用于控制 IO 口输入和输出延时。同时,IDELAYE2 和 ODELAYE2 的延时值需要使

MII、RMII、 SMII、GMII、RGMII、SMI接口介绍

简要介绍 这几种接口是我们常说的网卡中应用的接口,应用于MAC和PHY直接的通信接口,符合IEEE定义的标准,不同厂家生产的网卡也都是按照标准生产的,所以我们能直接换网卡使用。 接口说明 SMI接口是MAC对PHY的控制接口,叫做站管理接口,总共两根线,一根时钟线,一根数据线。 MII接口是MAC与PHY之间的数据通信接口,叫做介质独立接口。 而RMII、 SMII是对MII的简化,缩减了