本文主要是介绍AD9361+zedboard(ZYNQ7020)的SDK工程(上),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1.准备工具

vivado2018.3

HDL源码:https://wiki.analog.com/resources/fpga/docs/releases

no_os:https://github.com/analogdevicesinc/no-OS

注意:HDL源码下载的版本要与vivado一致,我这里是2018.3

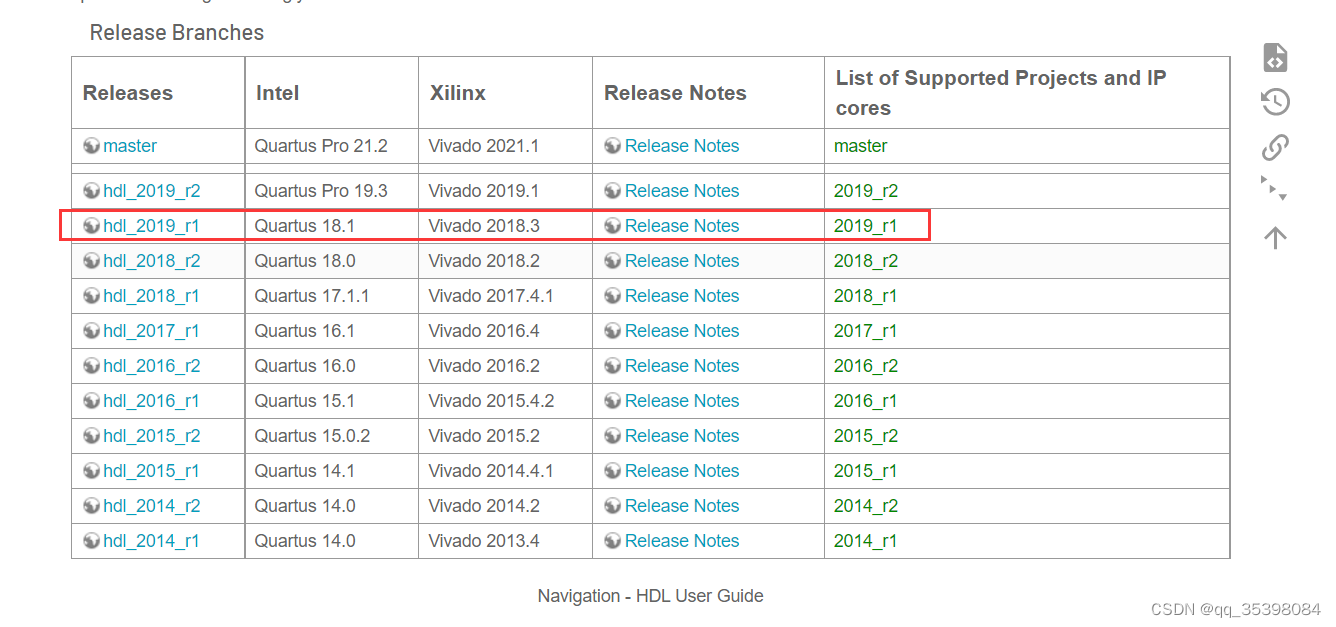

HDL版本选择

2.构建vivado工程

2.1编译源文件

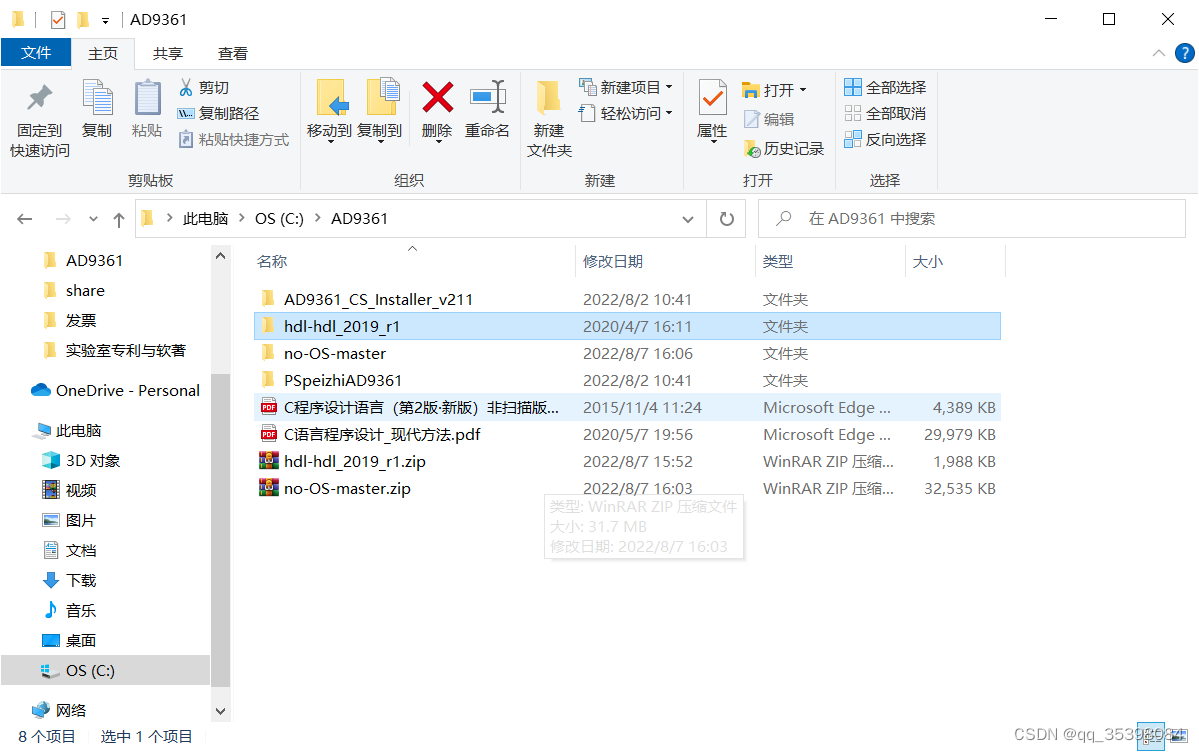

解压下载的HDL文件的压缩包

进入该文件夹C:\AD9361\hdl-hdl_2019_r1\projects\fmcomms5\zc702就是上一步解压完的那个文件夹里的路径,我这用的板子是ZEDBOARD,芯片是ZYNQ7020,所以选的是zc702文件夹。

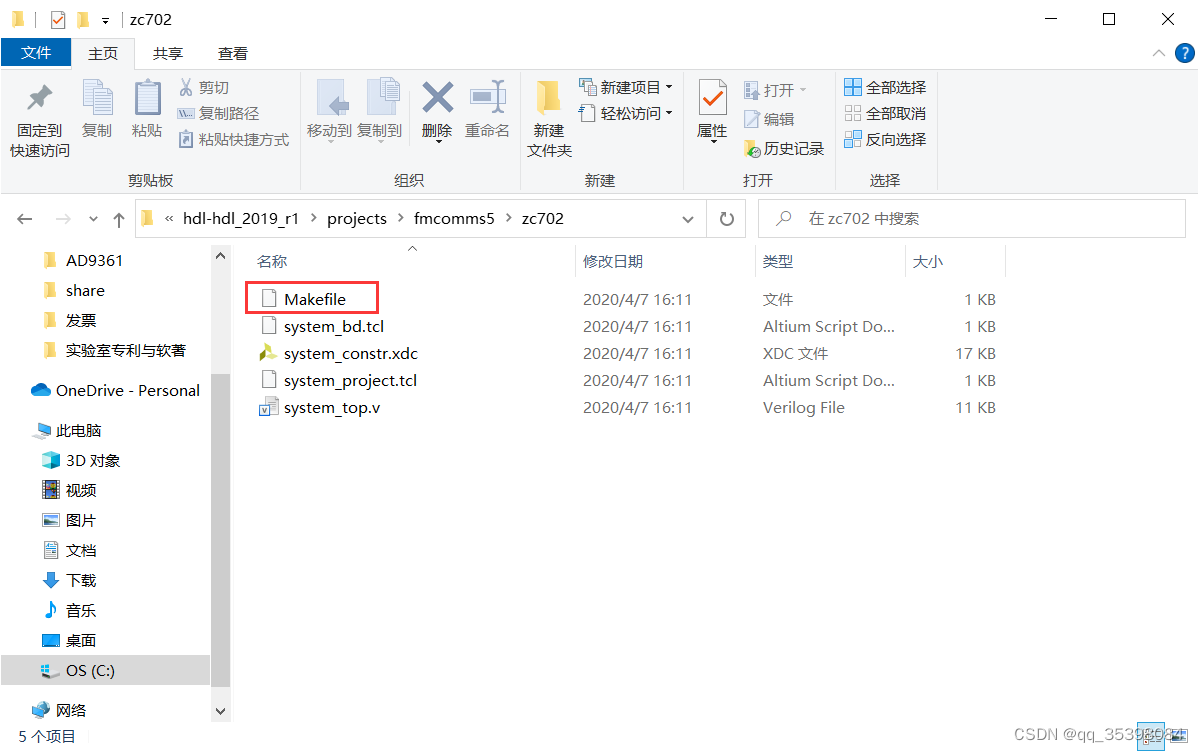

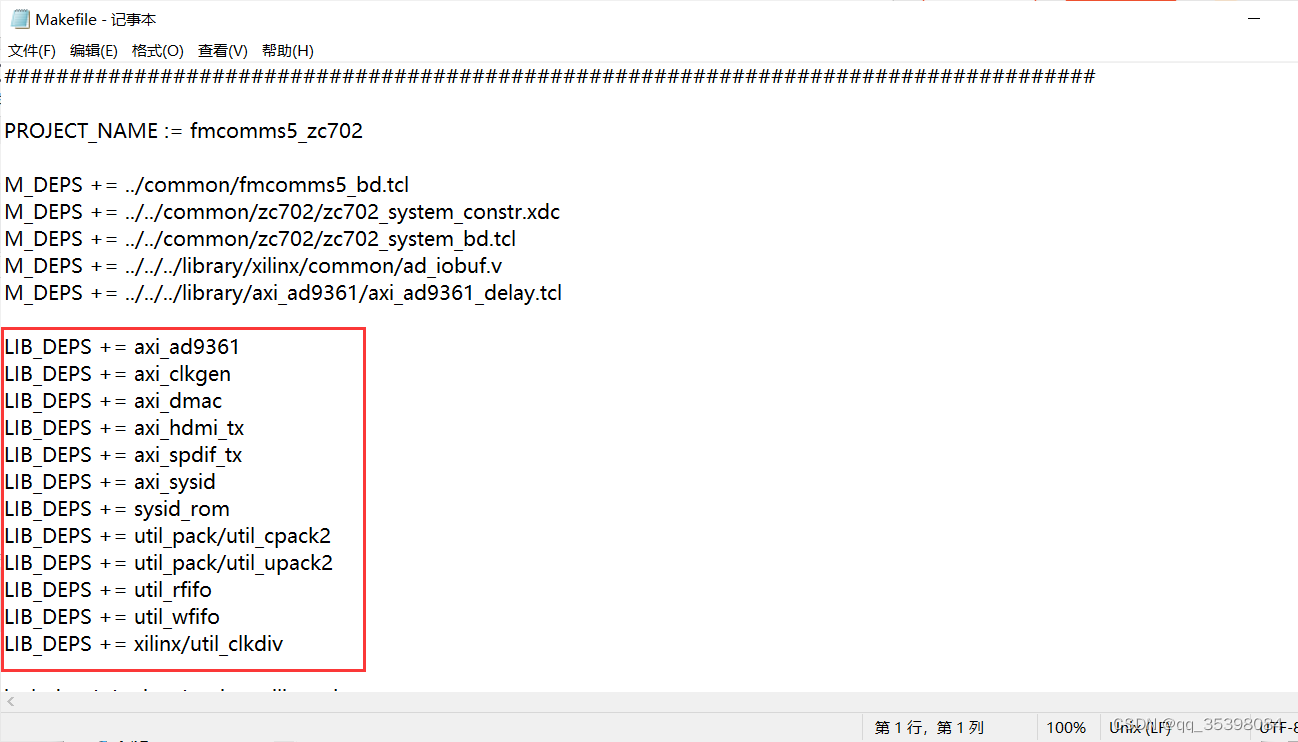

记事本打上一步文件夹中的makefile文件,可以查看依赖环境,这里不要关闭makefile。

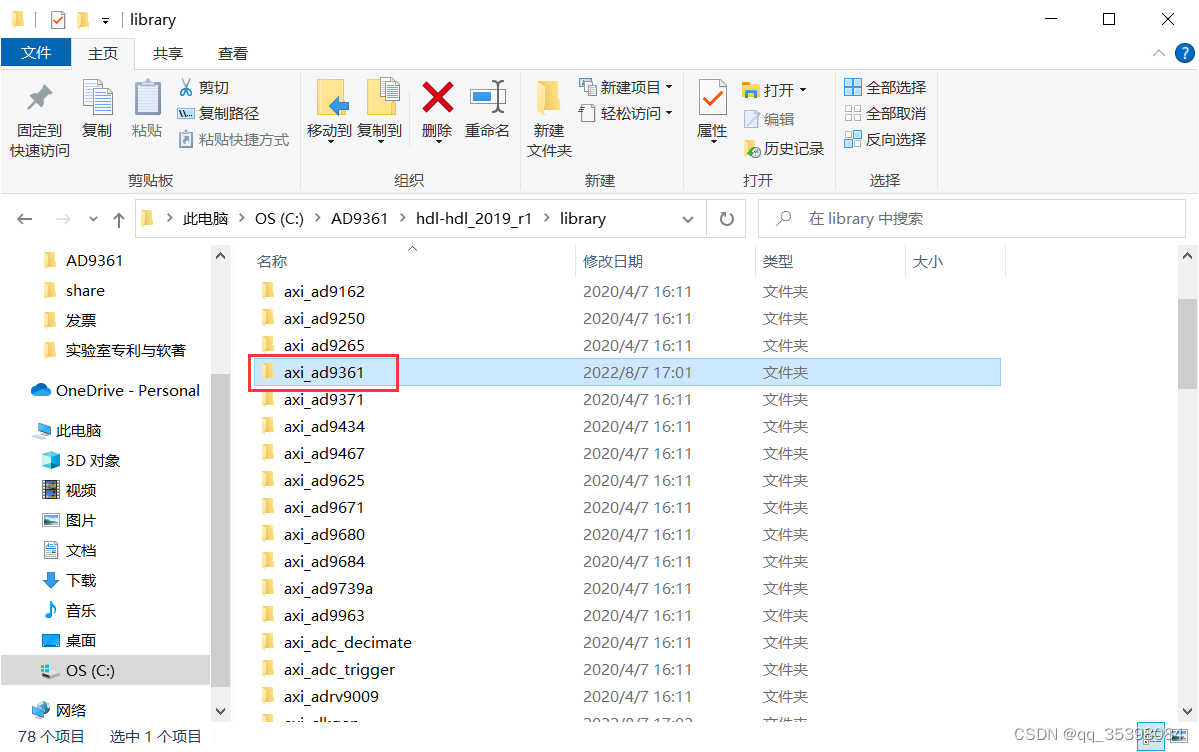

进入C:\AD9361\hdl-hdl_2019_r1\library的库文件夹,找到上面makefile的第一项axi_ad9361的库。双击进入axi_ad9361库文件夹,复制路径。

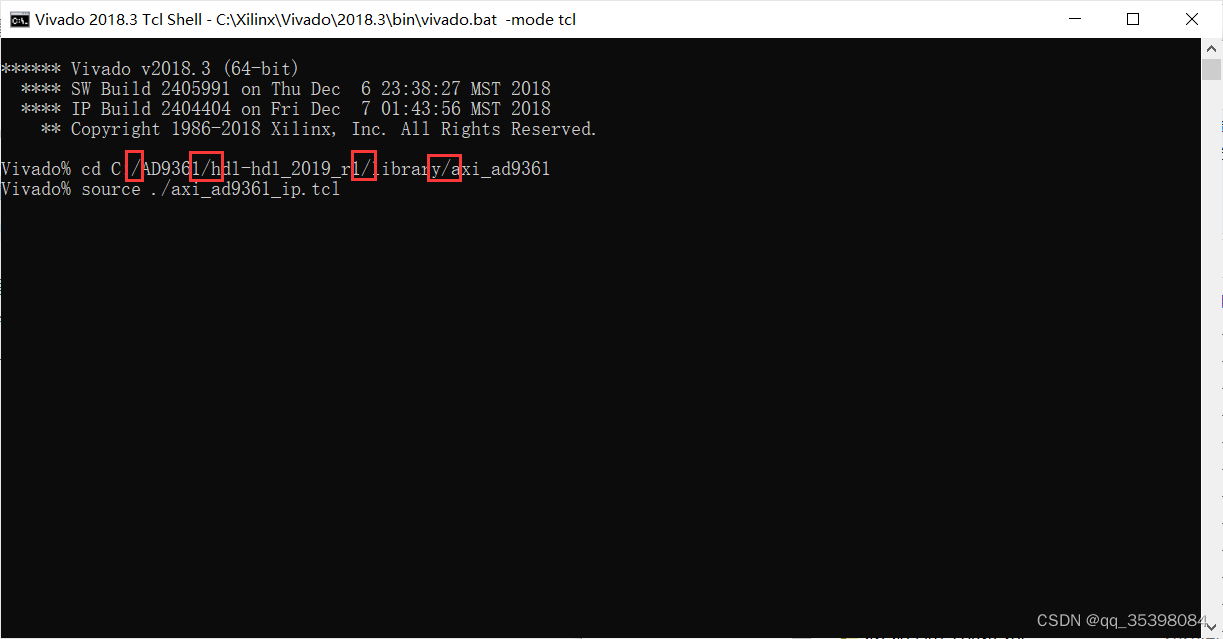

在“开始”里找到“Xilinx design tools”下的“vivado2018.3 Tcl shell”,打开后用Linux命令进入到上一步的axi_ad9361库文件夹中,这里的操作是输入 cd后空格,把上一步复制的路径粘贴一下,记得改斜杠为反斜杠,按enter键。然后输入 source ./axi_ad9361_ip.tcl按enter键后开始进行编译

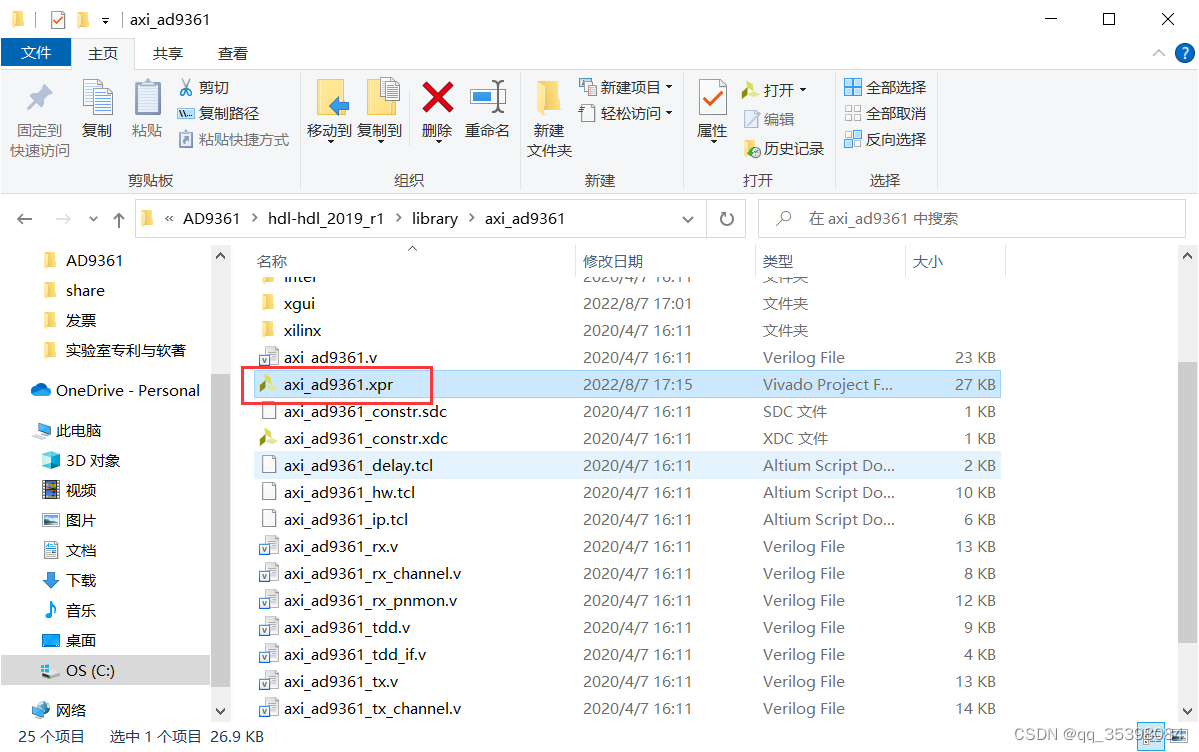

编译完生成“.xpr”文件,这就是vivado的工程文件。还没完,这只是第一个依赖库的编译,上面makefile中的依赖库都要编译依次,编译步骤就是进入对应的依赖库中,利用source命令编译带有**ip.tcl的文件。

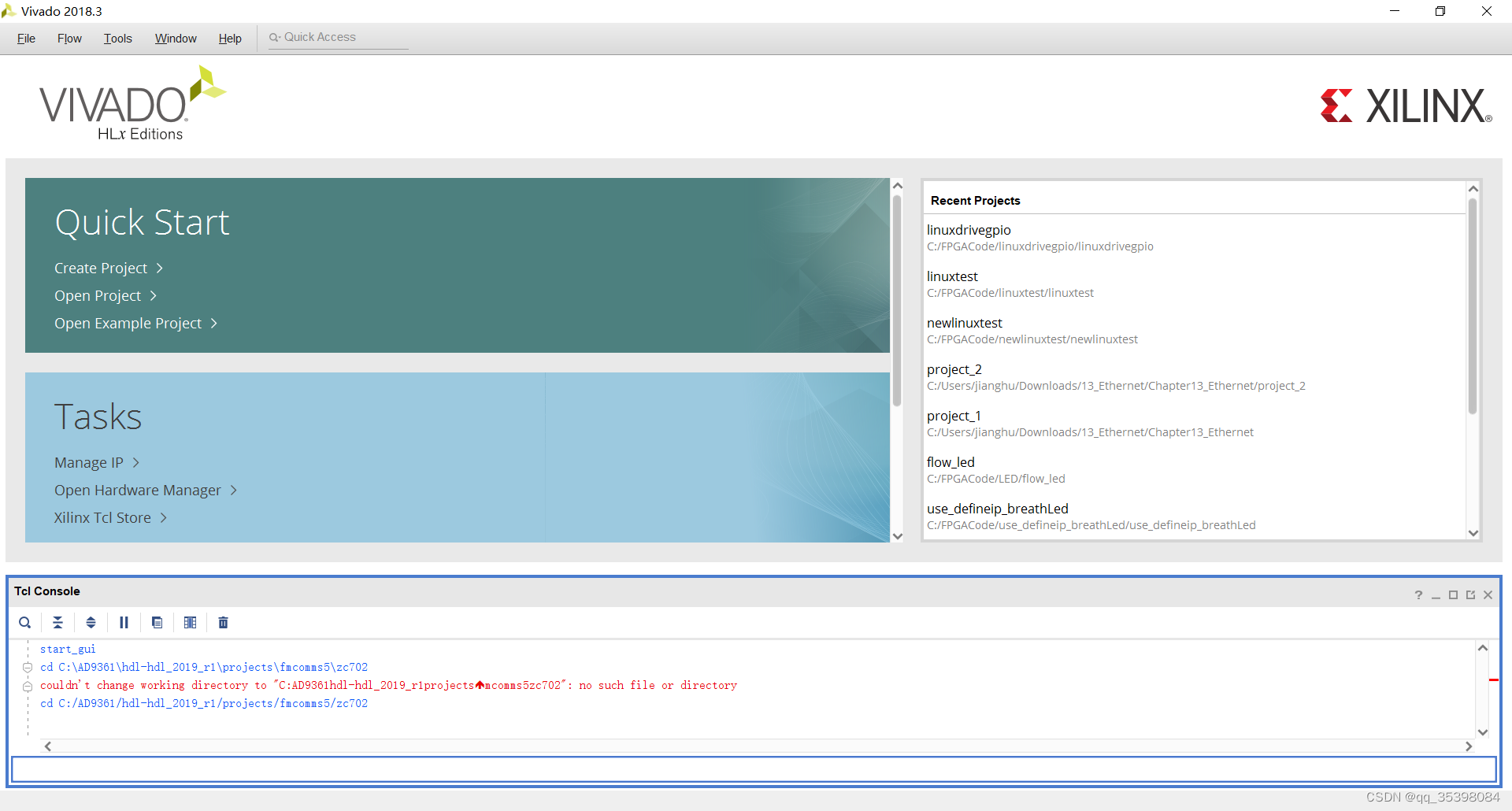

2.2接下来就是利用C:\AD9361\hdl-hdl_2019_r1\projects\fmcomms5\zc702的源码和TCL构建vivado工程了。打开vivado2018,在左下角的 tcl console中输入cd C:\AD9361\hdl-hdl_2019_r1\projects\fmcomms5\zc702

继续输入 source ./system_project.tcl 系统开始编译生成vivado工程

这篇关于AD9361+zedboard(ZYNQ7020)的SDK工程(上)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!