ad9361专题

创建 AD9361 的 vivado 工程,纯FPGA配置,不使用ARM程序

前言 AD9361 的配置程序,如果使用官方的,就必须用ps进行配置,复杂不好使,如果直接使用FPGA配置,将会特别的简单。 配置软件 创建一份完整的寄存器配置表 //************************************************************// AD9361 R2 Auto Generated Initialization Scri

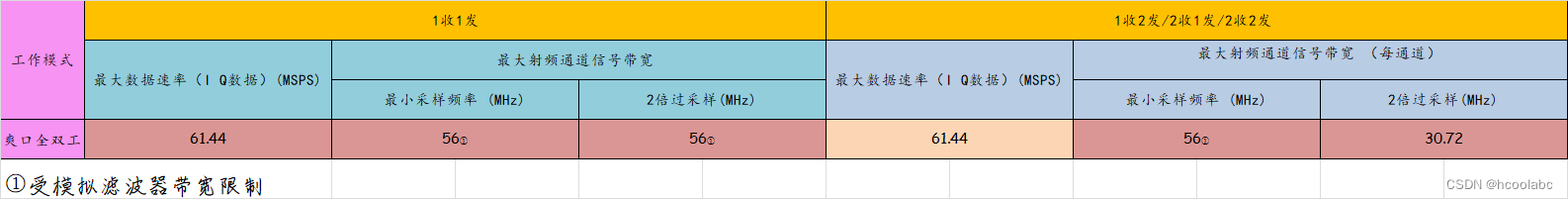

太速科技-FMC377_双AD9361 射频收发模块

FMC377_双AD9361 射频收发模块 FEATURES: ◆ Coverage from 70M ~ 6GHz RF ◆ Flexible rate 12 bit ADC/DAC ◆ Fully-coherent 4x4 MIMO capability, TDD/FDD ◆ RF ports: 50Ω Matched ◆ su

TQZC706开发板教程:在ZC706上运行AD9361

首先需要在github上下载两个文件,本例程用到的文件以及最终文件,我都会放在网盘里面,地址在本文的末尾,需要自行提取 在github上搜索hdl选择第一个-->选择版本-->我所使用的vivado是2018.3版本,所以这里我下载的是hdl_2019_r1-->在附录中下载资源-->下载对应版本的No-Os 把下载好的资源复制到虚拟机里解压缩,右键打开命令行 设置环境变量-->进入

FPGA_AD9361

1.集成12位DAC和ADC的一款器件,2个输入模拟通道和2个输出模拟通道 2.• TX频段:47 MHz至6.0 GHz • RX频段:70 MHz至6.0 GHz 3.SPI配置成LVDS或CMOS接口,也可以还可以选择FDD(频分双工——全双工,操作时需要两个独立的信道)或TDD(时分双工——半双工,只需要一个信道)工作方式 4.由于9361的寄存器较多,首先利用AD936X Eval

在pzp203上运行ad9361 no-os工程

0. 环境 - pzp203 - ubuntu18 + vivado2018 pzp203是一款plutosdr的国产兼容版。出厂默认是基于linux系统的,用libiio调用。软硬件兼容adalm-pluto。开发板提供网盘资料,是添加了板卡适配的。 1. hdl 1.1 准备源码 hdl https://github.com/analogdevicesinc/hdl/releas

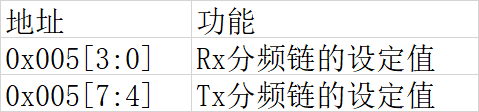

AD9361寄存器功能笔记之本振频率设定

LO的产生过程如图: 各个模块都有高灵活性。 1、参考时钟即是AD9361全局参考时钟,可以是外接晶振的片上DCXO,或是外部输入的有驱动能力的时钟信号。根据FM-COMMS5的设计,参考时钟可以使用时钟Buffer + 40MHz晶振构成的参考频率源。 (1)关于DCXO的说明:DCXO即数控晶体振荡器,AD9361通过外接晶体和内部数控电容构建DCXO,外接晶体谐振频

AD9361多片同步设计方法

本文基于ZC706+FMCOMMS5的平台,介绍了多片AD9361同步的方法。并将该设计移植到自行设计的ZYNQ7035+4片AD9361(实现8路同步收发)的电路板上。本设计采用纯逻辑的方式,仅使用了ZYNQ芯片的PL部分。 9361多芯片同步主要包括基带同步和射频同步两大块任务。其中基带采用AD9361自带的MCS功能实现。而射频同步分为两种方法,分别是内部本振法和外部本振法。 在正式介绍同

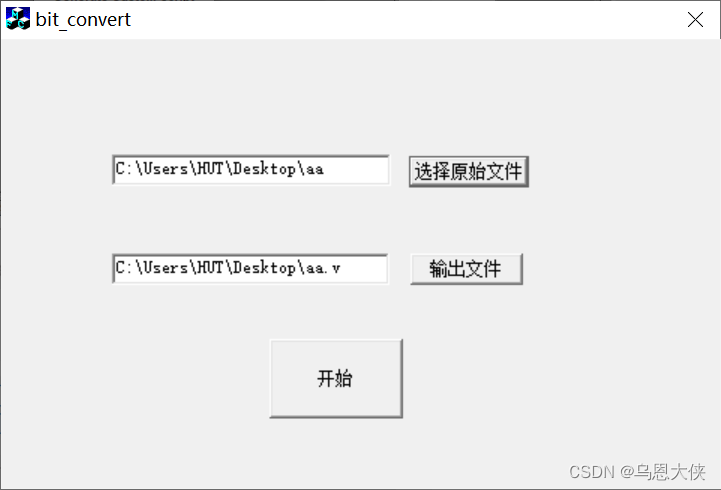

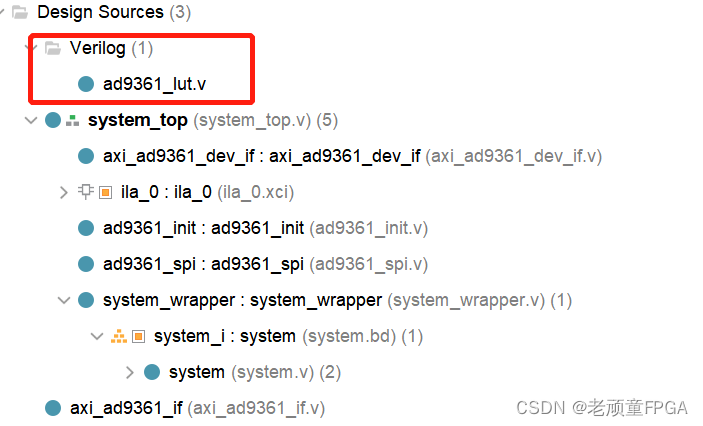

ZedBoard+AD9361_FPGA的PL端纯逻辑(verilog)配置控制9361(二)_将寄存器脚本文件转换成Verilog函数

在上一章节我们用AD936X Evaluation Software 软件生成了寄存器配的脚本文件FDD,具体内容如下:由于配置内容太多,大部分进行了省略。从配置文件中我们可以查看每个寄存器应该配置的参数,但是并不能直接在FPGA工程中调用,需要对文件格式进行修改,改成function函数形式,可以在工程中直接调用。如果人工一行一行修改,基本不可能,太费事,因此需要找出配置文件的规律,依靠自己编写

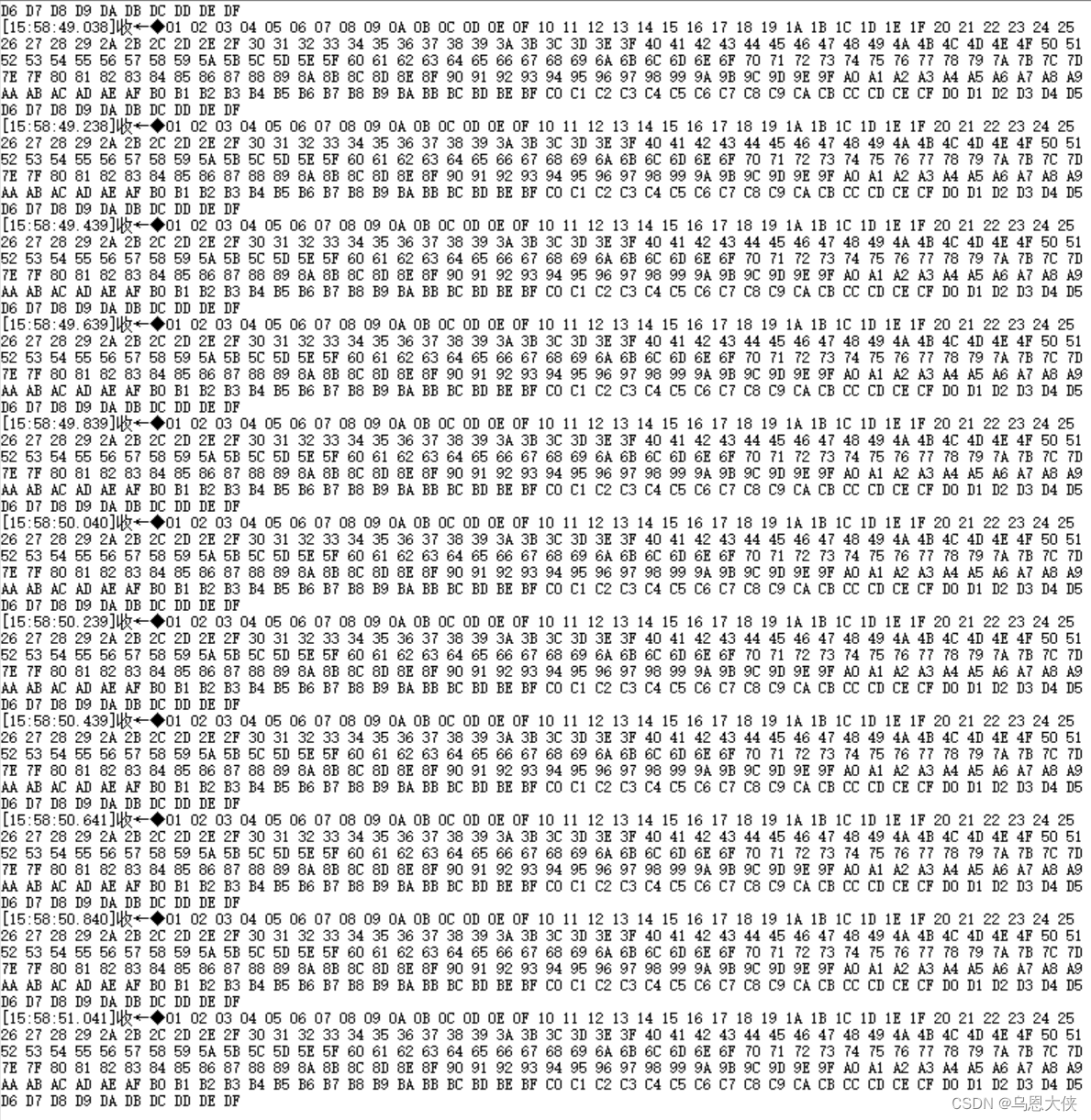

【基带开发】AD9361 生成1到223的递增数据

`timescale 1ns / 1ps//// Company: // Engineer: // // Create Date: 2022/06/29 17:50:56// Design Name: // Module Name: gen_Incremental_223// Project Name: // Target Devices: // Tool Versions:

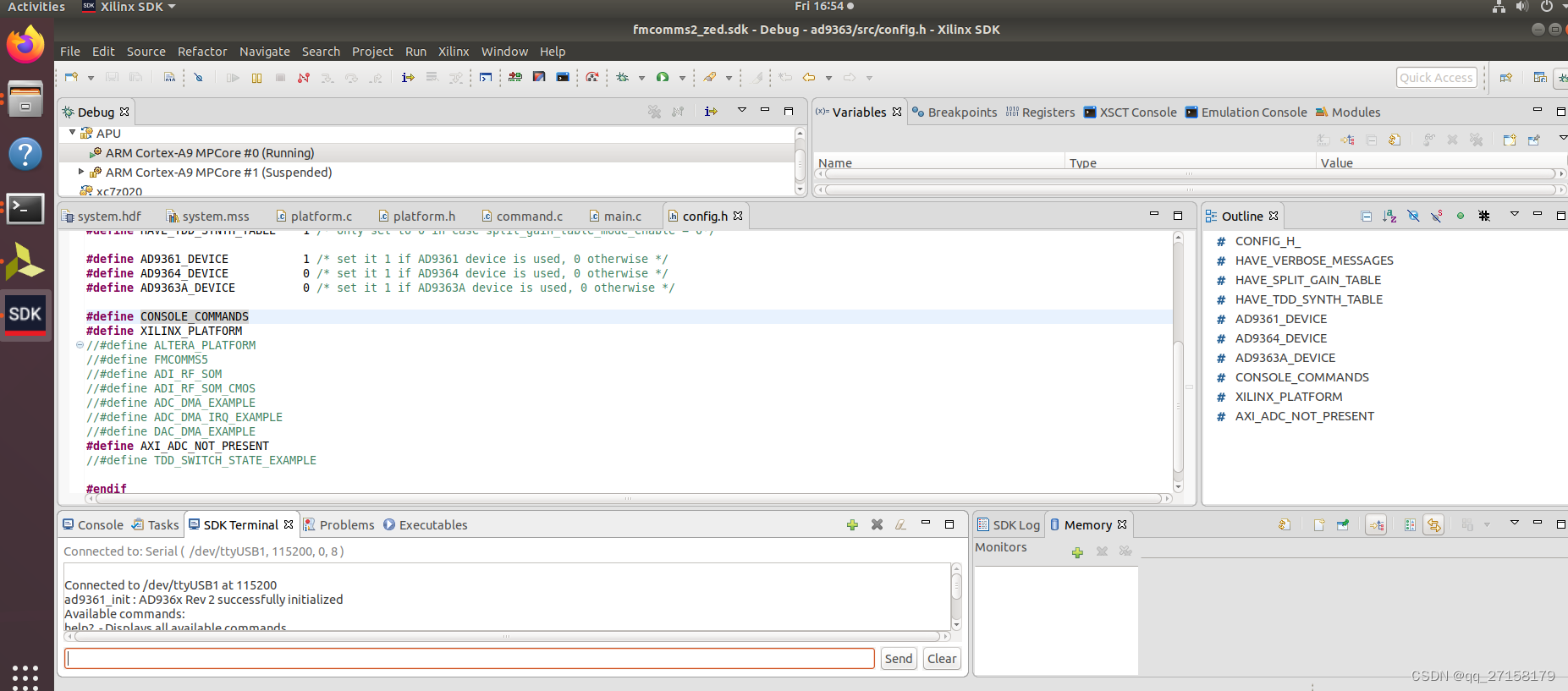

AD9361+zedboard(ZYNQ7020)的SDK工程(上)

1.准备工具 vivado2018.3 HDL源码:https://wiki.analog.com/resources/fpga/docs/releases no_os:https://github.com/analogdevicesinc/no-OS 注意:HDL源码下载的版本要与vivado一致,我这里是2018.3 HDL版本选择 2.构建vivado工程 2.1编译源文件 解压下载

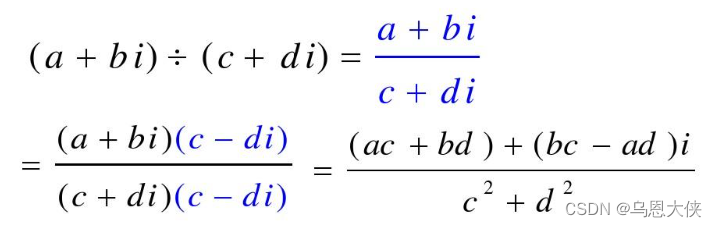

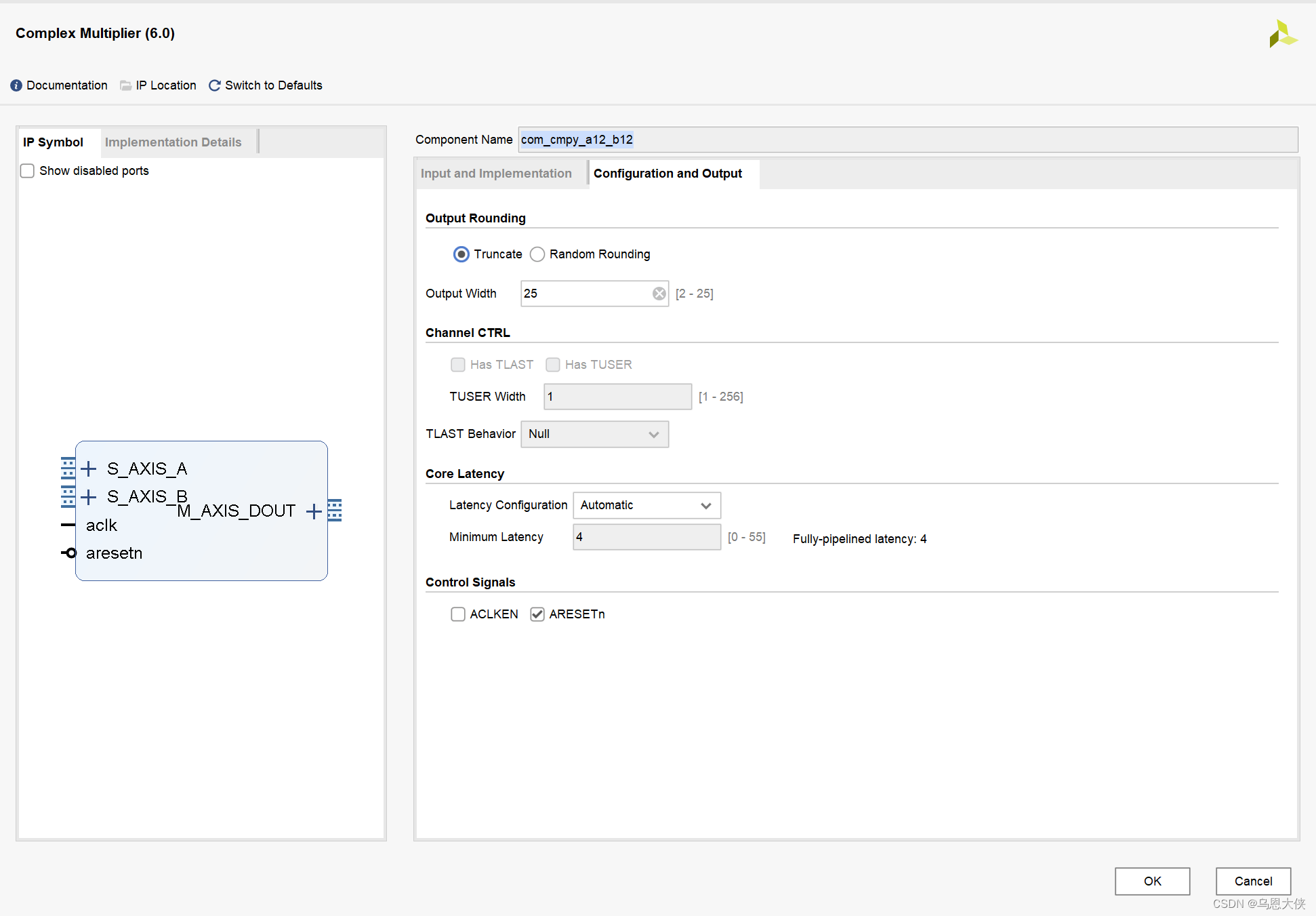

【基带开发】AD9361 复乘 com_cmpy_a12_b12

IP核 tb_com module tb_com();reg ad9361_l_clk,rst; initial beginad9361_l_clk=0;forever #4.545 ad9361_l_clk=~ad9361_l_clk;endinitial beginrst=1;#9.09 rst=0;endwire [63 : 0] m_fll_phase_shift_d

AD9361 数据数字接口说明

一、简要 AD9361和BBP之间的数据接口以两种模式之一工作:标准CMOS兼容模式或低压差分信号(LVDS)兼容模式。本篇文章将简要介绍一下CMOS和LVDS工作模式下的数据具体的传输样式。 二、CMOS 工作模式 P0_D[11:0] and P1_D[11:0]: 端口0(P0)和端口1(P1)都有一个12位并行数据总线(D[11:0]),可在BB

AD9361 数据数字接口说明

一、简要 AD9361和BBP之间的数据接口以两种模式之一工作:标准CMOS兼容模式或低压差分信号(LVDS)兼容模式。本篇文章将简要介绍一下CMOS和LVDS工作模式下的数据具体的传输样式。 二、CMOS 工作模式 P0_D[11:0] and P1_D[11:0]: 端口0(P0)和端口1(P1)都有一个12位并行数据总线(D[11:0]),可在BB

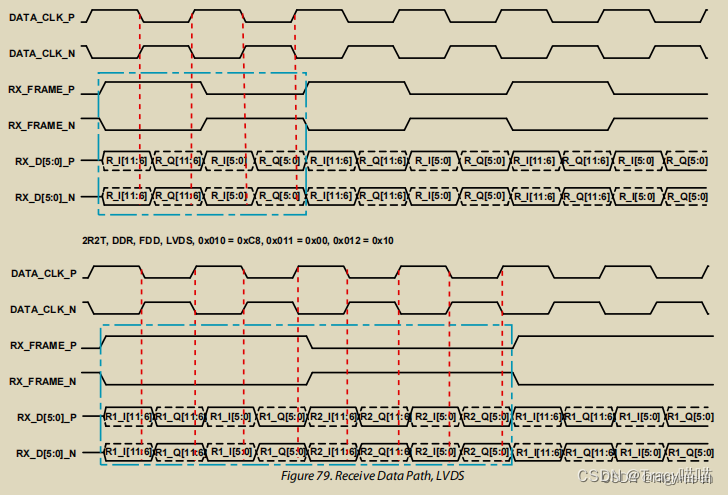

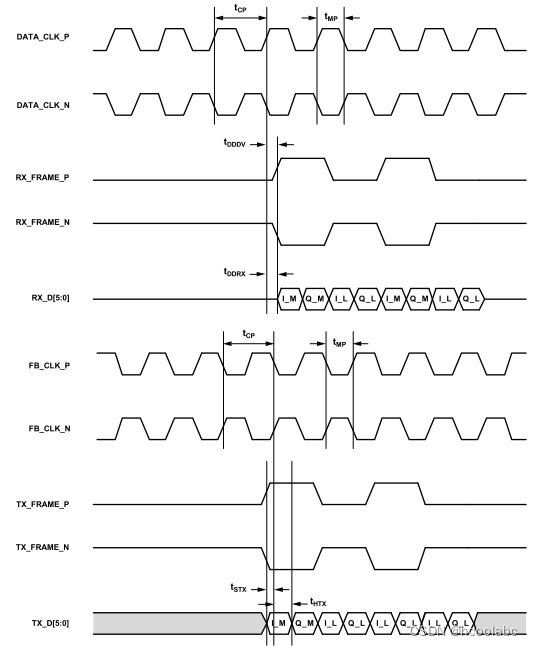

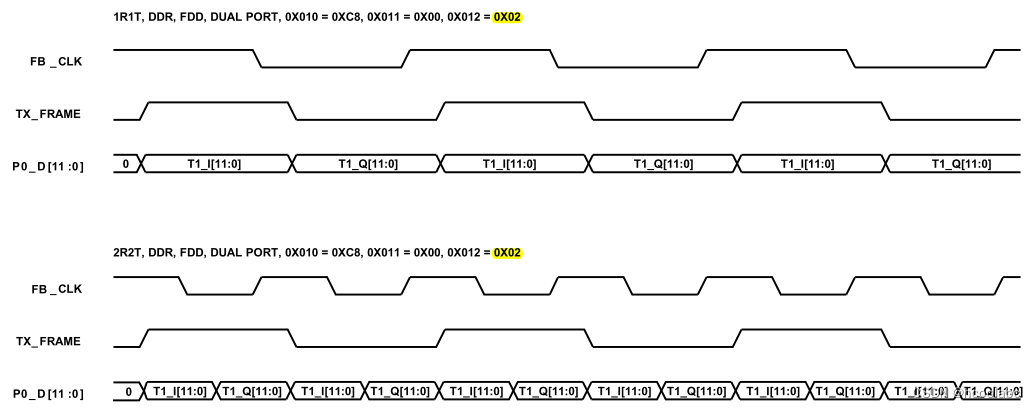

【AD9361 数字接口CMOS LVDSSPI】C 并行数据 LVDS

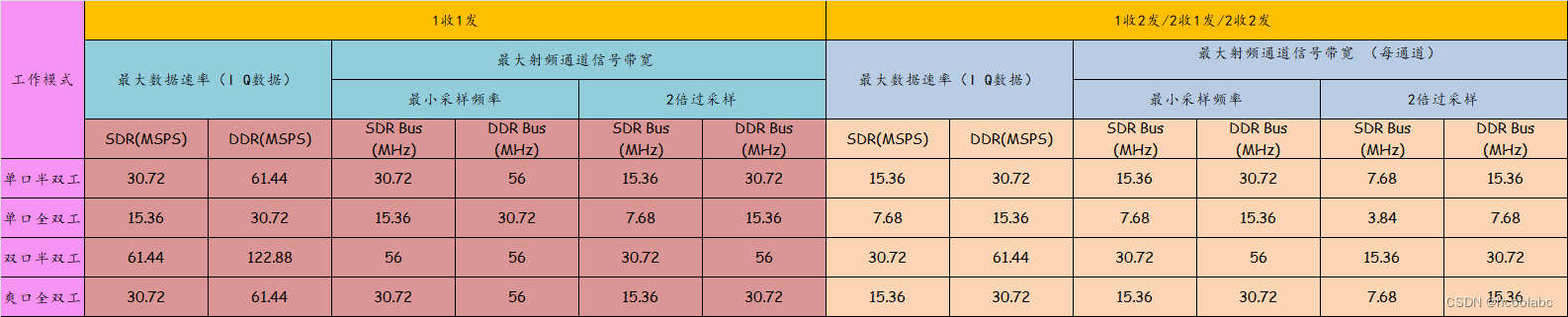

接上一部分,AD9361 数字接口CMOS &LVDS&SPI 目录 一、LVDS模式数据路径和时钟信号LVDS模式数据通路信号[1] DATA_CLK[2] FB_CLK[3] Rx_FRAME[4] Rx_D[5:0][5] Tx_FRAME[6]Tx_D[5:0][7] ENABLE[8] TXNRX系列 二、LVDS最大时钟速率和信号带宽 一、LVDS模式数据路径和时钟信号

【AD9361 数字接口CMOS LVDSSPI】C 并行数据 LVDS <续>

续【AD9361 数字接口CMOS &LVDS&SPI】C 并行数据之LVDS 不同于CMOS的传输方式,lvds只能工作在双端口全双工模式下。 一、 双端口全双工模式 (LVDS)代称 DFL DUAL PORT FULL DUPLEX MODE DFL 模式通过写入SPI寄存器实现。在此模式下,P0 和 P1 均作为 LVDS 信号使能,数据总线 (D[11:0]) 被拆分为单独的子总线

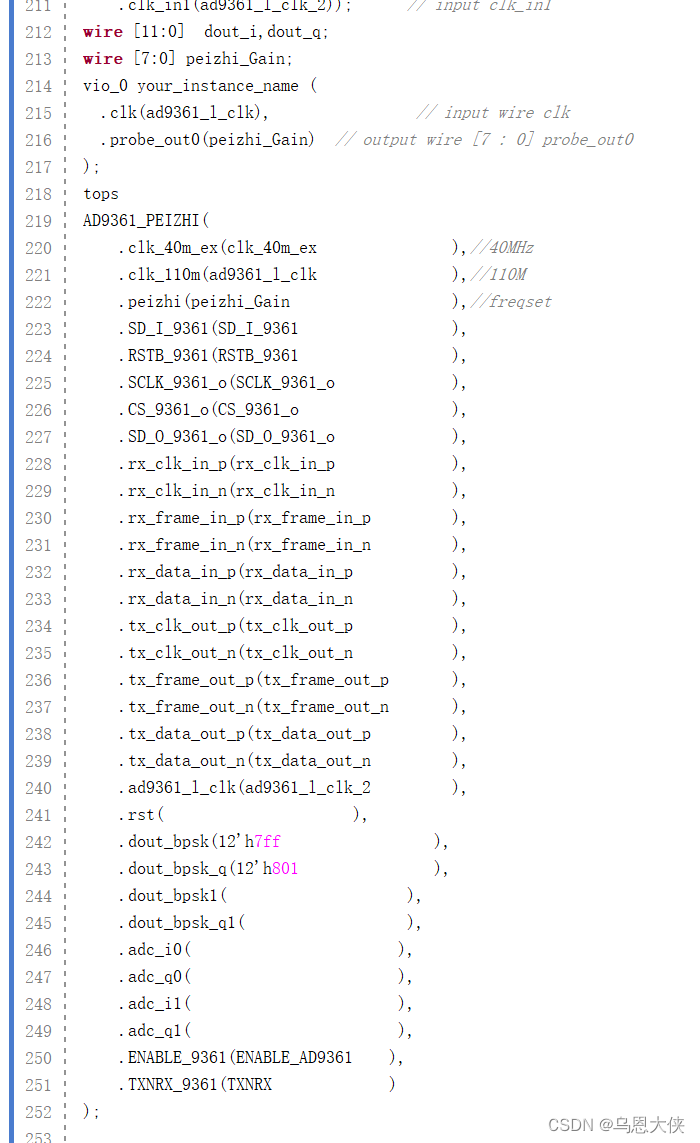

write_edif 生成 AD9361 配置的自定义IP核

将AD9361配置文件设置为顶层 设置里; -mode out_of_context 替换文字 综合 导出 IP 核 write_edif -security_mode all D:/tops.edf D:/tops.edf write_verilog -mode synth_stub D:/tops_stub.v D:/tops_stub.v 调用 AD9

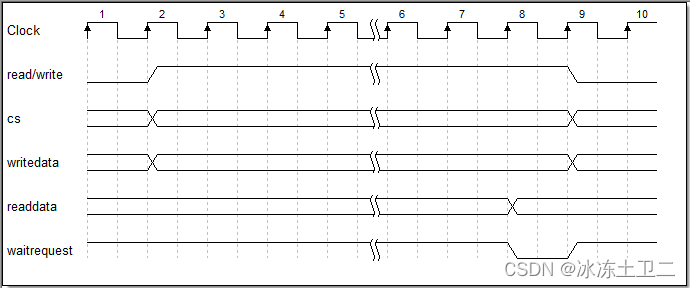

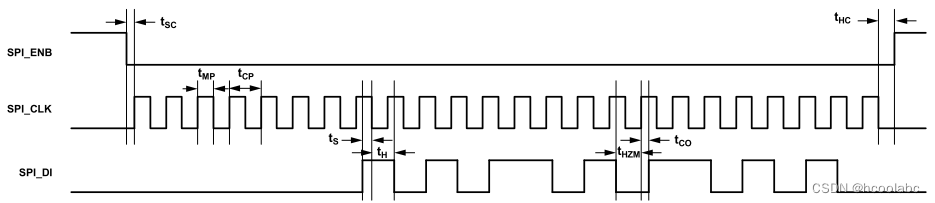

【AD9361 数字接口CMOS LVDSSPI】D 串行数据 SPI

【AD9361 数字接口CMOS &LVDS&SPI】D部分 接续 【AD9361 数字接口CMOS &LVDS&SPI】A 并行数据CMOS 串行外设接口(SPI) SPI总线为AD9361的所有数字控制提供机制。每个SPI寄存器的宽度为8位,每个寄存器包含控制位、状态监视器或其他控制器件所有功能的设置。以下介绍此接口的细节。 SPI功能层 可以通过在SPI配置寄存器中设置位值来配置SP

【AD9361 数字接口CMOS LVDSSPI】A 并行数据之CMOS

〇、综述 本章介绍并行数据端口(P0_D P1_D)和串行外设接口(SPI),用于在AD9361和BBP之间传输数据和控制/状态信息。 下图显示了这些接口,并提供了AD9361和BBP在宽带无线系统中的使用方式的高级视图。数据接口工作在两种模式之一:标准CMOS兼容模式或低压差分信号(LVDS)兼容模式。每个接口都具有以下各节中所述的独特特征。 使用 CMOS 模式时 • 保持单端CMOS

【AD9361 数字接口CMOS LVDSSPI】B 并行数据之CMOS

##接上一篇; 本节介绍 AD9361 数字接口CMOS &LVDS&SPI最后一张表中四种工作模式的具体配置及时序波形图。 目录 1、单端口半双工模式 (CMOS) *代称 SHC*换句话说,最大值是12‘b0111_1111_1111,即0x7FF,最小值的数字量是12‘b0111_1111_1111,即 0x800。这里提个问题,byte的范围是 -127~127 ? 还是 -128

AD9361射频捷变收发器系列推荐

文章目录 AD9361射频捷变收发器系列推荐AD9361优势与特点产品详情应用 ADRV9010优势与特点产品详情应用 AD9361射频捷变收发器系列推荐 AD9361 图 1 AD9361结构框图 优势与特点 集成12位DAC和ADC的RF 2 × 2收发器TX频段:47 MHz至6.0 GHzRX频段:70 MHz至6.0 GHz支持TDD和FD

【USRP】报错:Error: RuntimeError: [ad9361_device_t] BBPLL not locked

这个错误发生得源码位于:ad9361_device.cpp /************************************************************************ Calibration functions***********************************************************************//*

![【USRP】报错:Error: RuntimeError: [ad9361_device_t] BBPLL not locked](/front/images/it_default.jpg)