本文主要是介绍【基带开发】AD9361 复乘 com_cmpy_a12_b12,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

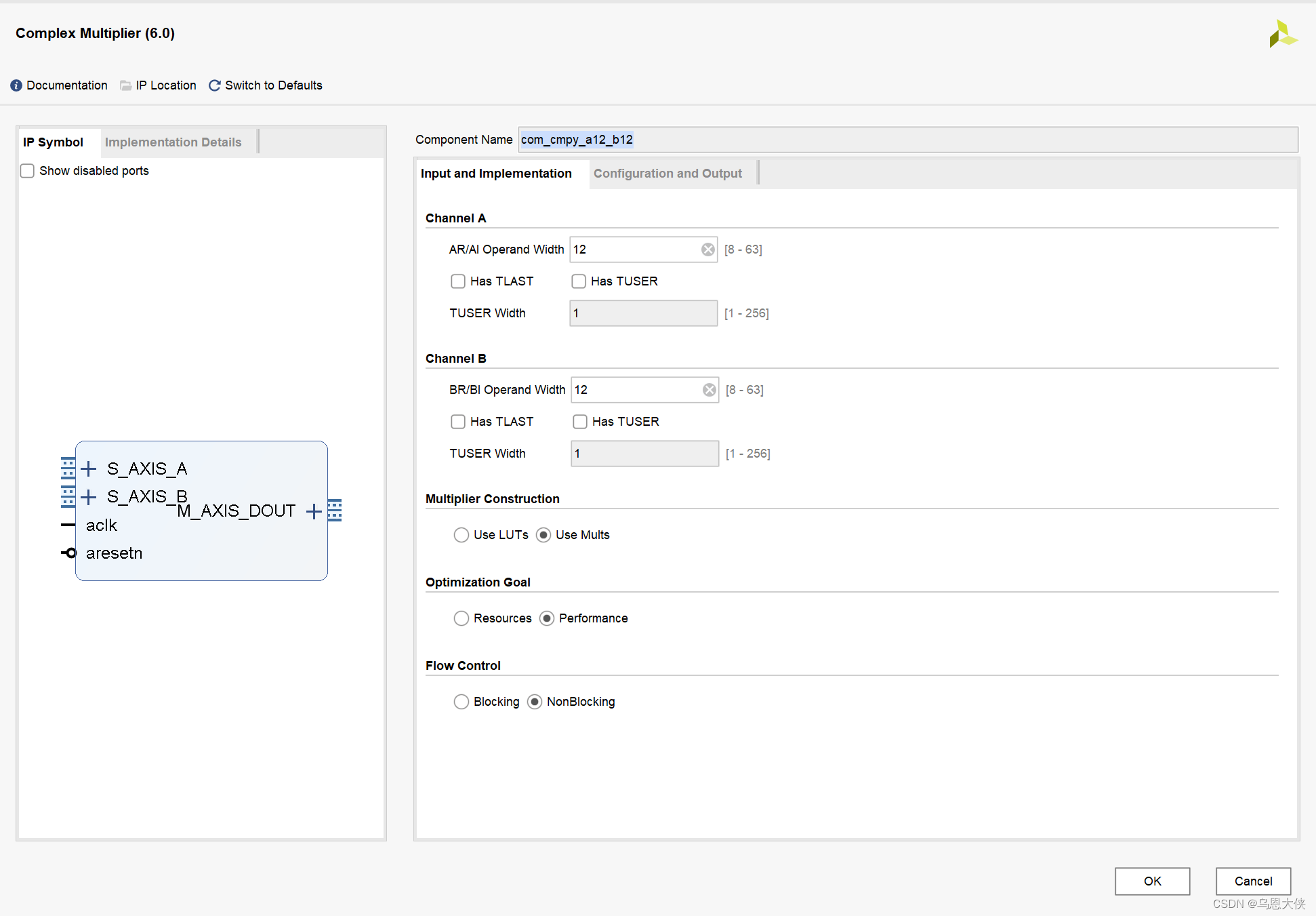

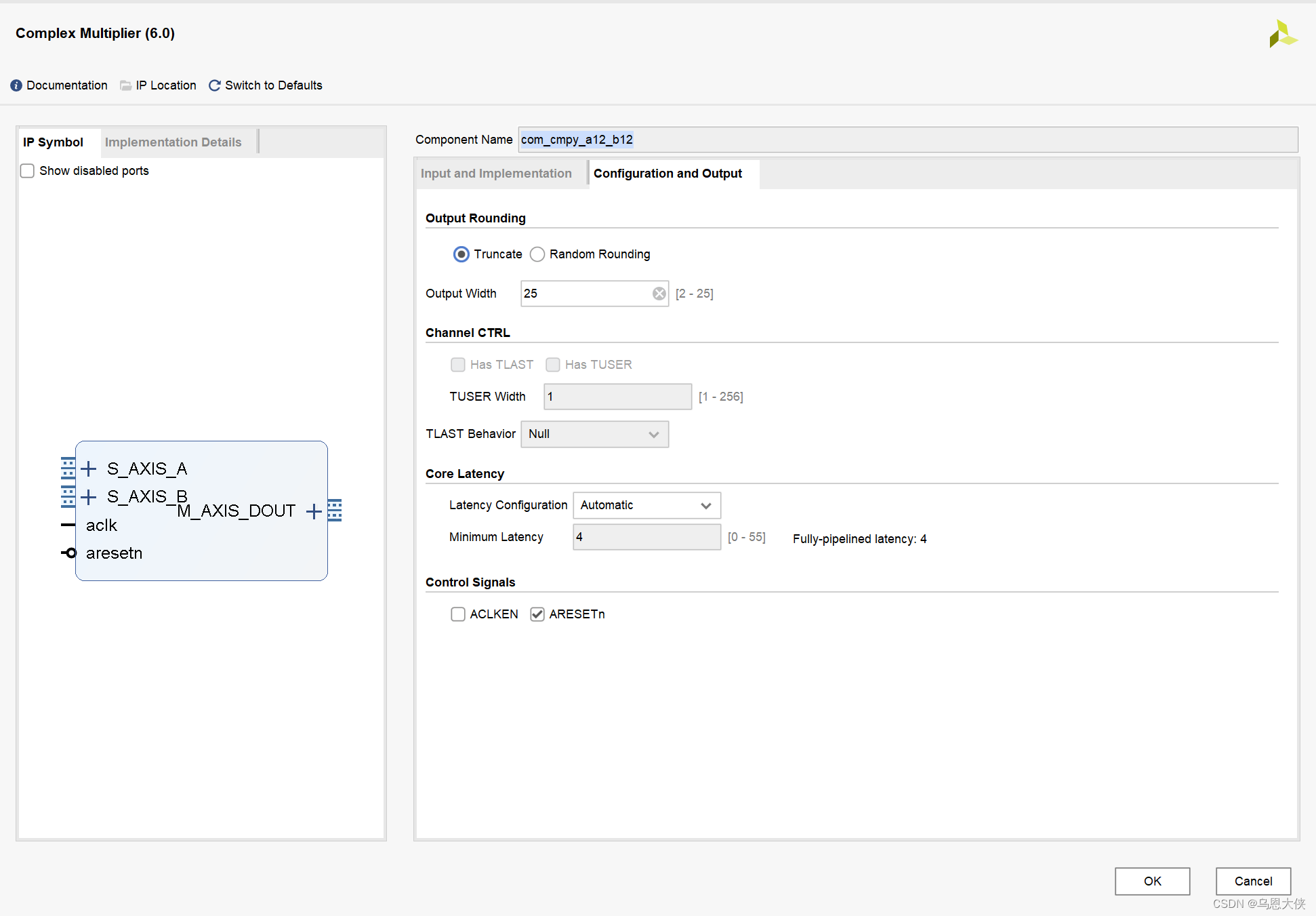

IP核

tb_com

module tb_com();reg ad9361_l_clk,rst; initial beginad9361_l_clk=0;forever #4.545 ad9361_l_clk=~ad9361_l_clk;

end

initial beginrst=1;#9.09 rst=0;

end

wire [63 : 0] m_fll_phase_shift_dout; // fll 输出 dout

// FLL Phase Shift

com_cmpy_a12_b12 FLL_Phase_Shift (.aclk(ad9361_l_clk), // input wire aclk.aresetn(~rst), // input wire aresetn.s_axis_a_tvalid(1'b1), // input wire s_axis_a_tvalid.s_axis_a_tdata({4'd0,12'h400,4'd0,12'h400}), // input wire [31 : 0] s_axis_a_tdata from data rate convert Q0.11 [27:16] [11:0].s_axis_b_tvalid(1'b1), // input wire s_axis_b_tvalid .s_axis_b_tdata({4'd0,12'h400,4'd0,12'h400}), // input wire [31 : 0] s_axis_b_tdata Q0.11 [27:16] [11:0].m_axis_dout_tvalid( ), // output wire m_axis_dout_tvalid.m_axis_dout_tdata(m_fll_phase_shift_dout) // output wire [63 : 0] m_axis_dout_tdata Q2.22 [56:32] [24:0]

);reg [24:0] dout_i,dout_q;

always @ (posedge ad9361_l_clk or posedge rst)

beginif(rst)begindout_i <= 25'd0;dout_q <= 25'd0;endelsebegindout_i <= m_fll_phase_shift_dout[24:0];dout_q <= m_fll_phase_shift_dout[56:32];end

endendmodule

这篇关于【基带开发】AD9361 复乘 com_cmpy_a12_b12的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!