本文主要是介绍【基带开发】AD9361 生成1到223的递增数据,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/06/29 17:50:56

// Design Name:

// Module Name: gen_Incremental_223

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module gen_Incremental_223(clk,rst,dout,dout_clk_p,dout_en

);input clk,rst;output [7:0] dout;output dout_clk_p;output dout_en;wire start;clk_file

#(.FREQUENCY_CLK(32'd195 )) //5hz

CLK_GENS(.clk(clk ),.rst(rst ),.clk_gens1( ),.clk_gens1_p(start )

);reg [15:0] cnts;

always @ (posedge clk or posedge rst)

beginif(rst)begincnts <= 16'hffff;endelse if (start)begincnts <= 16'd0;endelse if (cnts < 16'd250) begincnts <= cnts + 1'b1;endelsebegincnts <= cnts;end

endreg [7:0] dout;

always @ (posedge clk or posedge rst)

beginif(rst)begindout <= 8'd0;endelse if (start)begindout <= 8'd0;endelse if (cnts < 16'd224) begindout <= dout + 1'b1;endelsebegindout <= dout;end

endreg dout_clk_p;

always @ (posedge clk or posedge rst)

beginif(rst)begindout_clk_p <= 1'b0;endelse if (start)begindout_clk_p <= 1'b0;endelse if (cnts < 16'd1)begindout_clk_p <= 1'b1;endelsebegindout_clk_p <= 1'b0;end

endreg dout_en;

always @ (posedge clk or posedge rst)

beginif(rst)begindout_en <= 1'b0;endelse if (start)begindout_en <= 1'b0;endelse if (cnts < 16'd223)begindout_en <= 1'b1;endelsebegindout_en <= 1'b0;end

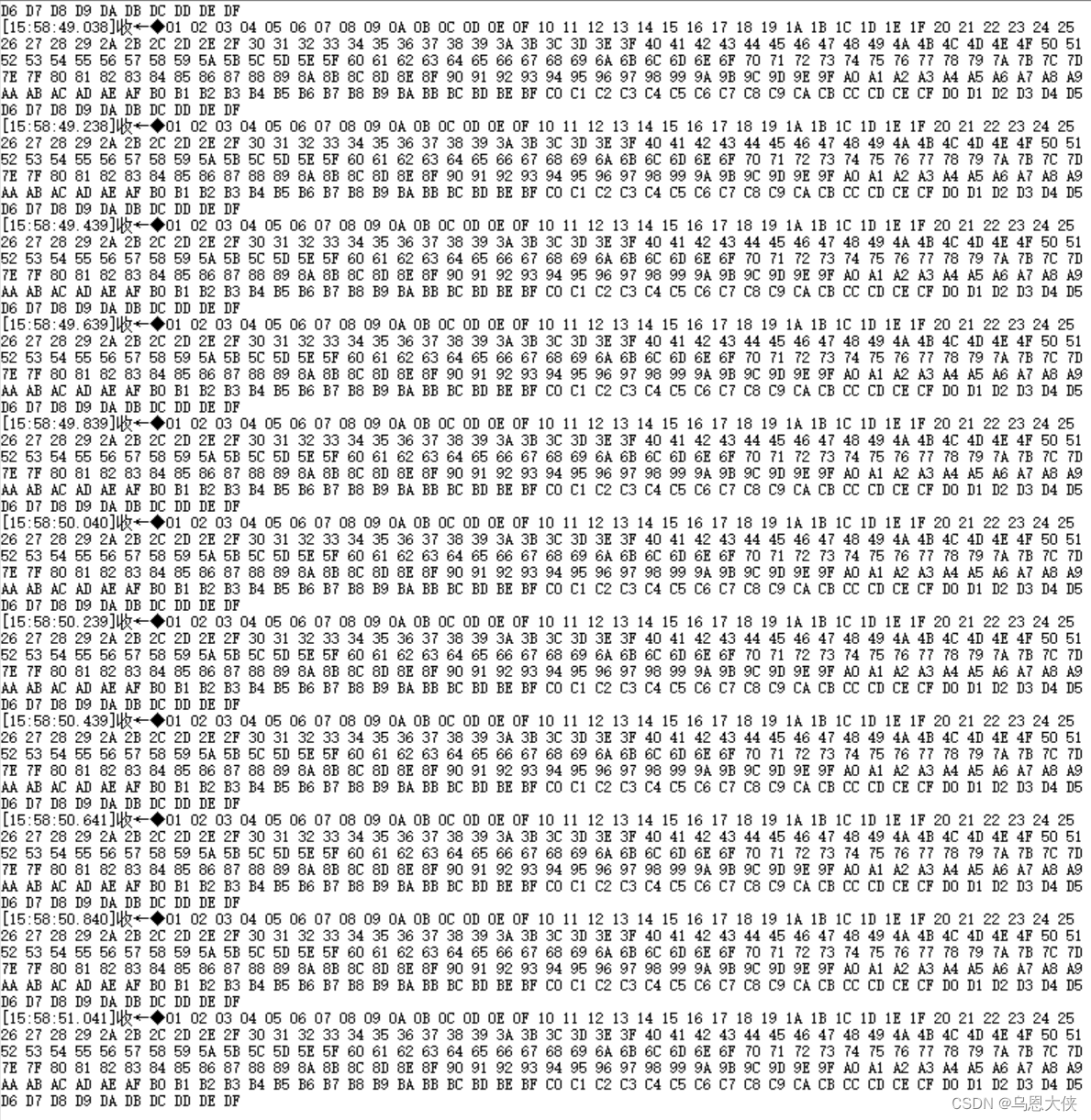

endendmodule结果

这篇关于【基带开发】AD9361 生成1到223的递增数据的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!