zynq7020专题

复旦微FMQL20SM全国产ARM+FPGA核心板,替代xilinx ZYNQ7020系列

FMQL20SM核心板一款全国产工业核心板。基于复旦微FMQL20S400M四核ARM Cortex-A7(PS端) + FPGA可编程逻辑资源(PL端)异构多核SoC处理器设计的全国产工业核心板,PS端主频高达1GHz。 核心板简介 FMQL20SM核心板是一款全国产工业核心板。基于复旦微FMQL20S400M四核ARM Cortex-A7(PS端) + FPGA可编程逻辑资源(PL

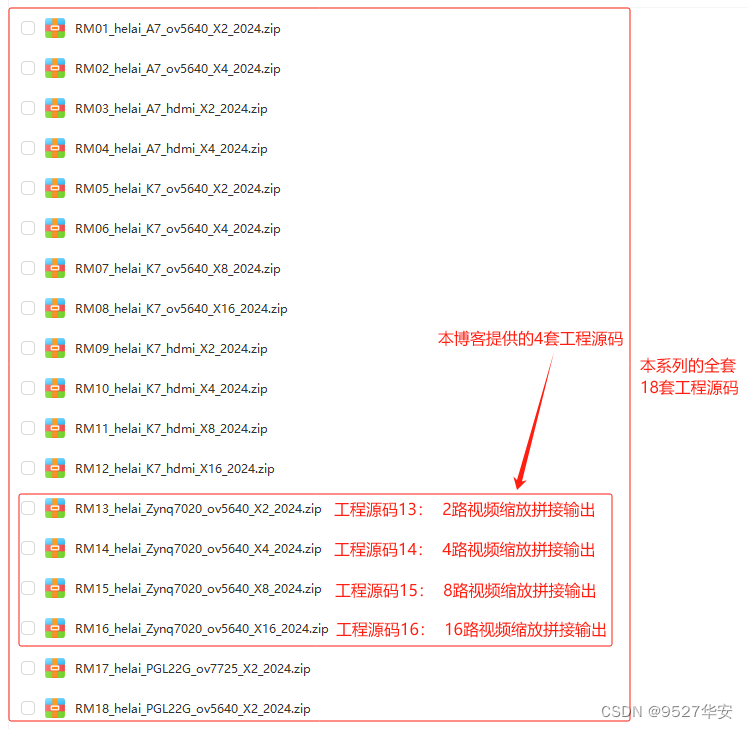

FPGA高端项目:Xilinx Zynq7020系列FPGA 多路视频缩放拼接 工程解决方案 提供4套工程源码+技术支持

目录 1、前言版本更新说明给读者的一封信FPGA就业高端项目培训计划免责声明 2、相关方案推荐我这里已有的FPGA图像缩放方案我已有的FPGA视频拼接叠加融合方案本方案的Xilinx Kintex7系列FPGA上的ov5640版本本方案的Xilinx Kintex7系列FPGA上的HDMI版本本方案的Xilinx Artix7系列FPGA上的应用 3、设计思路框架设计框图视频源选择ov564

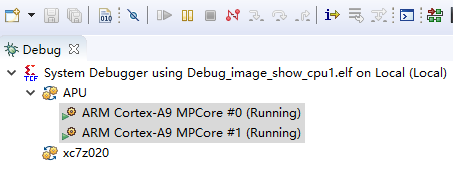

【JokerのZYNQ7020】AMP。

软件环境:vivado 2017.4 硬件平台:XC7Z020 首先吧,说说这篇文章标题AMP是个啥。这个AMP(非对称多处理)是相对于SMP(对称多处理)来说的,耍ZYNQ的朋友们都很清楚,PS这边是个双核A9,而之前的大多数SDK程序,除非特别指定,一般会默认只跑在核0上,而今天这个AMP程序,是核0和核1一起跑,类似于真正的两个进程同时进行,但彼此之间还有软中断相互触发,

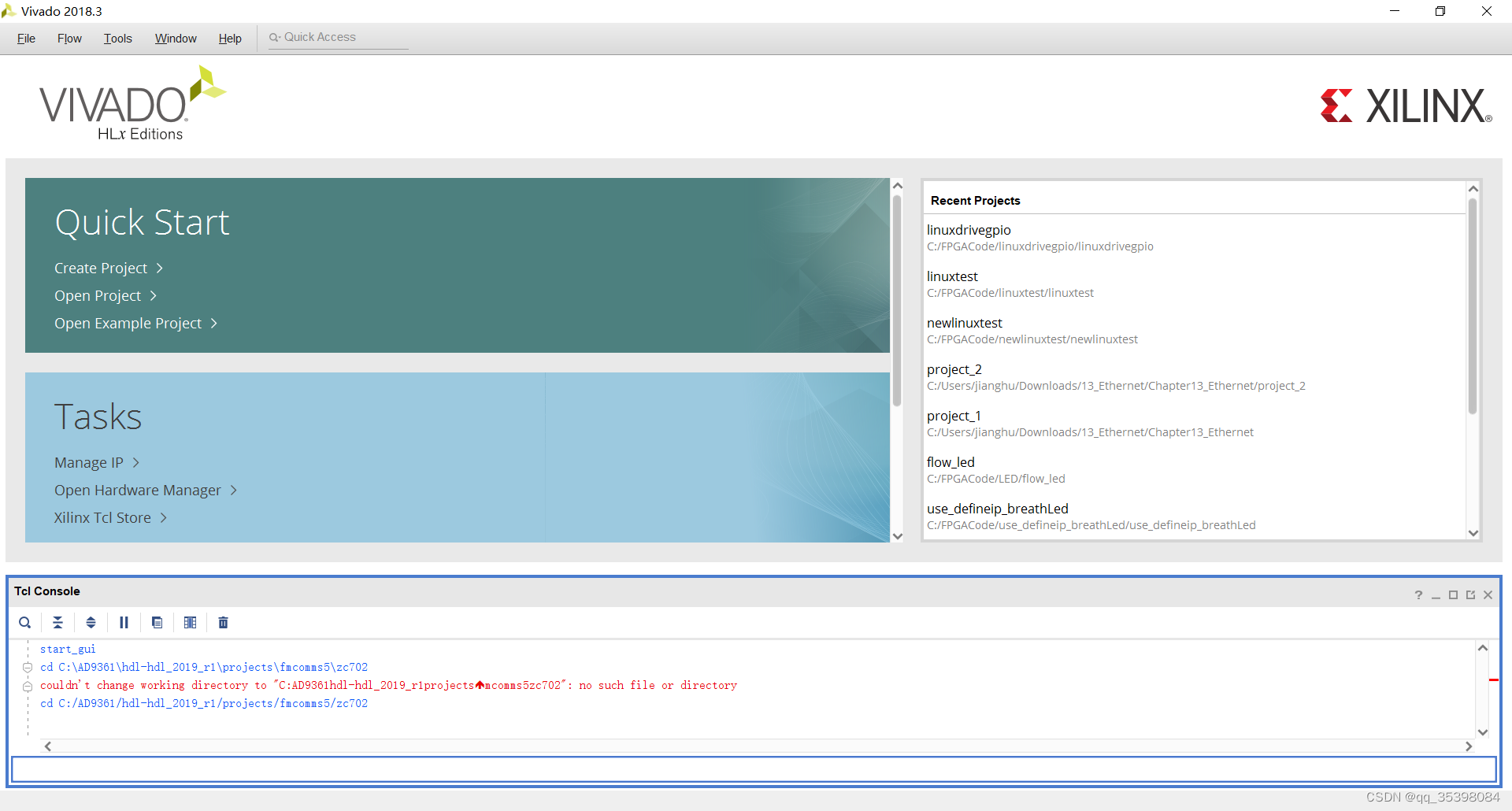

AD9361+zedboard(ZYNQ7020)的SDK工程(上)

1.准备工具 vivado2018.3 HDL源码:https://wiki.analog.com/resources/fpga/docs/releases no_os:https://github.com/analogdevicesinc/no-OS 注意:HDL源码下载的版本要与vivado一致,我这里是2018.3 HDL版本选择 2.构建vivado工程 2.1编译源文件 解压下载

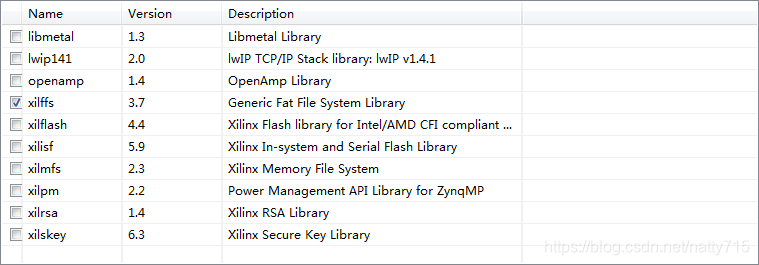

【JokerのZYNQ7020】BMP_SHOW_1080p。

软件环境:vivado 2017.4 硬件平台:XC7Z020 太丢脸了,实在太丢脸了,这篇日期是8月的文章,其实是我在8月的最后一天占了个坑,在9月才陆陆续续补上的,不然每月一更就破例了。出差在外果然是干什么都不方便啊。 本次!那就说说怎样在zynq7020上通过hdmi显示sd卡上的1080p图片。 因为这里只做图片显示输出,所以vdma只配置读通道就行。 接

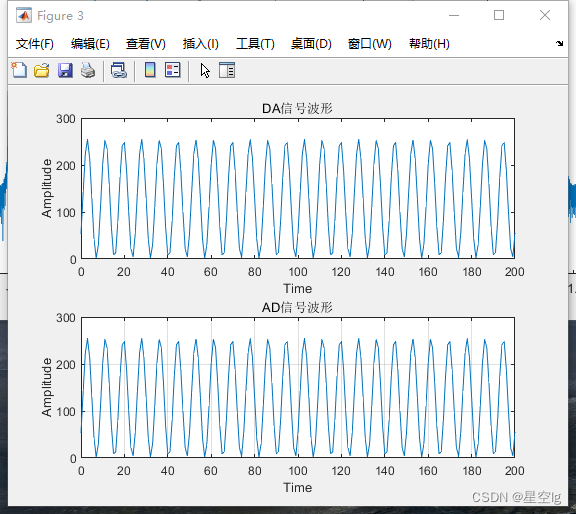

ZYNQ学习笔记(一):基于ZYNQ7020、AN108的DDS实验(VIO可控频率字)

目录 一、设计需求、 二、DDS 基本原理、 三、Vivado工程建立、 四、添加设计源文件、模块例化、 3.1 添加设计源文件 3.2 模块例化 五、程序设计、 六、分析与综合、约束输入、 6.1 分析与综合过程 6.2 约束输入 七、连接测试、 八、数据导出与matlab分析、 九、实验改进、 9.1、模块例化 9.2、程序改进 9.3、约束输入 9.4、连接测试 总结、 实验

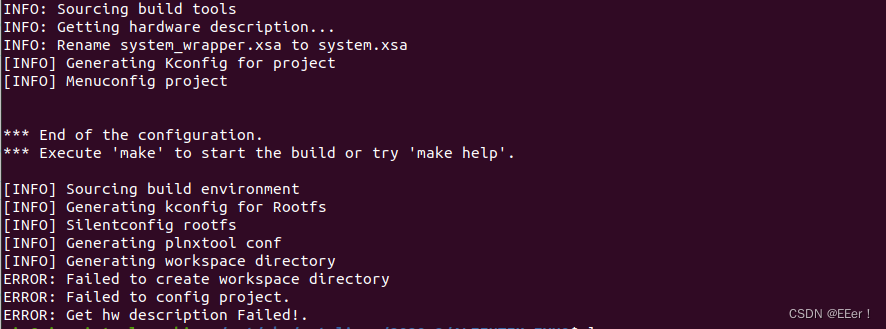

ZYNQ7020开发(二):zynq linux系统编译

文章目录 一、编译前准备二、SDK编译三、编译步骤总结四、问题汇总 一、编译前准备 1.设置环境变量 source /opt/pkg/petalinux/2020.2/settings.sh /opt/pkg/petalinux/2020.2是上一节petalinux的安装目录 2.创建 petalinux 工程 进入petalinux安装目录(例如:/opt/pkg/