本文主要是介绍DCT/DCG综合后,带边界优化网表的ECO方法介绍,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Conformal ECO对DC Topo模式的边界优化网表表现很差劲。它会在DCT/DCG网表里增加很多不需要的逻辑门。

Synopsys的Design Compiler的DCT和DCG模式为了floorplan、绕线和时序优化了网表,这使得功能ECO变得困难很多。在综合过程中,子模块的边界上增加了克隆端口或者反相端口,还有寄存器的合并。

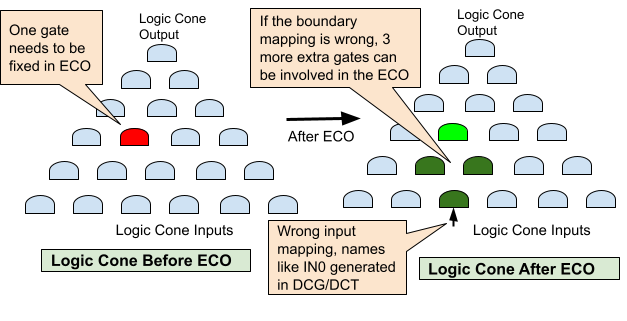

Conformal ECO在功能ECO时会做出错误的映射。如下图1,Conformal ECO对克隆端口映射错了,导致增加了超过正常三倍的逻辑门。

图1:边界映射影响ECO的质量

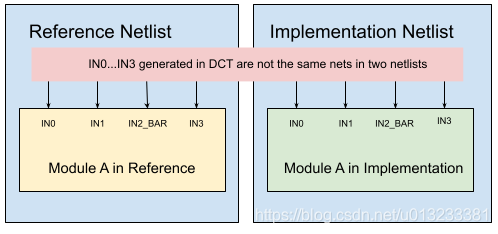

综合工具增加的克隆端口,与APR的实现网表里的并不是一一对应的。当ECO工具强制让这些端口相等,则ECO补丁会包含冗余的逻辑门,甚至使得最终逻辑不等价。

图2:DCT/DCG边界优化网表

GOF会合理的分析和映射克隆端口,只精确地修改真正不等价的点。

图3:GOF的ECO结果,只有红色的点被修改了。

这篇关于DCT/DCG综合后,带边界优化网表的ECO方法介绍的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!