网表专题

06:网表更新到PCB

1.先了解HDMI设计规范 有4对差分线,1对IIC串行总线信号从芯片---->防静电器件—>HDMI输出 发现错误,没有SDA网络,检查原理图 重新导网表 3.完成信号芯片—>防静电模块—>HDMI布局

【魔方网表】魔方网表涉及到的公式整理

1、取当前日期的年月作为流水号的前缀,例如20200625取202006 YEAR(NOW())&TEXT(MONTH(NOW()),“00”) 2、取当前登录的操作员名称:mfuser() 3、取当前登录系统日期:today()

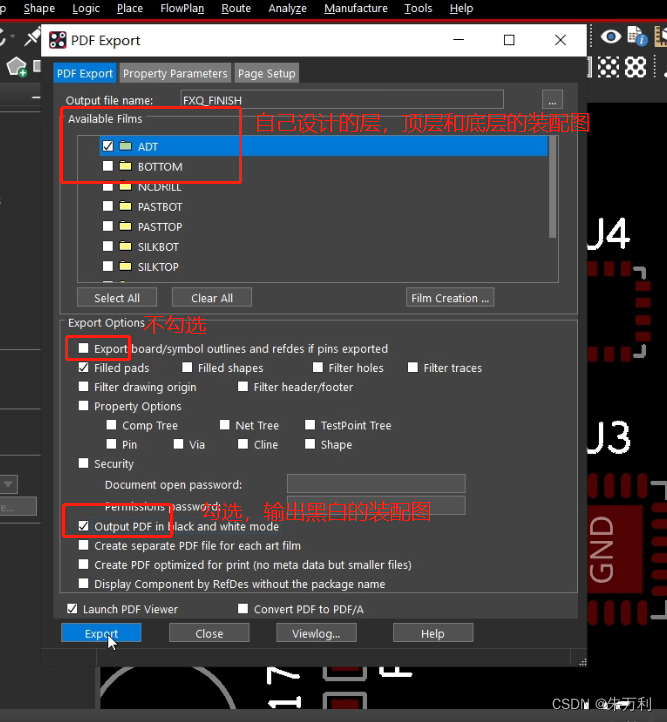

Allegro光绘Gerber文件、IPC网表、坐标文件、装配PDF文件导出打包

Allegro光绘Gerber文件、IPC网表、坐标文件、装配PDF文件导出打包 一、Gerber文件层叠与参数设置二、装配图文件设置导出三、光绘参数设置四、Gerber孔符图、钻孔表及钻孔文件输出五、输出Gerber文件六、输出IPC网表七、导出坐标文件八、文件打包 一、Gerber文件层叠与参数设置 一般要的层叠信息文件如下图所示 那么具体怎么操作呢,请看下文 我们

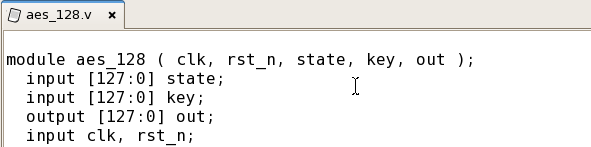

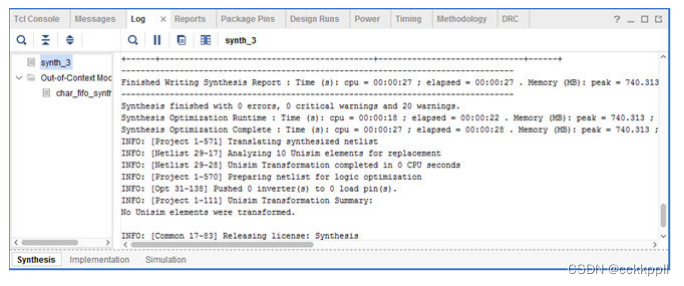

Xilinx(AMD) vivado对FPGA网表文件进行功能仿真的方法

1 概述 在FPGA开发中很多商用IP核出于知识产权保护的目的,不提供源代码,而是提供综合后的FPGA网表。由于没有源代码,也无法对网表文件直接进行仿真的操作来验证功能,此时需要独立的仿真模型文件。 本文介绍在Xilinx(AMD) vivado软件下对FPGA代码综合生成网表、网表的仿真模型,以及使用仿真模型对网表进行仿真的方法。 2 FPGA网表

魔方网表ERP mailupdate.jsp 任意文件上传漏洞复现

0x01 产品简介 魔方网表ERP是一款高效、灵活的企业资源规划解决方案,旨在帮助企业实现数智化转型,消除信息孤岛,打造全程一体化的管理体系。魔方网表ERP拥有强大的表单功能和模块化的产品特点,使得企业可以根据自身业务需求,通过简单的拖拽和配置,快速搭建符合自身特点的复杂业务管理系统。同时,魔方网表ERP能够无缝对接外部系统,打破信息壁垒,实现业务跨部门间并行协作,提高工作效率。 0x02 漏

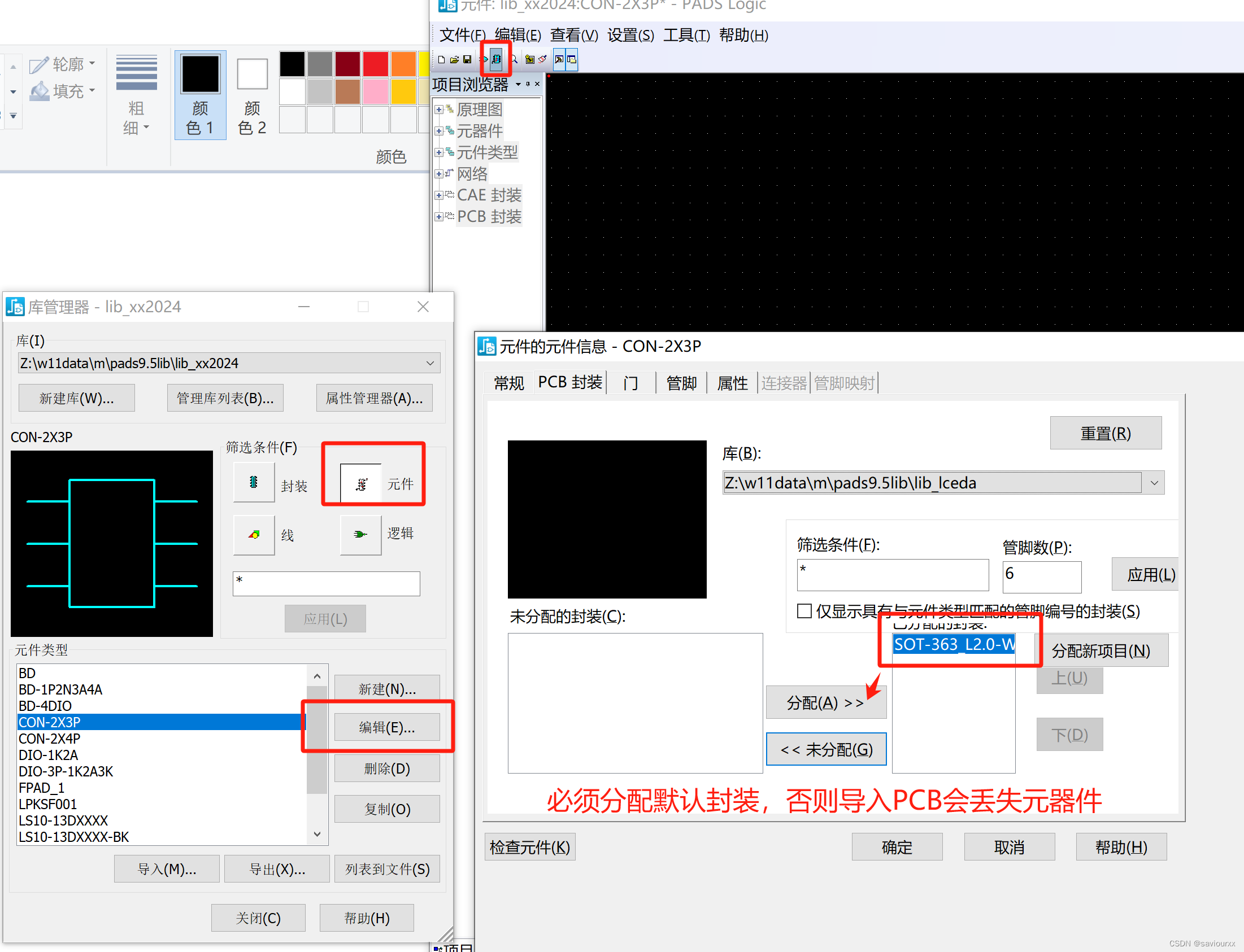

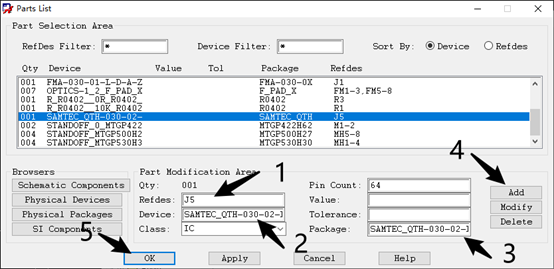

【PADS 原理图Logic发送网表元器件丢失的解决办法】

1、PADS版本:VX1.2 2、PADS Logic原理图导入PCB Layout后,发现总有几个元器件怎么导都不会显示在PADS Layout上,如下图: PADS Logic上也选择了封装,还是不行,如下图: 3、解决办法: 最后找到原因是,库管理器的元件,没有设置默认封装,所以即使在原理图上选了封装也不会导入到PCB中,解决办法如下图: 4、总结: 这么简单

vivado 手动设置自下而上的流量并导入网表、创建较低级别的网表

手动设置自下而上的流量并导入网表 要手动运行自下而上的流,请将较低级别的网表或第三方网表实例化为黑色盒子,Vivado工具在合成完成后将黑盒子融入完整的设计中。这个以下部分描述了该过程。 重要!Vivado合成不合成或优化加密或非加密合成网表;因此,XDC约束或合成属性不会影响导入的合成核心网表。此外,Vivado synthesis不会读取核心网表并修改实例化的组件默认情况下;然而,Viva

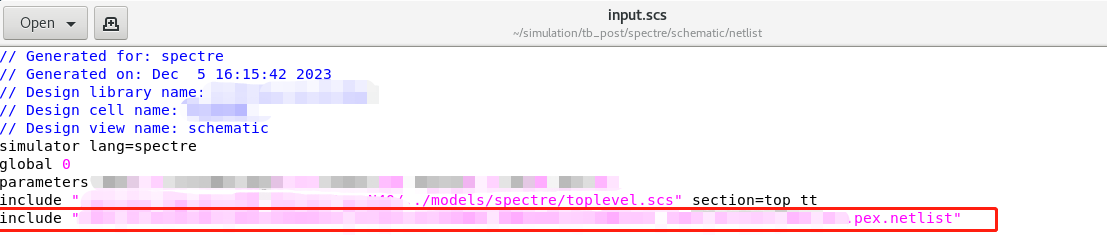

通过修改SPECTRE网表进行后仿

参考:关于修改网表进行Spectre的后仿教程与注意事项 寄生参数提取 首先确保layout能够通过DRC和LVS。 PEX-Outputs-Netlist中,Format选择SPECTRE格式,Use Names From选择SCHEMATIC。SPECTRE格式的NETLIST对大小写不敏感,因此这种方式适合原理图中terminal和pin使用不完全使用大写命名的情况。 PEX-Inp

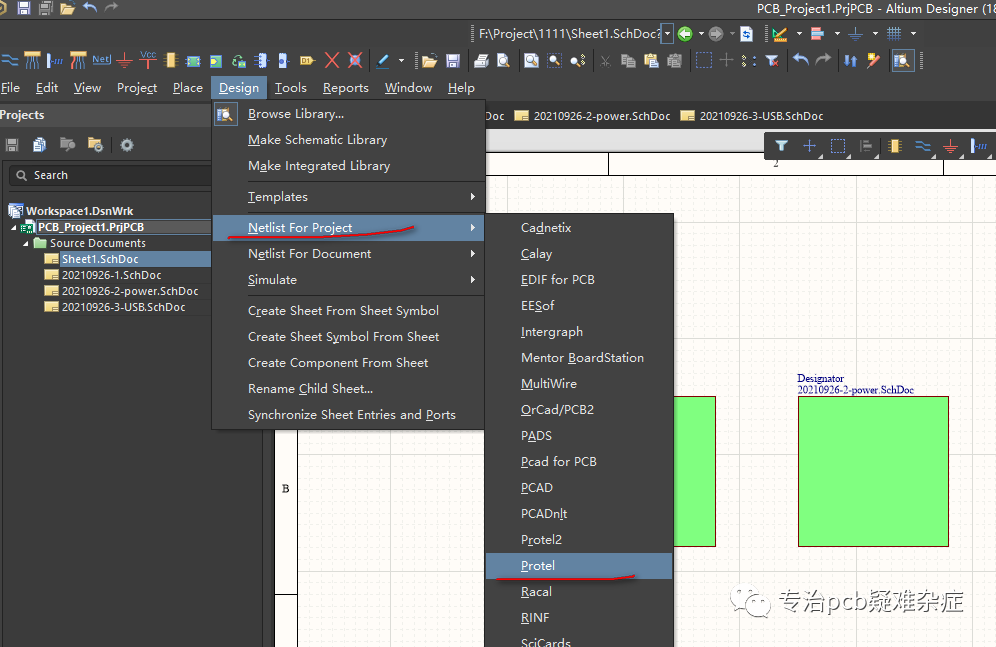

allegro如何导入AD格式的原理图,AD如何产生allegro支持的网表格式 ,AD的原理图可以用allegro进行PCB设计吗

来自群友的疑难杂症(加杨老师V信:PCB206 可入群):allegro如何导入AD格式的原理图,AD如何产生allegro支持的网表格式 AD的原理图可以用allegro进行PCB设计吗? 针对这个疑问:我们的PCB-谢老师这边写篇简单的文章来实现这一操作: 第一种情况:单页AD原理图的处理 第一步:打开AD原理图 直接生成AD格式的网表 直接netlist for document产生p

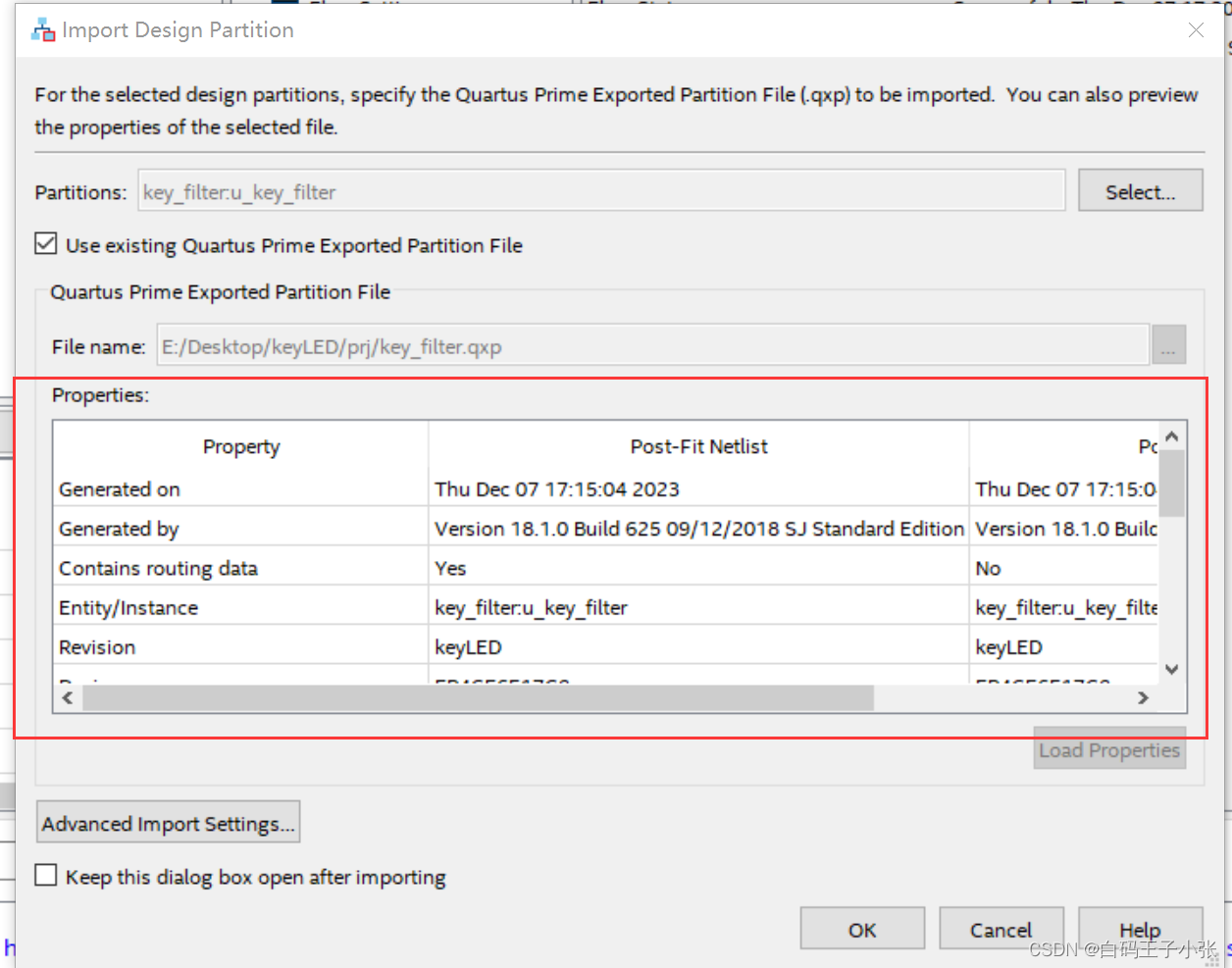

【FPGA】Quartus18.1打包封装网表文件(.qxp)详细教程

当我们在做项目的过程中,编写的底层Verilog代码不想交给甲方时怎么办呢?此时可以将源代码打包封装成网表文件(.qxp)进行加密,并且在工程中进行调用。 Quartus II的.qxp文件为QuartusII Exported Partition,用于创建综合或者PAR之后的网表文件。 一、 .qxp文件打包封装步骤 在QuartusII的Project Navigator中选中欲创建qxp

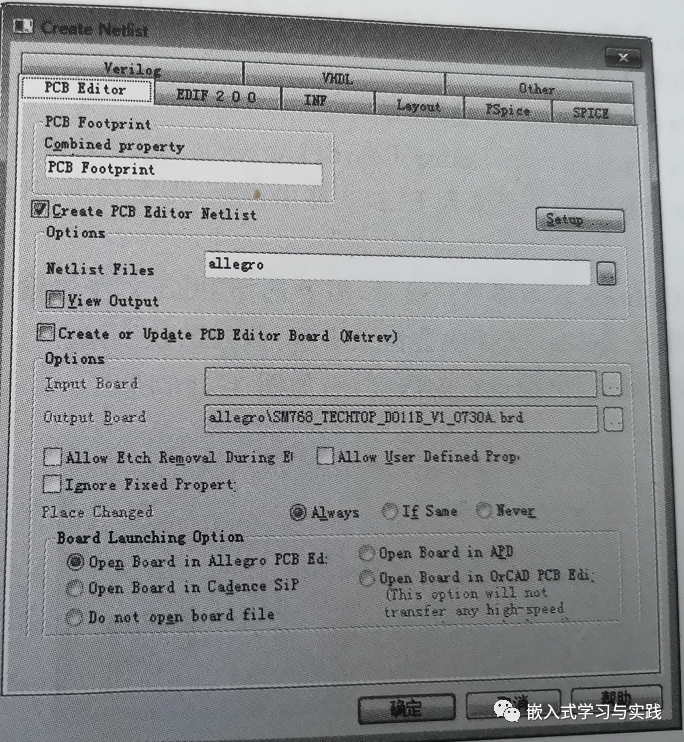

cadence OrCAD原理图输出-Netlist(网表)文件

一、输出前DRC检查 使用orcad设计完原理图,进行网表输出前需要先DRC检查。DRC检查主要是对各种设计Rule的检查,查用的检查如原件的位号是否重复,以及是否有单网络(Single Net)等。 如果有错误,生成网表文件会失败!!! 在项目管理器中,选择dsn文件,在主菜单中选择Tools-Design Rules Check选项,出现Design Rules Check对

cadence allegro中导出网表错误之元器件引脚名错误

文章目录 前言一、解决办法二、其他错误 前言 在用orCAD导出网表的时候,又发现一种错误。导致无法导出网表。 看了错误,结果发现是元器件引脚名有不合法的符号,感叹号!. 一、解决办法 那就再元件库把感叹号删了或者改成其他就行 重点,这个DRC是检查不出来的,服啦。 二、其他错误 其他错误我之前也讲过了,确实,刚学candence,会碰见一大堆问题,AD就没有这

Cadence网表导出常见错误

前言 好不容易绘制出来原理图,结果导出报了很多条错误,由于哥们还是小白,所以很多事情还不懂,有错误的地方希望大佬们能够指出,主要还是以我遇到的为主。 生成网表时候的常见错误 36002-封装名缺失 36003-多part器件属性冲突 36018-原理图中选用的封装是否在所指定的路径中 36022-管脚编号缺失 36032-位号重复 36035-多个相同的引脚连接到不同的网络 36

Cadence Allegro 17.4学习记录开始36-PCB Editor 17.4软件PCB中IPC网表,坐标文件,装配文件输出

目录 Cadence Allegro 17.4学习记录开始36-PCB Editor 17.4软件PCB中IPC网表,坐标文件,装配文件输出一、IPC网表二、坐标文件三、装配文件 Cadence Allegro 17.4学习记录开始36-PCB Editor 17.4软件PCB中IPC网表,坐标文件,装配文件输出 一、IPC网表 步骤; 第一:选择命令 第二:选择参数,导出I

Cadence放置网表以外的器件

在我们设计PCB时,有时需要临时放置一个或多个器件,但是在网表中没有该器件,修改原理图又比较麻烦。下面提供一种方法,软件版本16.6,供参考。如果有好的方法,欢迎留言。 首先设置允许编辑网表,Setup-->User Preferences Editor弹出如图1所示,将logic_edit_enable打勾。 图1 允许编辑网表设置 随后Logic-->Part Logic

Vivado生成网表文件的步骤及方法

软件版本 Vivado 2018.3 估计是在2018 1019系列应该都适用。亲测可用。全部干货。 第①步: 将需要生成网表的模块代码设置为顶层 第②步: 在界面中的Tools -> setting -> synthesis 修改Synthesis Options 其中需要注意的是,Options中将-flatten_hierarchy设为full,意思是模块综合后的层次结构全部

Altium Designer | 5 - 网表导入及模块化布局设计(待续)

导入常见报错解决办法(unknow pin及绿色报错等) 在原理图界面 Ctrl+F搜索元器件位号 在PCB界面,Ctrl+F是左右翻转, 快捷键JC才是搜索元器件位号 报错信息: Unknow pin 1.没有封装 2.封装管脚缺失 3.元件库对应的管脚不对 ... 常见绿色报错的消除 原因:规则问题 先把Rules To Check 的在线和批量 全部都

gds/网表导入virtuoso注意事项

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧?拾陆楼知识星球入口 gds和网表导入到virtuoso中都需要添加参考库,这里需要注意的是如果上层模块/顶层调用下层模块时参考库时,需要把library中的模块cell的单独copy到新的库中,模块的via layout或module schematic和symbol不需要被顶层参考,因为后续更新模块的layout或schematic可

DCT/DCG综合后,带边界优化网表的ECO方法介绍

Conformal ECO对DC Topo模式的边界优化网表表现很差劲。它会在DCT/DCG网表里增加很多不需要的逻辑门。 Synopsys的Design Compiler的DCT和DCG模式为了floorplan、绕线和时序优化了网表,这使得功能ECO变得困难很多。在综合过程中,子模块的边界上增加了克隆端口或者反相端口,还有寄存器的合并。 Conformal ECO在功能ECO时会做出错误的