本文主要是介绍vivado 手动设置自下而上的流量并导入网表、创建较低级别的网表,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

手动设置自下而上的流量并导入网表

要手动运行自下而上的流,请将较低级别的网表或第三方网表实例化为黑色盒子,Vivado工具在合成完成后将黑盒子融入完整的设计中。这个以下部分描述了该过程。

重要!Vivado合成不合成或优化加密或非加密合成网表;因此,XDC约束或合成属性不会影响导入的合成核心网表。此外,Vivado synthesis不会读取核心网表并修改实例化的组件默认情况下;然而,Vivado合成确实合成了安全IP和RTL。约束确实会影响合成后果

创建较低级别的网表

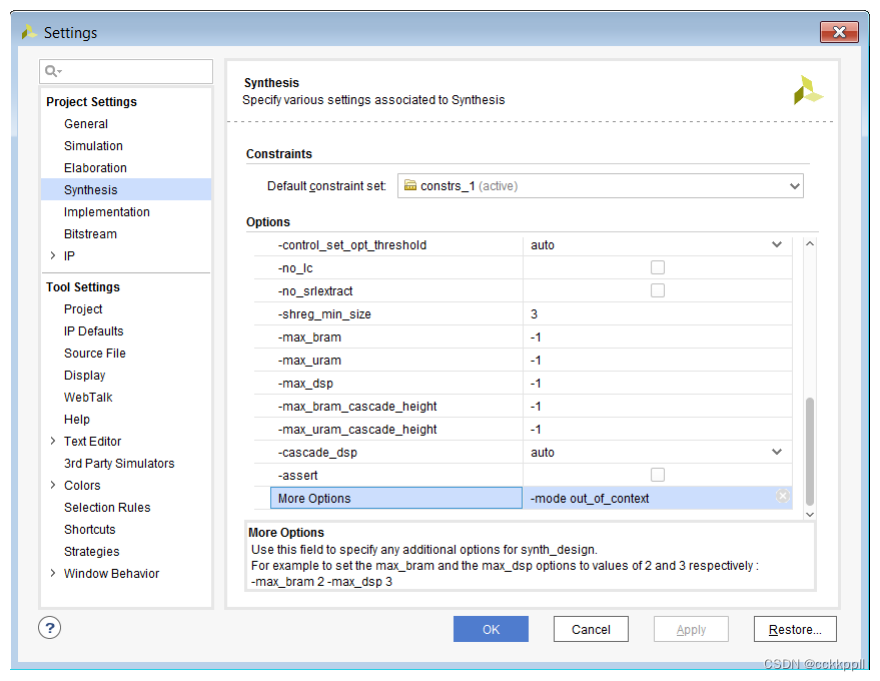

要创建较低级别的网表,请设置一个以该网表作为顶层模块的项目。之前运行合成后,设置上下文外(OOC)模式,如下图所示。

在“更多选项”部分中,可以键入-mode out_of_context以使该工具不在此级别中插入任何I/O缓冲区。运行合成后,打开合成的设计,并在Tcl控制台中键入在Tcl控制台中的write_edif Tcl命令。语法如下:

设计中下级网表的实例化

要使用较低级别的网表或第三方网表运行顶层设计,请实例化通过向Vivado提供较低级别的端口描述,将较低级别设置为黑盒工具在设置自下而上的上下文外流中,这被称为存根文件。重要!提供给Vivado工具的端口名称和网表中的端口名称必须匹配。在VHDL中,用component语句描述端口,如以下代码所示一小条

因为Verilog没有等效的组件,所以使用包装文件进行通信Vivado工具的端口。包装文件看起来像一个典型的Verilog文件,但只包含端口列表,如以下代码片段所示:

将手动自下而上组合在一起组件

创建较低级别的网表并正确实例化顶级网表后,可以在项目模式下,将较低级别的网表添加到Vivado项目中,或者可以使用read_edif或read_verilog命令。在这两种模式中,Vivado工具在合成后合并网表。

注意:如果设计仅来自第三方网表,并且没有其他RTL文件是项目的一部分,可以使用这些网表创建项目,也可以使用read_edif和read_verilog-Tcl命令以及非项目模式下的link_ design Tcl命令。

增量合成

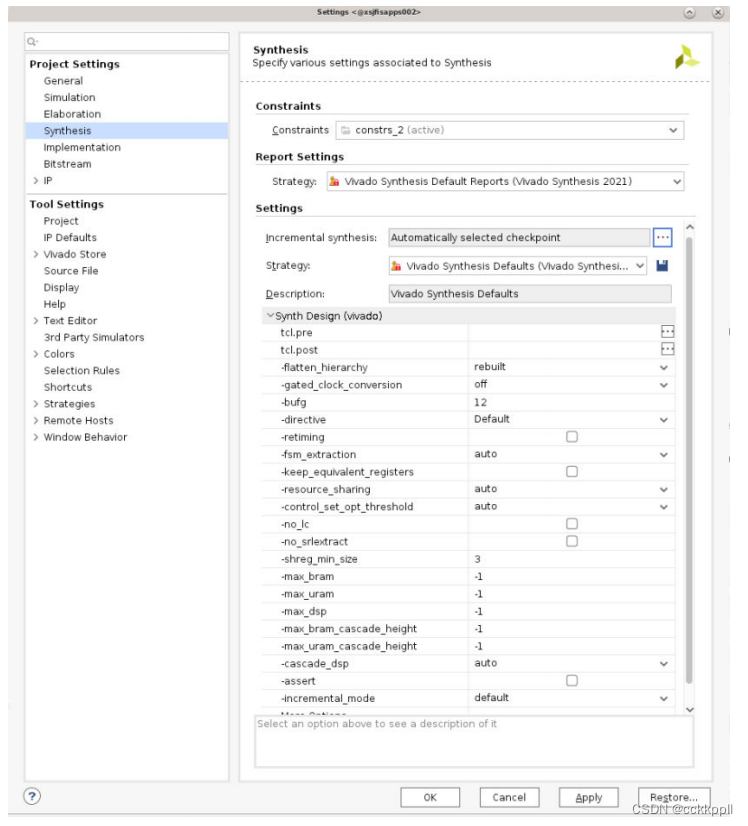

Vivado Synthesis可以增量运行。在这个流程中,该工具将增量合成信息放入生成的DCP文件,可在以后的运行中引用。它检测设计何时具有已更改,并且仅在已更改的设计部分上重新运行合成。关键这种流程的优点是,对于更改较小的设计,运行时间显著减少。此外,当RTL中插入小的变化时,设计的QoR波动较小。在项目模式下建立增量综合可以在“设置”对话框的“合成”页面中使用项目设置“增量合成”盒

请注意以下重要设置:

•增量合成选择框:使用浏览按钮指示增量合成使用已知的检查点、创建的最后一个检查点(默认值),或者如果是增量的合成被禁用。

•incremental_mode Synth Design选项:描述与跨分区优化。这些值有快速、默认、激进和关闭。快速关闭大多数优化,积极地打开更多,并对某些重复合成部分。Off告诉合成不要使用DCP中的增量合成信息文件

在非项目模式下使用增量综合

在项目模式下,该工具会自动读取合成时的最后一个DCP文件最后一次运行(如果在默认模式或特别提到的任何DCP下运行)。在非项目中模式下,合成前必须读取参考DCP。其命令是:

之后,正常运行synth_design命令。

注意:read_checkpoint中的-auto_incremental选项与中的默认行为相同石斑鱼类。

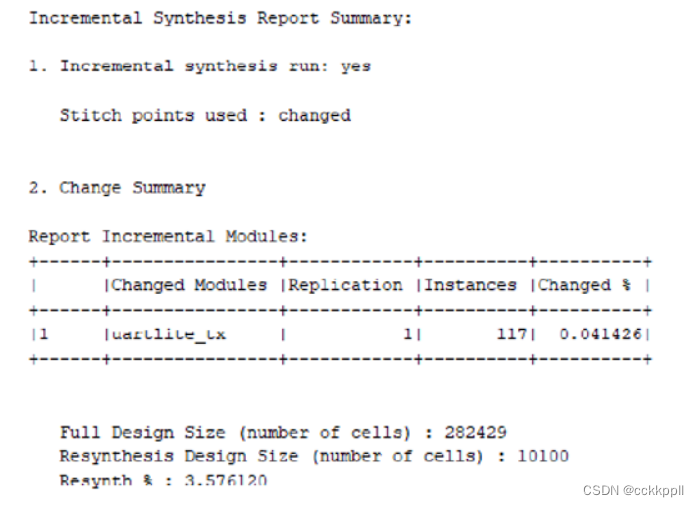

解释日志文件

执行参考运行时,该工具会在执行时对设计进行分区合成当增量运行开始时,它将详细的设计与参考运行并识别更改的模块。引用运行的分区是在增量运行中初始化。包含已更改模块的分区和标记受其影响的分区。基于此,该工具对标记的分区。关于设计的内容和设计的哪些部分的信息可以在增量运行后的日志文件中找到重新合成的。此信息在“增量综合报告摘要”中。以下是一个示例报告的一部分。

本节提供了设计中哪些部分发生了更改,需要重新合成的信息。此外,它还提供了设计与参考运行到增量运行。

重新综合整个设计

有些情况或类型的设计会导致流触发设计这些情况发生在以下条件下:

1.当对层次结构的顶层进行更改时

2.合成设置更改时

3.当小的设计包含很少的分区时

4.当超过50%的分区发生更改时

此外,异常大的XDC文件可能会触发整个设计的重新合成。这在未来版本。

注意:即使是合成设置,-mode out_of_context也不会触发完全的重新合成。

在Vivado中使用第三方合成工具IP

Vivado IP目录使用Vivado Design Suite进行设计、约束和验证合成

注意:即使这是一个合成设置,-mode out_of_context也不会触发完全的重新合成。大多数AMD提供的IP都有用IEEE P1735加密的HDL,并且不支持用于AMD IP的第三方合成工具。为了实例化在第三方合成工具内部使用Vivado IDE交付的AMD IP,建议采用以下流程:

1.在托管IP项目中创建IP自定义。

2.生成IP的输出产品,包括合成设计检查点(DCP)。Vivado IDE创建一个存根HDL文件,该文件在第三方合成工具中用于推断IP的黑匣子(_stub.v|_stub.vhd)。存根文件包含防止I/O缓冲区不会被推断;您可能需要修改这些文件以支持其他合成工具指令。

3.使用AMD IP的存根文件来综合设计。

4.使用第三方合成工具生成的网表和AMD IP的DCP文件,运行Vivado实现。有关更多信息,请参阅Vivado Design Suite用户指南:用IP(UG896)进行设计。

将进程移到后台

当Vivado IDE启动运行合成或实现的过程时对话框中,您可以将进程置于后台。当你把跑步放在在后台,它发布了Vivado IDE来执行其他功能,例如查看报告。

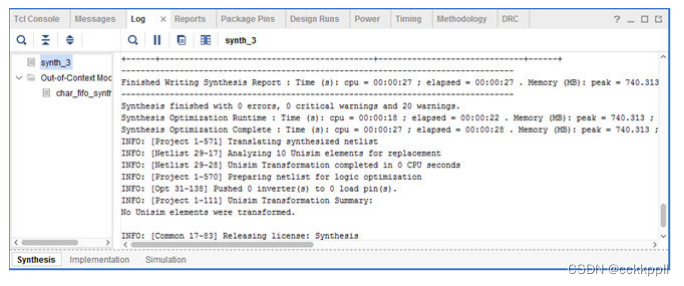

监控合成运行

从日志窗口监视合成运行的状态,如下图所示在合成期间显示在此窗口中的消息也是包含在合成日志文件。

这篇关于vivado 手动设置自下而上的流量并导入网表、创建较低级别的网表的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!