本文主要是介绍vivado HW_VIO,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

描述

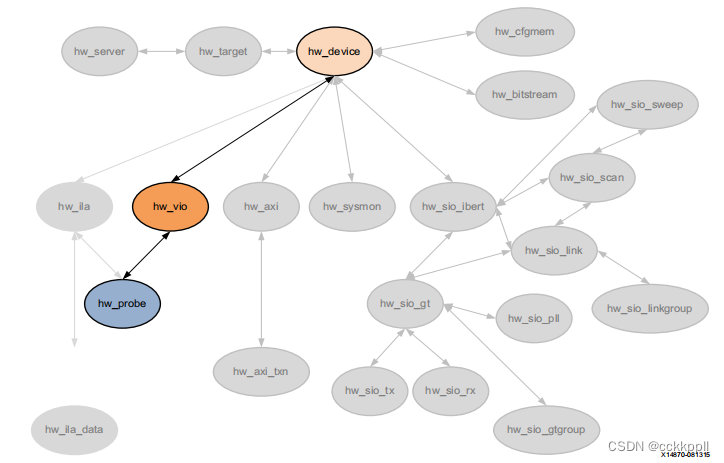

虚拟输入/输出(VIO)调试核心hw_VIO可以监视和驱动内部

在编程的XilinxFPGA上实时显示信号。在没有物理访问的情况下

目标硬件,可以使用此调试功能来驱动和监视

存在于物理设备上。

VIO核心具有硬件探测器hw_probe对象,用于监视和驱动特定信号

关于设计。输入探针监视作为VIO核心输入的信号。输出探针驱动

从VIO核心向指定值发送信号。探针上的值是使用定义的

set_property命令,并使用

commit_hw_vio命令。

VIO调试核心必须在来自XilinxIP目录的RTL代码中实例化。

因此,在调试之前,您需要知道要监视和驱动哪些网络

设计IP目录在Debug类别下提供了VIO核心。详细的

关于VIO核心的文档可以在虚拟输入/输出LogiCORE IP中找到

产品指南(PG159)【参考文献31】。

相关对象

VIO调试核心可以添加到XilinxIP目录中RTL源文件中的设计中。

使用get_Debug_cores可以在合成网表设计中找到调试核心

命令这些不是在中找到的硬件VIO调试核心对象hw_VIO

Vivado Design Suite的硬件管理器功能,尽管它们是相关的。

硬件VIO调试核心可以在编程的上的硬件管理器中找到

硬件设备对象hw_device。您可以查询hw_device的hw_vio,如下所示:

get_hw_vios-of[current_hw_device]

此外,hw_vio调试核心有与其关联的探针,也可以查询这些探针:

get_hw_probes-of[get_hw_vios]

属性

可以使用report_property命令报告指定给的特性

HW_VIO对象。请参阅Vivado Design Suite Tcl命令参考指南(UG835)

[参考文献13]了解更多信息。

这篇关于vivado HW_VIO的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!