本文主要是介绍vivado HW_ILA,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

HW_ILA

描述

集成逻辑分析器(ILA)调试核心允许您执行系统内监控

通过对内核上的调试探针,在实现的设计中对信号进行处理。您可以配置

ILA核心实时触发特定硬件事件,并在

以系统速度探测。

ILA调试核心可以通过从IP目录实例化ILA核心来添加到设计中

到RTL设计中,或者使用create_debug_core Tcl命令添加ILA核心

到合成的网表。请参阅Vivado Design Suite用户指南:编程和

调试(UG908)[参考文献23],了解有关在设计中添加ILA调试核心的更多信息。

根据设计生成比特流,并使用

program_hw_devices命令,可以从访问设计中的ILA调试核心

硬件管理器使用get_hw_ilas命令。分配给的调试探测器

可以使用get_ hw_。

ILA调试核心可以添加到RTL源文件中的设计中,或者使用

create_debug_core Tcl命令。调试核心可以在合成网表中找到

使用get_debug_cores命令进行设计。这些不是硬件ILA调试

Vivado Design Suite的硬件管理器功能中的核心对象hw_ila,

尽管它们是相关的。

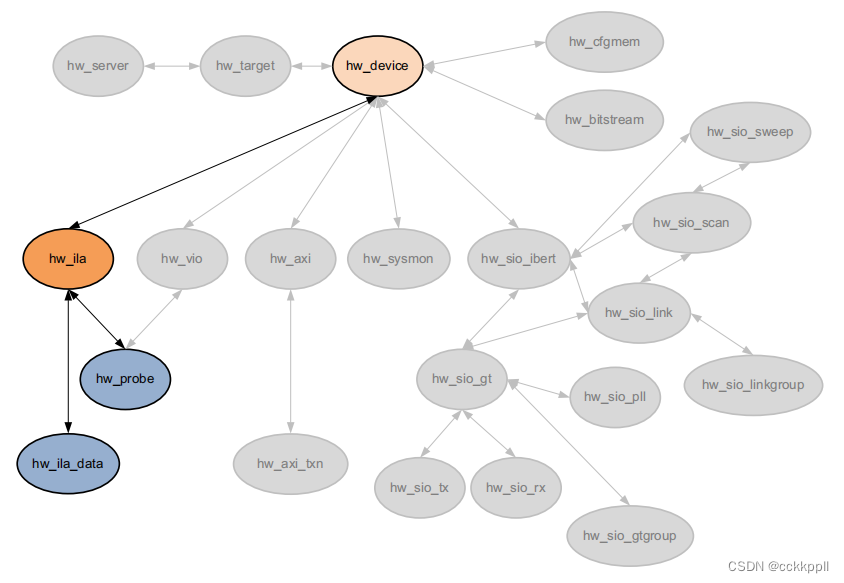

硬件ILA调试核心可以在编程的上的硬件管理器中找到

硬件设备对象hw_device。您可以查询hw_device的hw_ila,如下所示:

get_hw_ilas-of[current_hw_device]

还有一些与硬件ILA调试核心相关联的对象,例如硬件

探针以及从hw_ila核心捕获的数据样本。您可以查询对象

与ILA调试核心相关联,如下所示:

get_hw_ila_datas-of_objects[get_hw_idlas hw_ila_2]

属性

可以使用report_property命令报告指定给的实际特性

特定HW_ ILA。请参阅Vivado Design Suite Tcl命令参考指南(UG835)

[参考文献13]了解更多信息。

指定给HW_ILA对象的属性包括以下内容:

Property Type Read-only Visible Value

CLASS string true true hw_ila

CONTROL.CAPTURE_CONDITION enum false true AND

CONTROL.CAPTURE_MODE enum false true ALWAYS

CONTROL.DATA_DEPTH int false true 1024

CONTROL.IS_ILA_TO_DRIVE_TRIG_OUT_ENABLED bool true true 0

CONTROL.IS_TRIG_IN_TO_DRIVE_TRIG_OUT_ENABLED bool true true 0

CONTROL.IS_TRIG_IN_TO_ILA_ENABLED bool true true 0

CONTROL.TRIGGER_CONDITION string false true AND

CONTROL.TRIGGER_MODE enum false true BASIC_ONLY

CONTROL.TRIGGER_POSITION int false true 0

CONTROL.TRIG_OUT_MODE enum true true DISABLED

CONTROL.TSM_FILE string false true

CONTROL.WINDOW_COUNT int false true 1

CORE_REFRESH_RATE_MS int false true 500

HW_CORE string true false core_1

INSTANCE_NAME string true true u_ila_0

NAME string true true hw_ila_1

STATIC.IS_ADVANCED_TRIGGER_MODE_SUPPORTED bool true true 1

STATIC.IS_BASIC_CAPTURE_MODE_SUPPORTED bool true true 1

STATIC.IS_TRIG_IN_SUPPORTED bool true true 0

STATIC.IS_TRIG_OUT_SUPPORTED bool true true 0

STATIC.MAX_DATA_DEPTH int true true 1024

STATIC.TSM_COUNTER_0_WIDTH int true true 15

STATIC.TSM_COUNTER_1_WIDTH int true true 15

STATIC.TSM_COUNTER_2_WIDTH int true true 15

STATIC.TSM_COUNTER_3_WIDTH int true true 15

STATUS.CORE_STATUS string true true IDLE

STATUS.DATA_DEPTH int true true 2147483647

STATUS.IS_TRIGGER_AT_STARTUP bool true true 0

STATUS.SAMPLE_COUNT int true true 0

STATUS.TRIGGER_POSITION int true true 2147483647

STATUS.TSM_FLAG0 bool true true 1

STATUS.TSM_FLAG1 bool true true 1

STATUS.TSM_FLAG2 bool true true 1

STATUS.TSM_FLAG3 bool true true 1

STATUS.TSM_STATE int true true 0

STATUS.WINDOW_COUNT int true true 2147483647

TRIGGER_START_TIME_SECONDS string true true

TRIGGER_STOP_TIME_SECONDS string true true

要报告特定HW_ILA的属性,可以复制并粘贴以下内容

命令输入Vivado Design Suite Tcl shell或Tcl控制台:

report_property -all [lindex [get_hw_ilas] 0]

这篇关于vivado HW_ILA的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!