ila专题

microsoft微软excel或WPS表格打开vivado逻辑分析仪ILA保存的csv文件,自动转换科学计数法损失精度的bug

问题 vivado的逻辑分析仪ILA,可以方便的把数据导出成CSV(Comma-Separated Values)文件,实际是逗号作为分隔符的数据文件。 导出数据文件用文本编辑器打开,第74行有如下数据: 但是使用excel打开这个csv文件,则这个数据自动显示为科学计数法,但是值的最后一位已经从8变成0: 误差 这个值代表的双精度浮点数,误差-0.00000000000005

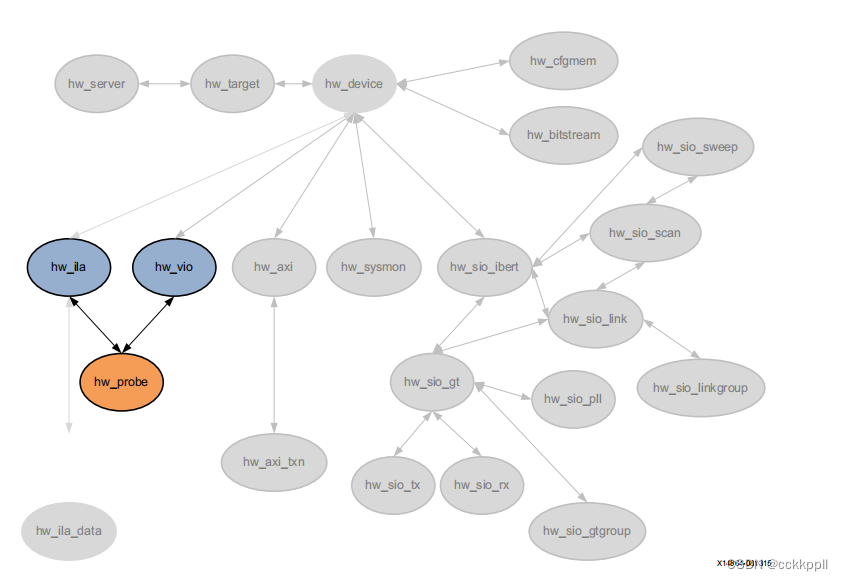

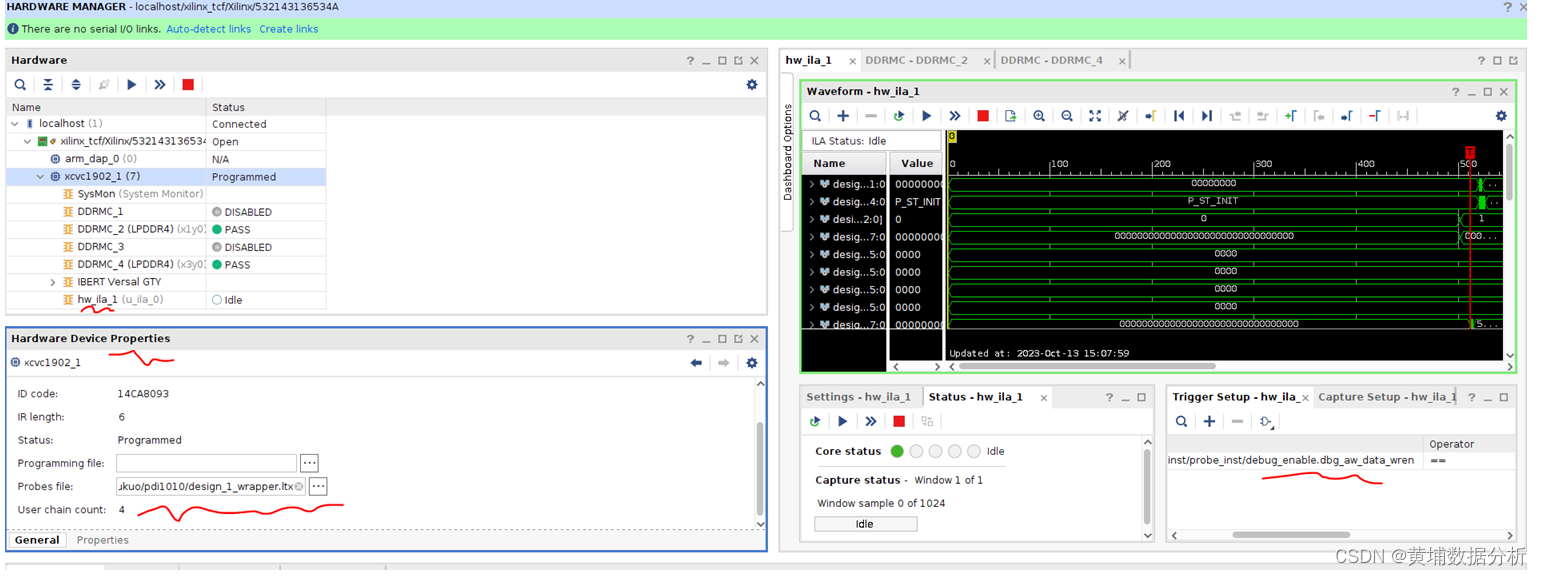

vivado HW_ILA_DATA、HW_PROBE

HW_ILA_DATA 描述 硬件ILA数据对象是ILA调试核心上捕获的数据的存储库 编程到当前硬件设备上。upload_hw_ila_data命令 在从ila调试移动捕获的数据的过程中创建hw_ila_data对象 核心,hw_ila,在物理FPGA上,hw_device。 read_hw_ila_data命令还可以在读取 来自磁盘的ILA数据文件。 hw_ila_data对象可以在Vivado

vivado HW_ILA

HW_ILA 描述 集成逻辑分析器(ILA)调试核心允许您执行系统内监控 通过对内核上的调试探针,在实现的设计中对信号进行处理。您可以配置 ILA核心实时触发特定硬件事件,并在 以系统速度探测。 ILA调试核心可以通过从IP目录实例化ILA核心来添加到设计中 到RTL设计中,或者使用create_debug_core Tcl命令添加ILA核心 到合成的网表。请参阅Vivado Design Sui

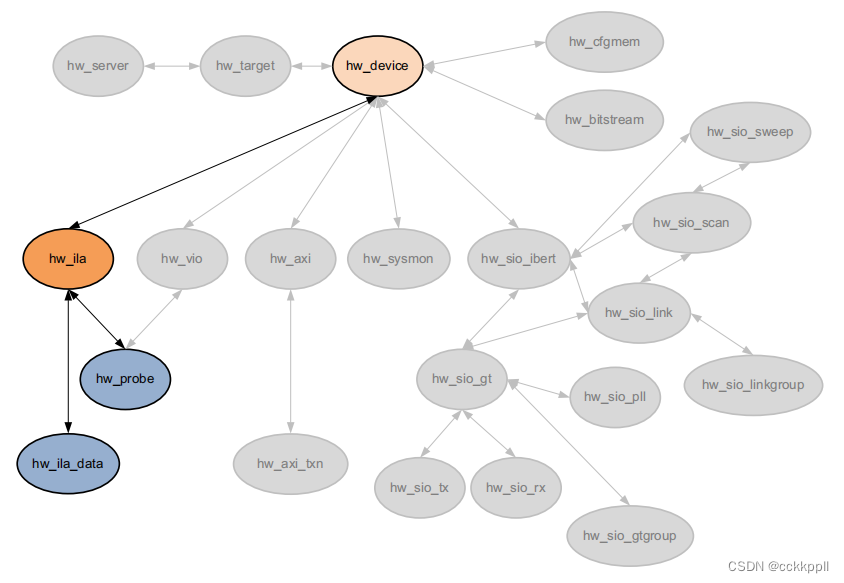

vivado 使用波形 ILA 触发器和导出功能

使用波形 ILA 触发器和导出功能 • 启用自动重新触发 : 选中“ Waveform ”窗口工具栏上的“启用自动重新触发 (Enable Auto Re-Trigger) ”按钮即可在 成功完成触发 + 上传 + 显示操作后 , 启用 Vivado IDE 以自动重新装备与“ Waveform ”窗口触发器关联的 ILA 核。 每次成功完成

无法触发vivado debug ila

1、更新硬件,重新编译,导出bit,更新SDK 编译后 运行run configuration调试,在vivado 中无法执行触发波形: 2、解决方法: 删除SDK 文件夹,重新创建

【vivado】ILA使用

一、ILA使用方法 使用ILA IP核或者在相应信号或者端口前添加(* mark_debug = "true" *)后实现相应波形观测。 二、一点感受 虽然ILA在一些情况下比较好用,但不建议靠ILA来debug。因为: 1) ILA分析的波形长度有限; 2) ILA抓取的信号数量有限; 3) 如果需要新加debug信号,需要重新做ILA,再Place&Route,费时费力; 4)I

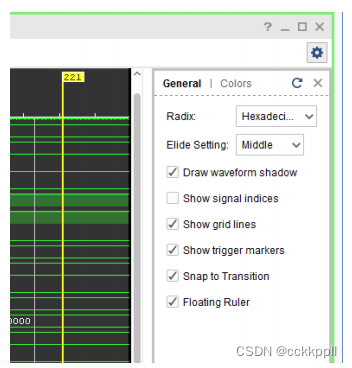

vivado加载ila波形文件

打开vivado的hardware manager界面,在命令行(tcl console)依次输入以下命令: 1、read_hw_ila_data + ila文件路径 2、display_hw_ila_data

ILA对时钟采样出现的问题

尽量让ILA采样同一个时钟的产物,不然会导致一些异常现象 比如用50MHz的时钟sys_clk采样48MHz的时钟cam_clk,cam_clk看起来会是2MHz,具体原分析如下 在下图1 中,clk2和clk1的频率比例为25:24,当使用clk2采样clk1时,会采到连续的低电平 见图2,连续的采到的低电平一直持续到clk2的第25个周期,然后是持续25个周期的高电平 总结:按照规范,

Vivado使用IP核创建ILA调试环境

创建ILA核 1.在IP核中找到ILA 2. General Options: 1.Monitor Type:ILA 探针接口类型设置。ILA 探针接口有两种类型,Native 与 AXI。Native 是普通接口模式;AXI 是 AXI 接口模式,用于调试 AXI 接口信号。Native 通常是用来测量电平或一定位宽信号,AXI 就比较明显了直接测量 AXI 总线的信号。这里主要测试 le

【FPGA教程案例68】硬件开发板调试8——通过ila在线调试DDS信号发生器

FPGA教程目录 MATLAB教程目录 -------------------------------------------------------------------------------------------------------------------------------- 本课程成果预览(通过ila在线监测正弦信号) 目录 1.软件版本 2.项目工程准备

Vivado中ILA显示信号不全的解决办法

在代码中加入了很多信号,但是下载程序后进入ILA界面时信号却显示不全。其实这不是代码的问题,信号有是有,只是没有添加进来。 点击加号把没有显示的信号添加进来就可以了。

[IP_Flow 19-3805] Failed to generate and synthesize debug IPs. u_ila_0_synth_1/u_ila_0.dcp“: no suc

vivado软件用ila调试时,提示缺少....dcp,我的解决办法如下: 在要观察的信号前添加(* mark_debug ="true" *),综合成功,set up debug成功, crtl + s保存到约束文件 实现后报错: 试了很多方法,1断开[IP_Flow 19-3805] Failed to generate and synthesize debug IPs.

添加ILA ip核以后编译会报[CRC RECP-1582] 借误

解决方法: 不能直接括双向10满口加到观原列限,会报懂,你可以播2c_h模决的sda_n,sd_d,sda_out三个信号分别进来观康

防止synplify优化ILA模块或信号

摘要:synplify综合的时候会优化掉没有用到的信号或者模块,为防止synplify优化ILA或信号特记录此方法; 我使用的是synplify_pro compile完成之后,可以打开synplify图形化的网表 1.防止synplify优化wire信号 在vivado里面一般可以用mark_debug解决 但是在synplify需要用 /*synthesis syn_

XILINX VIVADO 找不着ILA或者是[Common 17-162] Invalid option value specified for ‘-nets‘. 的解决办法

vivado经常时不时出现找不着ILA或者是报下在这种错误, 出现这种问题的原因是ILA更新了,但是约束没有自动更新,导致找不着dbg_hub的时钟,而这种时钟名是软件生成的,每次都不一样,可以在XDC文件中注释或删除掉dbg_hub的相约束。 然后implement下打开IO,再然后取消一个IO的锁定并重新勾上之后按CTRL+S保存,这时会生成新的约束,如下图,然后重新编译工程吧

![[IP_Flow 19-3805] Failed to generate and synthesize debug IPs. u_ila_0_synth_1/u_ila_0.dcp“: no suc](https://img-blog.csdnimg.cn/a59f1623953b4eb687e4951c22eda6b3.png)

![添加ILA ip核以后编译会报[CRC RECP-1582] 借误](https://img-blog.csdnimg.cn/direct/f6560e3bff8d4398a3ff065db3fec2fd.png)

![XILINX VIVADO 找不着ILA或者是[Common 17-162] Invalid option value specified for ‘-nets‘. 的解决办法](https://img-blog.csdnimg.cn/20200814195254424.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L1NoYXdnZQ==,size_16,color_FFFFFF,t_70)