本文主要是介绍Xilinx RFSOC 47DR 8收8发 信号处理板卡,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

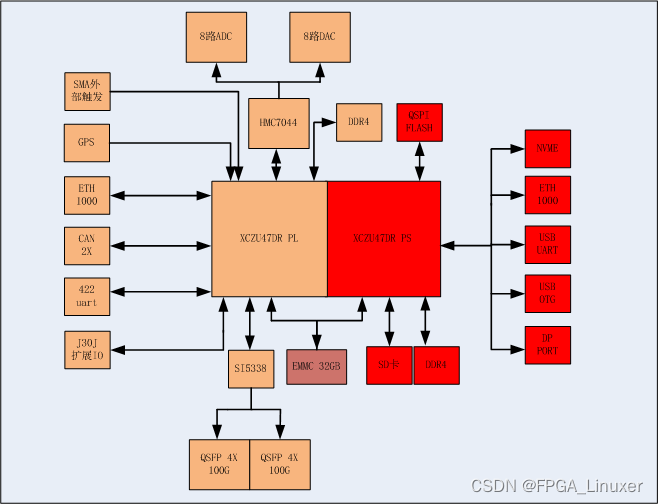

系统资源如图所示:

FPGA采用XCZU47DR 1156芯片,PS端搭载一组64Bit DDR4,容量为4GB,最高支持速率:2400MT/s;

PS端挂载两片QSPI X4 FLASH;

PS支持一路NVME存储;

PS端挂载SD接口,用于存储程序;

PS端或者PL端可选挂载一片EMMC芯片,可用于存储程序或者PL直接逻辑访问(跳线可选);

PS端外接一路USB3.0接口;

PS端支持一路千兆网口;

PS端支持一路UART(转接成USB接口);

PL端搭载一组32Bit DDR4,容量为2GB,最高支持速率:2400MT/s;

PL端挂载两路4X QSFP+接口,最大支持16*4Gbps;

PL端挂载一路uart 422接口;

PL端预留部分IO,用于用户扩展;

PL端支持两对Can收发接口;

PL支持一路GPS;

PL支持一片加密芯片;

这篇关于Xilinx RFSOC 47DR 8收8发 信号处理板卡的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-30 RS485串口程序收发环路设计](https://i-blog.csdnimg.cn/direct/320b5c48ecbf46a2b876f556cbe213e5.png)