47dr专题

TQRFSOC开发板47DR ADC输入采集测试(二)

本章内容将介绍如何使用RFSOC 47DR 进行ADC输入采样测试,我们这边提供三个ADC输入采样的python程序,实现8路通道的ADC采样解析数据,并且在时域与频域上显示出示波器与频谱仪的效果。 进入我们提供的47dr_python文件夹。以py后缀的文件一共有四个,其中的一共名为init.py 的文件在上一章节中使用过,是初始化开发板的程序。其他三个是不同的测

TQRFSOC开发板47DR LWIP自环测试

本例程基于RFSOC 47DR开发板实现LWIP自环通讯测试。使用开发板的网口与电脑或路由器等设备连接,使开发板与电脑在同一局域网内,使用telnet工具连接开发板,进行LWIP自环测试。 LWIP自环测试工程在Hello World项目上进行修改,首先打开vivado,修改设计文件中的ZYNQ核的配置。LWIP除了用到网口还需要用到定时器,双击ZYNQ核-->添加

TQRFSOC开发板47DR,LMK04832更新配置

在利用RFSOC开发板进行项目开发时,面对多样化的时钟需求,巧妙地配置LMK04832时钟管理芯片以输出精确的时钟信号显得尤为重要。本期内容将讲解如何通过ZYNQ更新LMK04832的配置,以满足您的特定时钟需求。 每次配置成功后,配置文件都会存储到EEPROM中,掉电开机后自动获取EEPROM中的配置。 使用TICS Pro软件设置好需要的配置后,

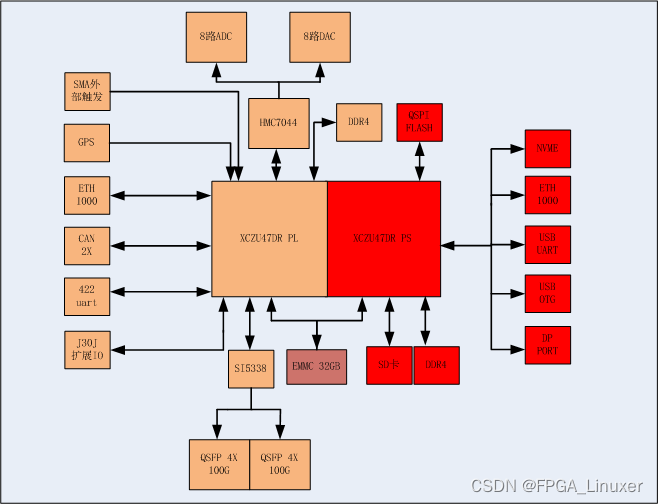

Xilinx RFSOC 47DR 8收8发 信号处理板卡

系统资源如图所示: FPGA采用XCZU47DR 1156芯片,PS端搭载一组64Bit DDR4,容量为4GB,最高支持速率:2400MT/s; PS端挂载两片QSPI X4 FLASH; PS支持一路NVME存储; PS端挂载SD接口,用于存储程序; PS端或者PL端可选挂载一片EMMC芯片,可用于存储程序或者PL直接逻辑访问(跳线可选); PS端外接一路USB3.0