走线专题

电路笔记(PCB):JLC PCB布局和走线基础教程笔记

对立创EDA 四层板PCB设计保姆级教程的笔记看完才发现是个虚假的教程,除了没教四层板咋画其它教了(中间的两层全是GND的作用) 文章目录 PCB布局转换原理图布局传递 板框布局确定锁定功能布局调整工具 调整器件位置**alt+B**放置到底层网络中隐藏GND飞线使用不同颜色标注网络 对PCB设计规则进行设置,选择四层板设计,将铜箔层改为四计算线宽在设计规则将间距设置为6mil在设计规则将

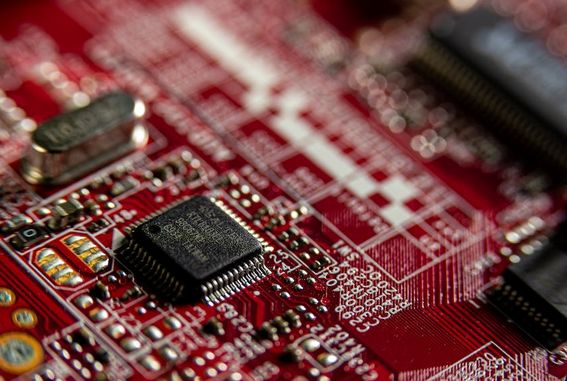

PCB 走线注意事项

PCB 走线注意事项 引言正文 引言 PCB 英文全称 Printed circuit board,中文翻译为印刷电路板。 正文 PCB 板不能直角走线。 直角走线会使传输线的线宽发生变化,造成阻抗的不连续,会引起待高频信号本身的反射,信号在 PCB 中传输会有延迟。如果时序没有匹配,系统就会罢工,同时 90 度拐角处还会产生寄生电容,寄生电感和尖端 EMI,从而影响信号。

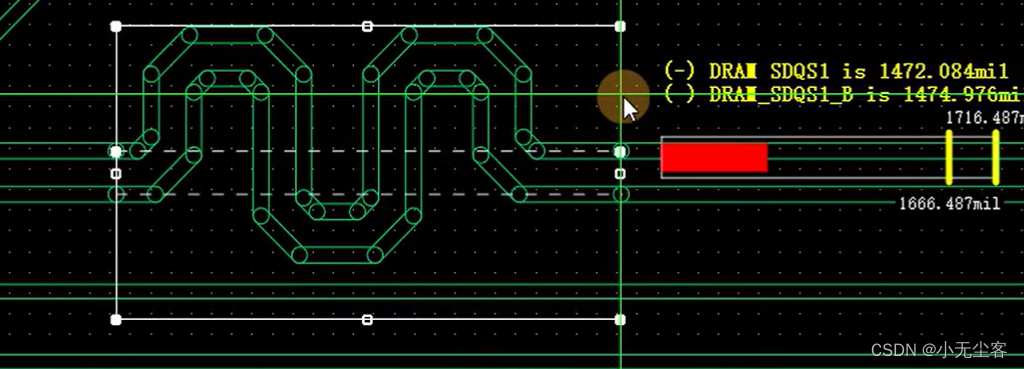

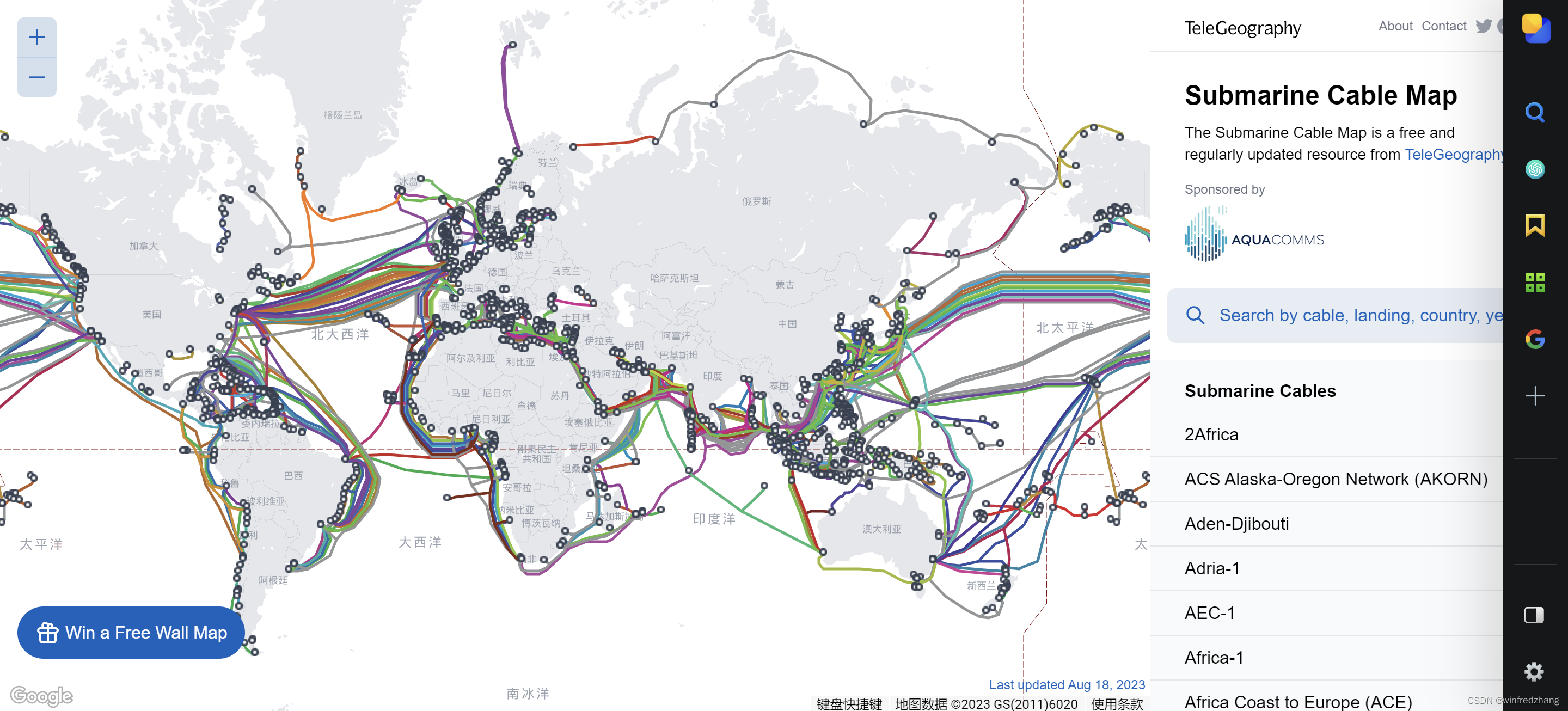

Marin说PCB之如何在主板上补偿链路中的走线的等长误差?

一场雨把我困在这里,你冷漠地看我没有穿雨衣淋成落汤鸡。今天刚刚出门时候看天气预报没有雨,于是我就没有带雨衣骑电动车去公司了,谁知道回来的路上被淋成狗了。天气预报就像是女人的脾气那样,不能完全相信的。 好了,我们言归正传了,这期文章是给大家分享一下我之前设计的一个单板上如何在主板上补偿MIPI走线的等长误差值,各位帖子们打起精神来了,下面就是本期的内容解析了。 小编我之前做的一个单板是主板,

深度论证-高速走线控制100欧姆阻抗一定是最好的选择吗?

高速先生成员--黄刚 对于高速差分信号到底需要控制多少欧姆的阻抗,高速先生相信大部分工程师首先都会看下例如信号的协议文档或者芯片的文档,看看里面有没有推荐的控制阻抗值。例如像PCIE信号,在4.0之后的阻抗会明确要求按照85欧姆来控制,USB阻抗会要求控制90欧姆等。除了这一部分有明确的阻抗要求外,其他没明确要求的高速信号你们会控多少欧姆阻抗呢?就好像为什么PCB的单端走线要控制50欧姆一样

【转】USB2.0走线要点

USB通用串行总线(Universal Serial Bus),目前我们所说的USB一般都是指USB2.0,USB2.0接口是目前许多高速数据传输设备的首选接口,从1.1过渡到2.O,作为其重要指标的设备传输速度,从1.5Mbps的低速和12Mbps的全速提高到如今的480Mbps的高速。USB的特点不用多说大家也知道就是:速度快、功耗低、支持即插即用、使用安装方便。正是因为其以上优点现在很多视

嵌入式硬件中PCB走线与过孔的电流承载能力分析

简介 使用FR4敷铜板PCBA上各个器件之间的电气连接是通过其各层敷着的铜箔走线和过孔来实现的。 由于不同产品、不同模块电流大小不同,为实现各个功能,设计人员需要知道所设计的走线和过孔能否承载相应的电流,以实现产品的功能,防止过流时产品烧毁。 文中介绍设计和测试FR4敷铜板上走线和过孔的电流承载能力的方案和测试结果,其测试结果可以为设计人员在今后的设计中提供一定的借鉴

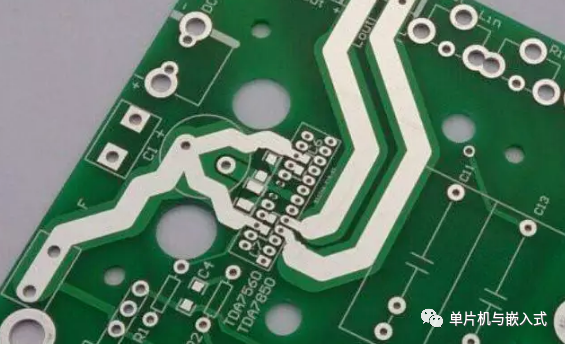

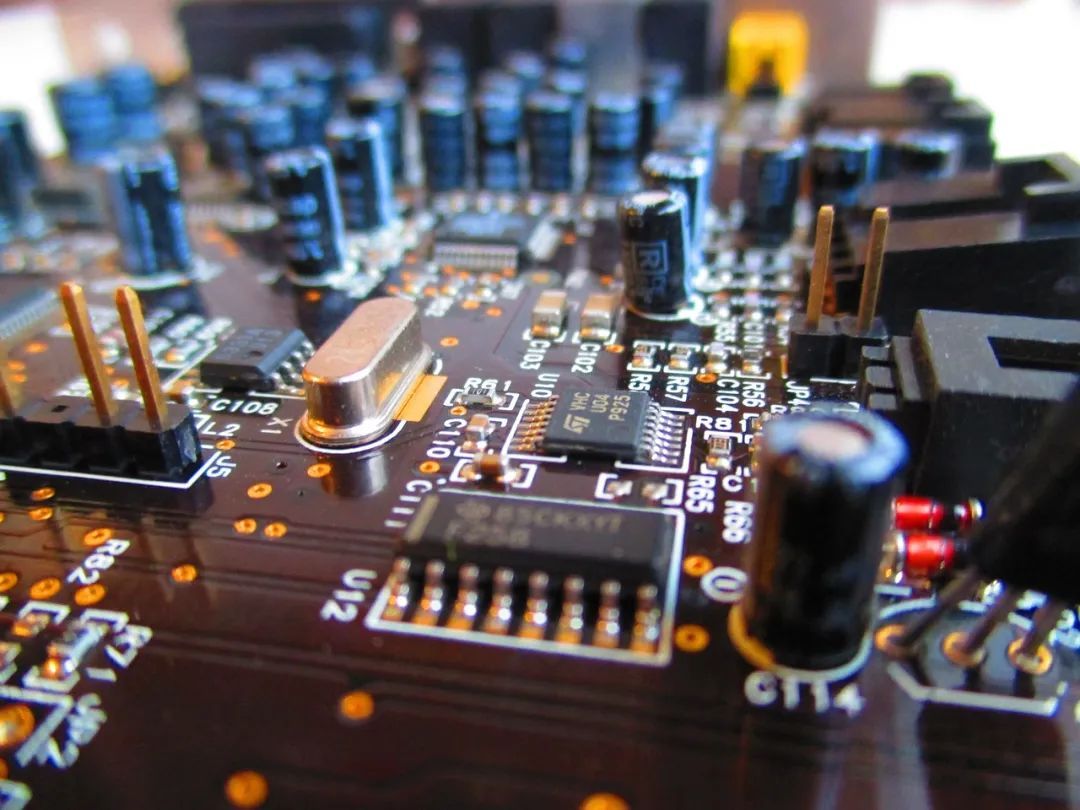

逆向学习技术!拆解驱动器,学习布局走线技术

微信关注 “DLGG创客DIY” 设为“星标”,重磅干货,第一时间送达。 下边公众号的UP主维修一个驱动器,里面有好多可以参考的地方。分享给大家一起学习 1.板与板的链接方式,稳定便宜性价比高2.多层板顶底层走线设计3.快查头防呆并预留副插4.接口的保护处理5.模块化设计 你点的每个在看,我都当成喜欢

PCB三大走线,如何高效率检查?

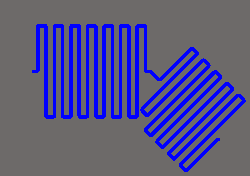

在PCB设计中,走线的布局与检查是至关重要的环节。按照走线类型,可分为直角走线、差分走线及蛇形线,如何针对这三种走线方式进行高效率检查,去也报电路的稳定性和可靠性? 1、直角走线 容性负载:观察直角拐角处是否造成传输线上的容性负载增加,进而影响信号的上升时间。阻抗连续性:检查直角走线是否导致阻抗不连续,进而产生信号反射,影响信号完整性。EMI辐射:对于高频设计,特别注意直角尖端可能

PCB走线时的注意事项

一般规则 1.1 PCB板上预划分数字、模拟、DAA信号布线区域。 1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。 1.3 高速数字信号走线尽量短。 1.4 敏感模拟信号走线尽量短。 1.5 合理分配电源和地。 1.6 DGND、AGND、实地分开。 1.7 电源及临界信号走线使用宽线。 1.8 数字电路放置於并行总线/串行DTE接口附近,DAA电路放置於电话

Altium Designer 差分走线出现网格

Altium Designer 差分走线出现网格 使用Altium Designer布线时,差分走线上出现致密的网格,如下图所示: 经查是因为设置的差分线的最大或最小间距不合适所致,修改后即恢复正常。如下图所示:

高功率电源PCB设计中变压器底层走线的关键要点

高功率电源的设计中,变压器起到了电能的传递与转换的重要作用。变压器下方的走线设计不仅涉及到电路的功率传输效率,还与电磁兼容性(EMC)、热管理以及电路的可靠性密切相关。 1. 走线布局 在进行变压器下方走线设计时,合理的走线布局是关键。应该避免在变压器下方设置过多的信号线,以减少互感干扰。同时,高功率电源的走线应该尽量短而直,减小电阻,提高效率。 2. 地线设计 合理的地线

【原创分享】高功率电源PCB设计中变压器下方走线的关键技巧

高功率电源的设计中,变压器起到了电能的传递与转换的重要作用。变压器下方的走线设计不仅涉及到电路的功率传输效率,还与电磁兼容性(EMC)、热管理以及电路的可靠性密切相关。 1. 走线布局 在进行变压器下方走线设计时,合理的走线布局是关键。应该避免在变压器下方设置过多的信号线,以减少互感干扰。同时,高功率电源的走线应该尽量短而直,减小电阻,提高效率。 2. 地线设计 合理的地线设计是电

Allegro PCB Design GXL (legacy) 使用slide推挤走线,走线的宽度就发生改变的原因

Allegro PCB Design GXL (legacy) version 16.6-2015 使用slide推挤走线,走线的宽度就会发生改变。 后来发现是因为约束管理器(Constraint Manager)中设置了最大线宽(Max Line Width)。 把最大线宽改为0,再推挤走线,走线的宽度就不会发生改变了。

Allegro-群组走线

一根一根走线嫌慢? 那就多根线一起走 解决方案: 单击 Add Connect 图标 如果几个走线是相邻的 可以直接框选 如果不相邻 右键 选择 Temp Group 依次点击想要同时走线的焊盘 选择完后 右键 选择Complete 选中的网络同时拉出 还可以设置各个走线之间的线距 更换主控制线 转换为单线模式 设置线间距 走线过程中 右键 选择Ro

AltiumDesigner画图不求人15 多条线路同时走线方法

原文地址:https://mp.weixin.qq.com/s/i4zKZ5BKBNA-UTlMHMviQQ 往期技术文章:https://mp.weixin.qq.com/s/KU9g0EMcjX42cFTV_niKJw

AD Altium Designer查看走线 布线长度方法

说明:以下为个人使用经验总结的记录,不对由此造成任何风险承担责任。 AD Altium Designer查看走线 布线长度方法-实用快捷键如下: STEP1: S-P 选中需要测量走线,适用于直线、斜线、蛇形线E-S-T 只能选中一线段 STEP2: R-S 弹出显示选中线条的长度

Altium中PCB上走线镀锡的方法

Altium中PCB上走线镀锡的方法 PCB设计时,有时候需要在不增加PCB走线宽度的情况下提高该走线通过大电流的能力(载流能力),通常的方法是给该导线镀锡(或者上锡);下面以在PCB顶层走线镀锡为例,使用AD09软件,简单介绍如何走线上锡处理: 1、 选择TopLayer层,确定需要走线的地方,画一条导线; 2.然后选择TopSolder层,如果软件没有显示TopSolder层,按快键键L打

PCB走线开窗上锡如何实现

俗称开天窗,举个例子,像下图中的Micro USB,它本身的封装引出的引脚非常的短,手工焊接的话非常不好焊接,需要将引脚拉长些,更方便焊接,也就是打板子的时候去掉那层绿色的油层,让走线光着露出来,既方便添加焊锡增加走线宽度,也适合手工焊接,下面是如何实现的例子(基于altium designer) 1、 如何在DXP中去掉个别线的绿油呢? 方法如下: A、 在top layer(或botto

HSMC接口简介(上)_HSMC接口用途_HSMC接口外观图_三视图_HSMC接口电压_HSMC接口电气特性_HSMC接口走线长度规则

做设计时需要获取HSMC的具体接口定义,CSDN等网站暂时没有结果,作者在Altera官网(现为Intel FPGA官网)搜索HSMC,获取了HSMC_spec(ification).pdf,现分享我之所得: pdf下载地址:https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ds/hsmc_spe

AD(Altium Designer)/DXP蛇形走线

使用环境(蓝色粗体字为特别注意内容) 1、软件环境:Win7 32 bit,AD(Altium Designer) 10.39. 准确来讲有两种走线方式,这里仅介绍比较方便的一种 直接蛇形线布线 布好线之后再进行蛇形走线受限于板子已经布好的各种线条的影响,在前行布线的过程也要考虑走线要宽松才能进行后期的蛇形走线调整。有一定的不便。在AD中不仅能在布线完成后再进行蛇形线调整,也可以在布线中直接

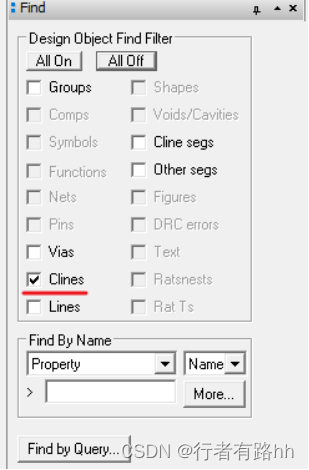

Allegro批量剪断走线操作

在用Allegro设计 PCB过程中,有时候由于原理图改动,导致布局的改动。这就会导致走完的线要重新走,对于差分对因为前半部分的走线是不用重新走的。那就可以使用剪断后面部分的线,然后删除,提高走线的效率。那如何批量剪断走线呢? (1)选择菜单Manufacture→Drafting→Delete by Rectangle(按矩形删除) (2)Find选项卡只选择Clines

PCB 设计时铜箔厚度,走线宽度和电流的关系

不同厚度不同宽度的铜箔的载流量见下表: 铜皮厚度 35um 铜皮厚度 50um 铜皮厚度 70um 铜皮 t=10 铜皮 t=10 铜皮 t=10 注 1 用铜皮作导线通过大电流时铜箔宽度的载流量应参考表中的数值 降额 50%去选择考虑 再看看摘自>(国防工业出版社, 毛楠孙瑛 96.1 第一版)的经验 公式, 以下原文摘录: “由于敷铜板铜箔厚度有限,在