缓冲器专题

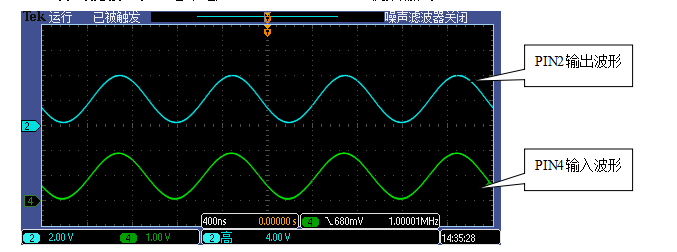

Xilinx FPGA 原语解析(二):IBUFDS差分输入缓冲器(示例源码及仿真)

目录 前言: 一、原语使用说明 二、原语实例化代码模版 三、使用示例 1.设计文件代码 2.仿真文件代码 3.仿真结果 前言: 本文主要参考资料xilinx手册,《Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for HDL Designs》UG768 (v14.7) Octob

MicroBlaze IP核中的外设接口和缓冲器接口介绍

MicroBlaze IP核是Xilinx公司提供的一个嵌入式软核处理器,广泛应用于FPGA设计中。在MicroBlaze IP核中,外设接口和缓冲器接口是处理器与外部设备和内存交互的关键部分。 1 外设接口 MicroBlaze处理器中的AXI4 内存映射外设接口AXI4是一种在Xilinx FPGA设计中常见的通信协议,用于在处理器和内存或其他外设之间传输数据。 指令外设接口(M_AXI_

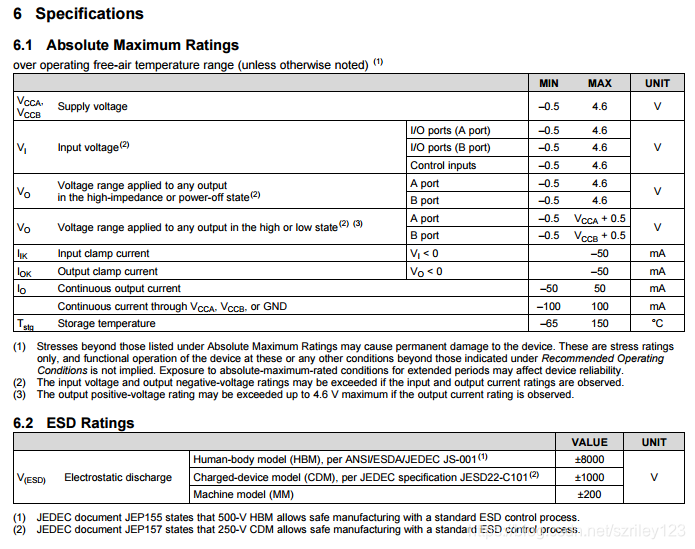

AiP74LVC1T45GB236.TR SOT23-6缓冲器/驱动器双电源接口电平转换

AIP74LVC1T45GB236.TR 是一款电平转换芯片,它的应用领域非常广泛,主要包括: 1. 嵌入式系统:在嵌入式系统中,由于不同的外设可能工作在不同的电源电压下,该电平转换器可用于确保微控制器和其他逻辑电路之间的信号传输正确无误。 2. 汽车电子:汽车电子系统经常需要处理来自不同电源域的信号,AIP74LVC1T45GB236.TR 可用于汽车电子设备中以保证稳定的数据通信。

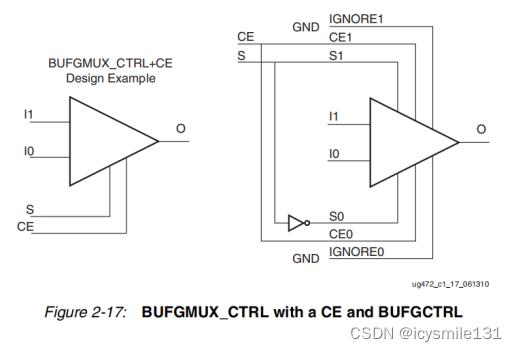

Xilinx 7系列FPGA全局时钟缓冲器基本单元

Global Clock Buffer Primitives(全局时钟缓冲器基本单元)在FPGA(现场可编程门阵列)和其他数字系统中扮演着至关重要的角色。这些基本单元被设计用于处理、分配和增强时钟信号,以确保系统中的各个组件都能以精确和同步的方式工作。 表2-2中的基本单元代表了全局时钟缓冲器的不同配置。 1. BUFGCTRL BUFGCTRL基本单元如图2-3所示,可以在两个异步时钟之间

【电路笔记】-数字缓冲器

数字缓冲器 文章目录 数字缓冲器1、概述2、单输入数字缓冲器3、三态缓冲器3.1 有效“高”三态缓冲器3.2 有效“高”反相三态缓冲器3.3 有效“低”三态缓冲器3.4 有效“低”反相三态缓冲器 4、三态缓冲器控制 数字缓冲器和三态缓冲器可以在数字电路中提供电流放大以驱动输出负载。 1、概述 数字缓冲器是与反相器(非门)相反的逻辑门,我们在上一篇教程中看到非门输出状态是其

单通道 6 阶高清视频滤波驱动电路芯片D1675,一款高清视频信号译码、编码的滤波器和缓冲器

1、概述: D1675单电源工作电压为+2.5V到+5V,是一款高清视频信号译码、编码的滤波器和缓冲器。与使用分立元件的传统设计相比,D1675更能节省PCB 板面积,并降低成本以及提高视频信号性能。D1675集成了一个直流耦合输入缓冲器、一个消除带外噪声的视频编码器和一个增益为+6dB可驱动75Ω负载的运放驱动。交流或直流耦合输入缓冲器消除同步挤压、弯曲和场倾斜。D1675的输出也可

ADC32RF80IRMPT功能特点、AD8418WBRZ放大器和ADCLK846BCPZ时钟缓冲器概述

ADC32RF80IRMPT 是一款14位、3-GSPS双通道电信接收机和反馈器件系列,支持输入频率高达4 GHz及以上的射频采样。ADC32RF8x系列专为高信噪比(SNR)而设计,可在大输入频率范围内提供-155 dBFS/Hz的噪声频谱密度以及动态范围和通道隔离。带片上终端的缓冲模拟输入在宽频率范围内提供均匀的输入阻抗,并最大限度地减少采样和保持故障能量。 应用—— 多载波GSM蜂窝基础设

SI53340-B-GM时钟缓冲器2304NZLPGGI8特征、STM8AF52A9TCY汽车微控制器

SI53340-B-GM时钟缓冲器说明 SI53340 LVDS扇出时钟缓冲区为时钟/数据分布和冗余时钟应用进行了优化。Si53340 缓冲器提供典型的50fs的超低抖动,并在宽直流至1250MHz频率范围内工作。这些器件具有最小的串扰,并提供优越的电源噪声抑制,简化了噪声环境中的低抖动时钟分布。独立的核心和输出银行供应引脚提供集成的电平转换,而不需要外部电路。 Si53340缓冲器有多种配置可

SN74AHCT541PWR缓冲器 非反向1Element 8 Bit per Element 三态 Output 20-TSSOP

SN74AHCT541PWR 工作范围2 V至5.5 V VCC 闩锁性能超过250 mA JESD 描述/订购信息 AHC541八进制缓冲器/驱动器非常适合驱动总线或缓冲存储器地址寄存器。 这些设备具有输入和 包裹两侧的输出到便于印刷电路板布局。 三态控制门是双输入AND门具有低电平有效输入,如果有的话输出使能(OE1或OE2)输入为高电平 相应的输出处于高阻态州。 输出时提供非反转数据它们

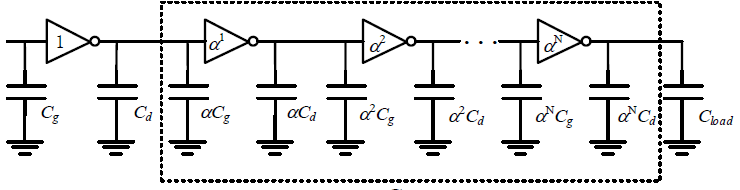

数字CMOS集成电路——超级缓冲器设计

超级缓冲器设计 超级缓冲器示意图 超级缓冲器——驱动大电容、减少传输延迟时间 # Cload = 50 # 负载电容/pF# Ci = Cg = 5 / 1000 # 等效反相器(第一级)的输入电容(栅极电容)/pF# tp0 = 35 # 第一级反相器的本征延时/ps,无负载的情况下的延迟# tp_inv = 70 # 环形振荡器单级的延迟时间/ps,

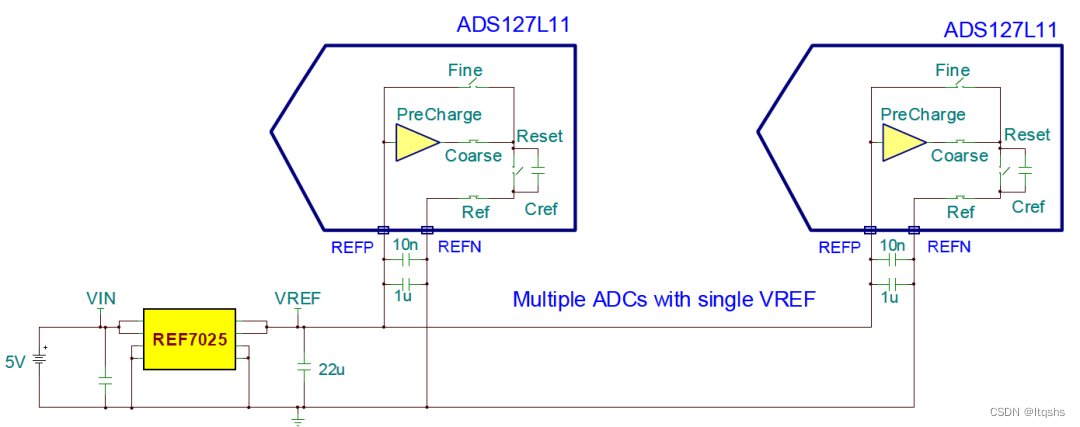

充分理解ADC预充电缓冲器的重要性-运放缓存

新型高性能模数转换器(ADC)设计师的目标之一是放宽对外部输入放大器和基准的设计要求,他们的通常做法是内置针对模拟和基准输入的集成式缓冲器。然而,对于高性能ADC而言,在信号链中添加任何元件都会降低整体性能。 设计优先事项包括优选硅工艺、电路精心设计以及良好的布局和IC封装,以优化电压偏移、增益、信噪比(SNR)和总谐波失真(THD)等诸多指标。添加传统的缓冲器会影响这些指标,而且很多时候,这些

(五)基于Multisim的电台发射系统:缓冲器的设计

(五)基于Multisim的电台发射系统 写在前面系统要求基本原理振荡器的设计振幅调制器的设计高频功率放大器的设计低频功率放大器的设计缓冲器的设计目的Multisim电路图及分析仿真结果 写在前面 1.本系列分为五篇,包括(一)振荡器的设计、(二)振幅调制器的设计、(三)高频功率放大器的设计、(四)低频功率放大器的设计和(五)缓冲器的设计,使用的软件均为Multisim14。

锁存器、触发器、寄存器和缓冲器的区别

一、锁存器 锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。 锁存器不同于触发器,它不在锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。锁存器也称为透明锁

同步缓冲器设计(Synchronous FIFO)

缓冲器又称为队列,是一种数据暂存的机制。缓冲器存在的必要是因为当数据传出端传出数据时,接收端不一定能实时地接收,如果接收端不能实时地接收,又无缓冲器的存在,数据将不可避免会遗失。如果输出输入端的时钟频率一致,称之为同步缓冲器,如果输出输入端的时钟频率不一致,称之为异步缓冲器。缓冲器能存储的数据个数,称之为其深度,每一个数据有多少位数,称之为其宽度。在使用缓冲器时必须了解,如果输入端不断地将数据写入

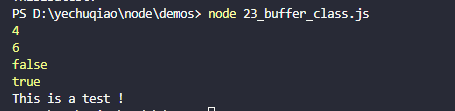

Node3-2基础API----Buffer(缓冲器)

Buffer(缓冲器) Buffer是用于处理二进制数据流的实例类似整数数组,大小固定(实例化之后,是多大就多大,不能进行变更)C++代码在V8 对外分配物理内存Buffer是全局变量,没必要使用require来引用 //常见一个规定长度,默认用0填充console.log(Buffer.alloc(10));console.log(Buffer.alloc(20));// 用2填充

NodeJS3-2基础API----Buffer(缓冲器)

Buffer(缓冲器) Buffer是用于处理二进制数据流的实例类似整数数组,大小固定(实例化之后,是多大就多大,不能进行变更)C++代码在V8 对外分配物理内存Buffer是全局变量,没必要使用require来引用 //常见一个规定长度,默认用0填充console.log(Buffer.alloc(10));console.log(Buffer.alloc(20));// 用2填充c

【玩转Node.JS】=> 之 Buffer(缓冲器)

Node.js® 是一个开源、跨平台的 JavaScript 运行时环境 文章目录 Buffer 概念Buffer 的特点创建 BufferBuffer 与字符串的转化 Buffer 的读写 Buffer 概念 Buffer 是一个类似于数组的 对象 ,用于表示固定长度的字节序列Buffer 本质是一段内存空间,专门用来处理 二进制数据 Buffer 的特

Node.js之Buffer(缓冲器)

Buffer的概念 Buffer 是一个类似于数组的 对象,用于表示固定长度的字节序列 Bufer 本质是一段内存空间,专门用来处理 二进制数据。 Buffer创建方法 // 1.alloclet buf1 = Buffer.alloc(10)// 使用alloc创造buffer的方法 是一个二进制类 都会归零console.log(buf1) //<Buffer 00 00 00 00

RTOS流和消息缓冲器

RTOS流和消息缓冲器 [ 任务间通信和同步 ] 可从FreeRTOS V10.0.0获得 介绍 流缓冲区是 RTOS任务 的RTOS任务,并且是任务通信原语的中断。与大多数其他FreeRTOS通信原语不同的是,它们针对单读卡器单写入器方案进行了优化,例如将数据从中断服务例程传递到任务,或从双核CPU上的一个微控制器核心传递到另一个微控制器核心。数据通过复制传递 - 数据由

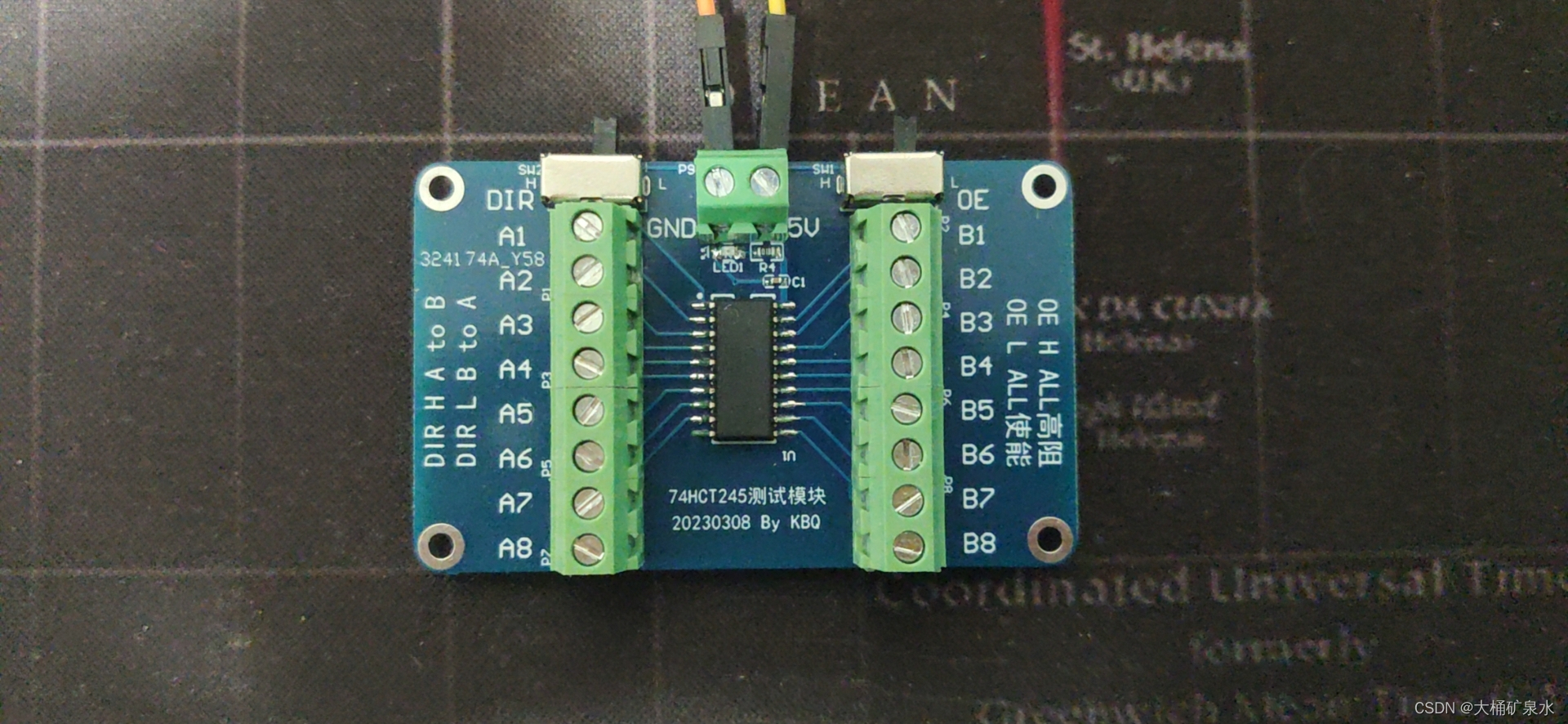

缓冲器/驱动器/收发器IC

一、前言 记录学习未使用过的IC,开发使用新的IC,哎,就是玩 本编文章主要介绍缓冲器/驱动器/收发器 目录 一、前言二、环境三、正文1.SN74HCT245NSR2. 四、结语 二、环境 FPGA或MCU低驱动能力引脚 单向长距离信号 三、正文 1.SN74HCT245NSR DIR高电平,A到B可控制,B到A不可控制 DIR低电平,B到A可控制,A到B不可控制